高动态范围ADC:逐次逼近型抑或Σ-Δ型?

时间:12-15

来源:互联网

点击:

工业、仪器仪表和医疗设备中使用的高性能数据采集信号链需要宽动态范围和高精度。 通过增加可编程增益放大器,或者并联使用多个ADC,然后利用数字后处理对结果进行平均,可以提高ADC的动态范围,但受制于功耗、空间和成本,这些方法可能不切实际。 过采样技术不仅能让ADC以低成本实现高动态范围,而且解决了空间、热和功耗设计方面的难题。

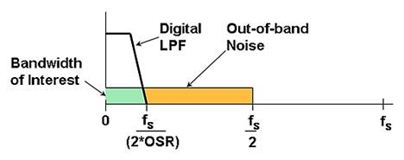

过采样是以大幅高于奈奎斯特速率(两倍信号带宽)的速率对输入信号进行采样,从而提升信噪比(SNR)和有效位数(ENOB)。 当ADC过采样时,量化噪声会扩展,使其大部分出现在目标带宽以外,从而增加较低频率下的整体动态范围。 利用数字后处理可以消除目标带宽之外的噪声,如图1所示。 过采样比(OSR)等于采样速率除以奈奎斯特速率。 过采样引起的动态范围增加量(ΔDR)可计算如下:ΔDR = log2(OSR) × 3 dB。 例如,对ADC进行4倍过采样可增加6 dB的动态范围或多提供1位分辨率。

图1 . 奈奎斯特ADC过采样

多数集成数字滤波器的Σ-Δ型ADC原本就可以实现过采样特性,调制器时钟速率通常是信号带宽的32到256倍,但对于需要快速切换输入通道的应用,可用的Σ-Δ型ADC很有限。 SAR型架构没有延时或流水线延迟,支持高速控制环路和输入通道快速切换,并且其高吞吐速率也允许过采样。

虽然这两种ADC拓扑结构都能精确地测量低频信号,但SAR型ADC的功耗与吞吐速率成正比,而Σ-Δ型ADC的功耗通常是固定的,相比之下,前者的功耗至少要低50%。 ADI公司的5 MSPS、18位SAR型ADC AD7960就是一个例子,它具有高吞吐速率和线性功耗变化特性。

放置在SAR型ADC之前的低通滤波器可使混叠最小,并能通过限制带宽来降低噪声。 Σ-Δ型ADC的高过采样比和数字滤波器可最大程度地降低其模拟输入端的抗混叠要求,过采样则能降低整体噪声。 为了提高灵活性,FPGA上也可以执行定制数字滤波。

高性能SAR型ADC的低噪底和高线性度使其能够提供更高的带宽、高精度和较短时间窗口内的离散采样能力,满足快速测量和控制应用的要求。 高吞吐速率、低功耗和小尺寸则有助于设计人员应对高通道密度系统中常见的空间、散热、功耗及其他重要设计挑战。 针对满量程输入信号,SAR型ADC还能提供最低的噪底,实现更高的SNR和出色的线性度,但与Σ-Δ型ADC不同的是,SAR型ADC无法抑制接近DC(50/60 Hz)的1/f 噪声。

SAR型和Σ-Δ型ADC各有千秋,数据采集系统设计人员必须根据性能、速度、空间、功耗和成本要求进行抉择。

放大器 ADC 滤波器 ADI 低通滤波器 FPGA 相关文章:

- 使用简化电路的高压放大器(11-21)

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 对数放大器的技术指标(11-26)

- 一种增大放大器增益的方法(11-28)

- 对数放大器的典型应用 (11-26)

- AGC中频放大器的设计 (11-29)