运放稳定性连载8:单电源缓冲器电路的实际设计(1)

时间:07-31

来源:互联网

点击:

作者:Tim Green,德州仪器公司

本系列的第5部分将着重讨论“实际”应用,我们到目前为止所学会的技巧和经验都将得到应用,帮助我们方便地稳定一个复杂的电路。我们将设计一个通用单电源缓冲放大器(将2.1V 缓冲至4.1V 参考),5V 单电源供电使它能够线性地工作,可提供较大的输出电流(>13mA),并在 -40°C 至 +125°C 工作温度范围的飘移为0.4V。虽然可将该电路用于许多应用中,但我们仍将简要介绍一下促使给出这个设计的原因,并解释为何没有现成的电路可用来完成此项工作。我们这里采用综合技术来开发器件网络,以提供一个证明对许多运放应用都有益的稳定电路。

技术背景:

在实际应用中,惠斯通电桥的一个常见应用就是压力测量。如图5.1 所示,随着所加压力变化,很多这种压力传感器都具有明显的二阶非线性特性。

图5.1 典型实际传感器输出比所加压力

图字(上、下):室温下电桥输出与压力关系、理想传感器、实际传感器;

坐标轴字: X 轴:压力、Y 轴:Vexc=1V 时的电桥输出(V/V 或Vbridge)

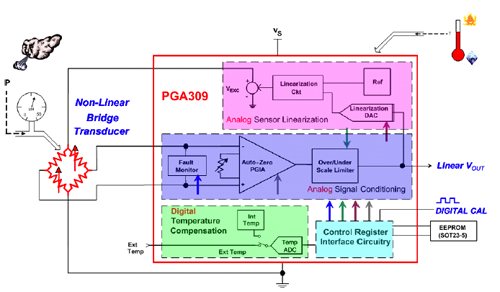

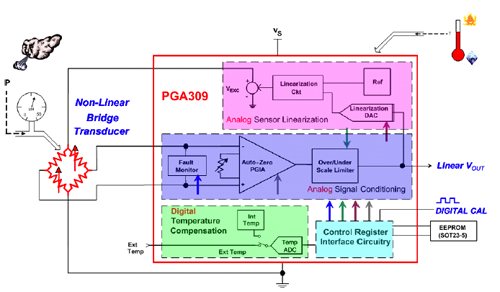

除了随所加压力变化而产生的非线性外,许多压力传感器随温度变化在偏移量和范围上也有非线性特性。用来校正这些误差的一种现代解决方法是在压力传感器中内置电子电路,然后将电子电路与压力传感器作为一个模块,随着温度的变化进行数字校准。一种适用于此类用途的IC是由德州仪器公司提供的Burr-Brown产品PGA309(如图5.2 所示)。此输出电压已经过数字校准的传感器,其信号调整IC包含有一个模拟传感器线性化电路,该电路将输出电压的一部分反馈至传感器的电压激励引脚,从而以20:1 的改良比例对二阶非线性进行线性化。因此,VEXC引脚将随传感器所加压力的变化而对其电压进行调整。此电路的一个局限就是其传感器激励引脚VEXC,在工作温度范围内限制在5mA最大输出电流上。这里我们遇到了一个两难的境地,即如何用一个阻抗来激励要求电流超过5mA的传感器。

图 5.2:现代数字校准传感器信号调整器

图字(左右、上下):非线性电传式感器、线性化电路、参考、模拟传感器线性化电路、线性化DAC、故障监视器、自动零点PGIA、过/欠刻度限幅器、模拟信号调整电路、外部温度、数字温度补偿、内部温度、温度ADC、控制寄存器接口电路、线性Vout、数字计算。

设计要求:

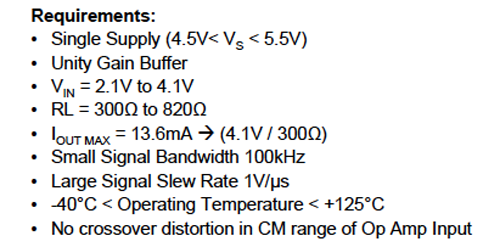

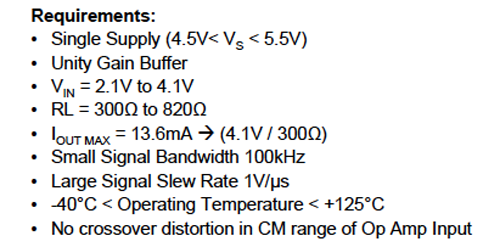

图5.3 详细给出了主要的设计指标。我们希望用一个容差为10%的5V电源来供电。我们需要一个统一增益缓冲器,因为我们不希望在PGA309 线性化环路中引入任何误差。由于PGA309 在VEXC引脚上有很宽的可编程范围,因此我们需要容纳从2.1V至4.1V的电压范围。我们最小的传感器阻值为300Ω。因此,对于最大4.1V的输出电压,我们至少需要提供13.6mA的电流。PGA309 线性化电路具有大约35 kHz的带宽。由于环路闭合的方式,我们的缓冲器带宽至少要等于或大于线性化环路的带宽。我们将目标定为100kHz的小信号闭环带宽。对于我们感兴趣的传感器应用来说,大信号响应若有1V/μs的摆动速率就足够了。该设计在从 -40°C 至 +125°C的温度范围内应该是稳定工作的。因为我们不希望由于缓冲器的原因而在最后应用电路中引入任何额外的误差,因此我们需要一个在运放共模输入范围内不会有任何交叉失真的电路。我们将简要讨论一下这个问题,因为它几乎对所有CMOS单电源轨至轨输入 (RRI) 运放来说都是一个问题。

图5.3 单电源、大电流缓冲器指标

图字:

指标:

单电源(4.5V统一增益缓冲器

VIN=2.1V 至4.1V

RL=300Ω到820Ω

IOUT MAX=13.6mA→(4.1V/300Ω)

小信号带宽100kHz

大信号摆动速率1V/μs

-40°C <工作温度<+125°C

在运放的共模范围内不能有交叉失真

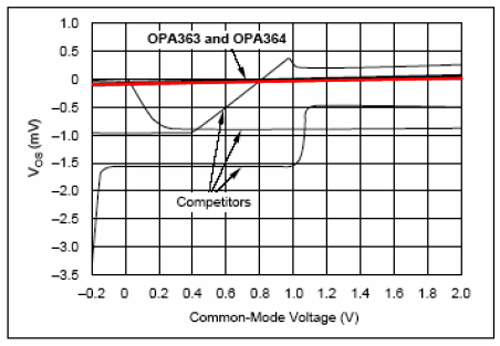

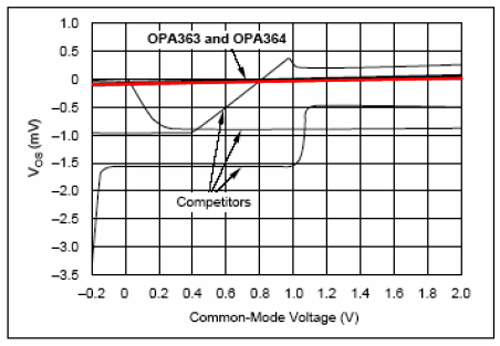

对于轨至轨输入运放,传统的解决方案是将N沟道和P沟道MOSFET并联使用来实现轨以外的摆动。问题是这里存在着一个过渡区,如图5.4所示,此处两对晶体管都是打开。在此区域,PSR、CMR、偏移电压及偏移漂移都与通常情况不同。现代解决方法采用正在申请专利的低噪声电荷泵浦技术,来避免使用传统技术中的并联N沟道与P沟道MOSFET。这样就能消除偏移量被打乱的过渡区。在整个共模范围内,OPA363 和 OPA364 均有线性偏移。上面给出的典型曲线是对1.8V电源来说的。当电源电压升到 +5V时,VOS的变化及非线性特性将变得更差。因此,为获得共模输入电压下最好的线性度,我们将采用OPA364。

图5.4:单电源、RRI运放VOS比共模输入电压关系曲线

图字:竞争产品、共模电压(V)

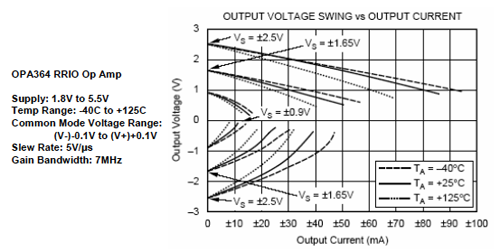

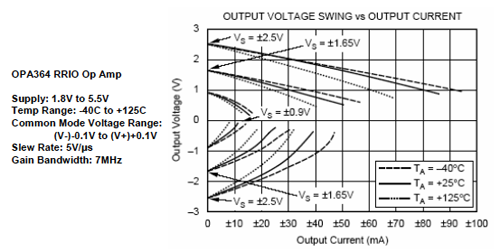

图5.5 给出了OPA364 的一些关键指标:

图5.5:OPA364 关键指标

图字:OPA364 RRIO 运放

电源电压:1.8V 至5.5V

温度范围:-40°C 至+125°C

共模电压范围:(V-)-0.1V 至 (V+)+0.1V

摆动速率:5V/μs

增益带宽:7MHz

输出电压摆动与输出电流之间的关系、输出电压(V)、输出电流(mA)

设计拓扑:

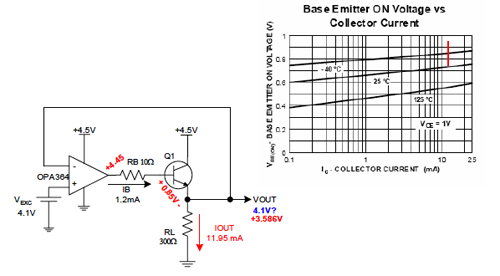

既然我们知道我们所拥有的电压空间很少,那么让我们使用双极型晶体管而不是MOSFET,因为双极型晶体管的Vbe 大约为0.65V,而MOSFET 的栅-源电压可能为2V 或更大。此外,让我们使用如图5.6 所示的射极跟随器结构。由于将超出电压空间,因此,如图5.6 所示,在任何温度下都无法使用射极跟随器结构,且在 -40°C 温度上情况最差。

图5.6:使用射极跟随器?–– 容易稳定!

图字:基极和发射极导通电压与集电极电流关系 、VBE(ON)-基极和发射极导通电压 (V)、IC-集电极电流 (mA)。

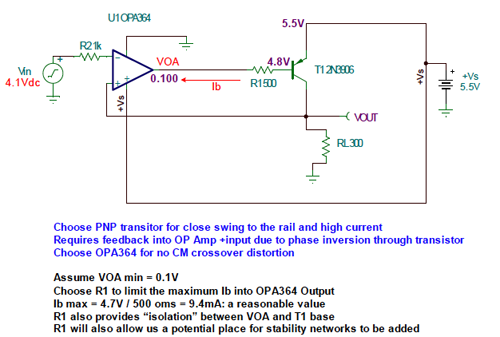

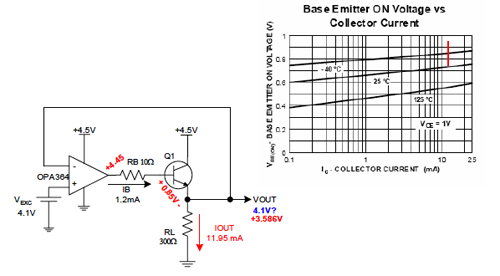

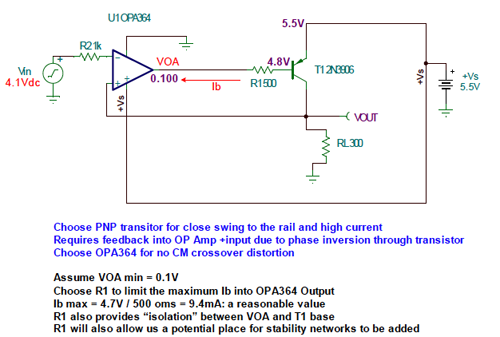

让我们先保留双极型晶体管,因为我们还是只有很少的电压空间。但让我们把晶体管变成一个PNP 型,如图5.7所示。现在我们看图5.7 所示的拓扑结构时觉得它看起来有点奇怪。乍一看,我们可能认为它似乎像使用了正反馈而且即将产生振荡!但经过进一步检查后我们会发现,事实上通过T1 我们获得了一个180 度的反相。我们可以直观地看到随着U1 输出的降低,更多的基极电流被驱动流过T1 的基极,这将导致更多的电流流入T1 的集电极并流过负载RL。然后这又会导致VOUT 增加。因此U1 输出的降低将导致VOUT 的增加。由于这个反相,我们的电路拓扑将用负输入U1 来作为输入,而将正输入U1 作为反馈点。

我们将增加一个R1 来限制 OPA364 在启动或瞬态条件下所需的最大瞬态或直流电流。R1 还将运放的输出与晶体管T1的寄生电容进行隔离,这样就提供了一个地方,如果需要的话可方便地加入稳定性网络。

图5.7:基本缓冲放大器电路拓扑

图字:选择PNP 晶体管以得到靠近电源轨的摆动及大电流

要求反馈至运放+由于通过晶体管反相的输入

选择OPA364 避免共模交叉失真

假定最小 VOA =0.1V

选择R1 来限制流入OPA364 输出端的最大Ib 值

最大Ib =4.7V/500 欧姆 =9.4mA:一个合理值

R1 也提供了VOA 和T1 基极之间的“隔离”

R1 还使我们有潜在地方来加入稳定性网络

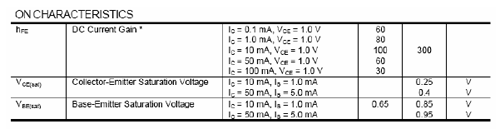

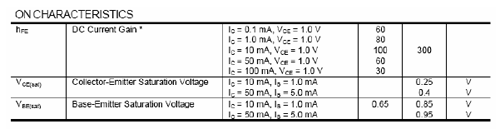

图5.8 详细给出了我们所需要的有关T1——2N3906 PNP 晶体管的一些关键参数。

图5.8: T1-2N3906 关键参数

图字:开通特性

直流电流增益、集电极-发射极饱和电压、基极-发射极饱和电压

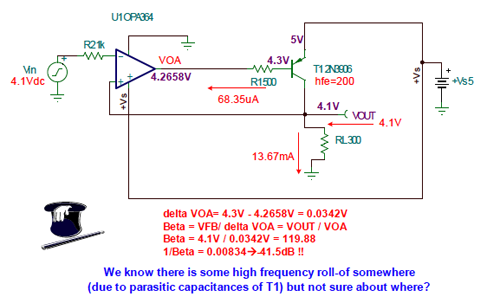

1/β 分析:

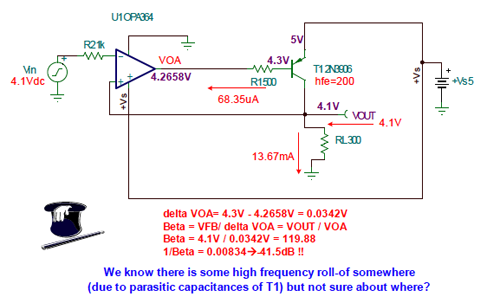

现在我们开始对缓冲器电路进行稳定性分析。首先,图5.9 详细给出了直流1/β 项的计算。假设T1 拥有hfe =200 的电流增益,300Ω负载需要从缓冲器电路上得到4.1V 上的13.67mA 电流。这意味着T1 处的基极电流将需要68.35uA。假设T1 的压降Vbe 为0.7V,我们将看到VOA 将需要4.2658V 电压来提供T1 所需的基极电流。如图5.9 所示,这意味着OPA364 的输出电压若有0.0342V 的变化,将导致13.67mA 的电流流入RL。因此,我们可以计算在此电路中与电压有关的β 项,得到的计算值为119.88。对直流1/β,这意味着 -41.5dB 的值。对大多数运放电路而言,1/β 通常是一个正数,但我们所开发的技术仍然有效,并使我们能分析此电路拓扑。通过在运放电路的反馈路径中增加增益,我们就得到了一个负的1/β 值。我们知道,在晶体管T1 中有寄生电容,我们猜测它可能会在反馈路径中引入几个高频极点——亦即1/β 曲线上的零点。但无论是从器件数据资料来看,还是经过和经验丰富的IC 设计者就如何在环路分析中方便地确定电容的影响进行长时间讨论以后,这一点也并不十分明显。因此我们将获取制造商的SPICE 晶体管模型,并用Tina SPICE 仿真来为我们演示它们应位于何处。

图5.9:什么是直流1/β?

图字:我们知道在某些地方会有一些高频极点(由于T1 的寄生电容),但我们不能确定在哪里?

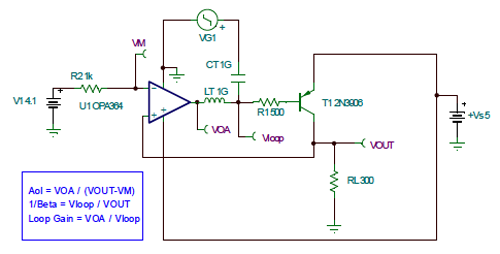

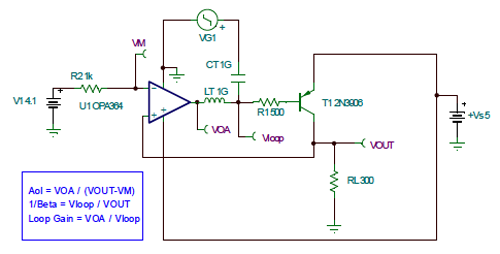

图5.10显示我们如何用Tina SPICE电路来寻找可能出现的高频极点。请注意,我们使用了一个直流电压V1,它设置了我们的直流工作点,这样晶体管T1就在其实际工作点附近被偏置。这能保证我们能获得适当的交流分析结果。

图5.10:“高频极点在哪里?”电路

图字:Aol=VOA/(VOUT-VM)

1/Beta=Vloop/VOUT

环路增益=VOA/Vloop

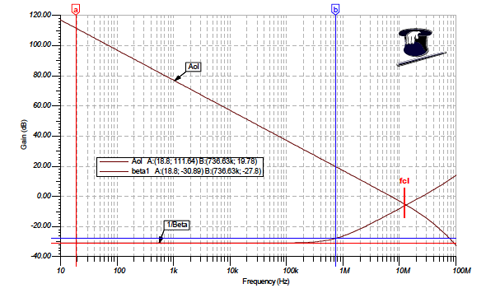

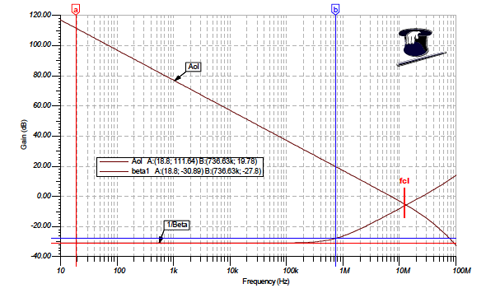

图5.11 给出了我们寻找高频极点的仿真结果。我们注意到,对RL = 300Ω 来说直流1/β 值为 -30.89dB。我们用一阶分析得到的预测值为 -41.5dB。如同实际的结果,仿真结果也依赖于实际使用的晶体管。对于RL = 820Ω,仿真结果表明直流1/β 值为 -39.6dB。我们确实希望β 值会随负载的增加而增加(1/β 值降低)。VOUT 保持不变,但负载增加时IOUT 减少,因此基极电流变小,ΔVOA 也变小。这就说明,将β 设为较大值(1/β 设为较值)时VOUT /ΔVOA 将变大(负dB 数量级更大)。我们看到高频极点在大约736kHz 处。为便于使用一阶分析,我们取直流 1/β 值为 -40dB 而高频极点为1MHz。根据我们关于稳定性的一阶闭合速度准则,我们发现电流缓冲电路是不稳定的(fcl 处的闭合速度为40dB/Decade)!

图5.11:找到高频极点!

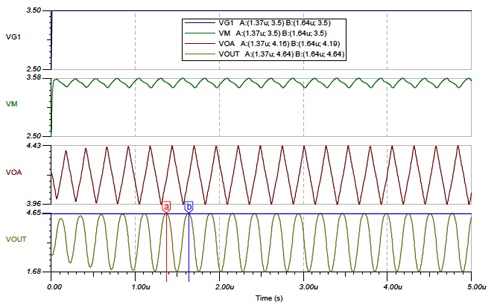

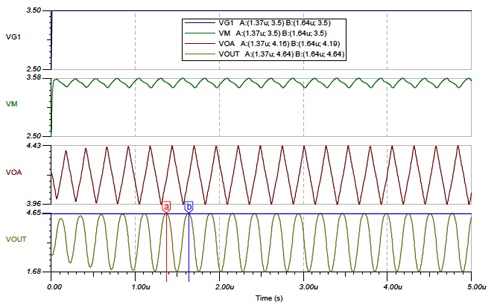

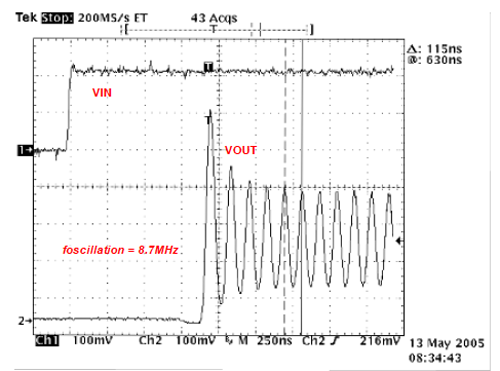

作为对我们的不稳定性预测的快速验证,我们对如图5.12 所示的现有缓冲器电路做了一个Tina 瞬态分析,这类似于我们的实际稳定性测试。如图5.13 所示,我们发现它振荡得很严重!

图5.12:瞬态分析电路 –––– 缓冲器拓扑w/o 补偿

图5.13:瞬态分析结果 –––– 缓冲器拓扑w/o 补偿

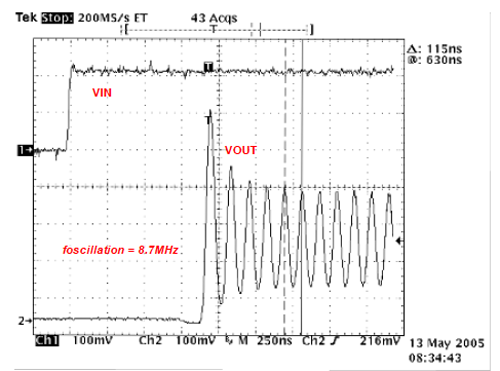

我们在实验室建成了缓冲器拓扑w/o补偿结构,以100Hz方波激励的结果如图5.14所示。现在,通过预计电路的不稳定性,我们“闭合了环路”。通过用一阶分析预测,再用Tina SPICE仿真,最后在实际电路中证明这个电路如同预计的一样,是不稳定的。振荡的准确频率与SPICE 仿真结果并不相同,这是因为使用了别的晶体管来代替T1,就算实验室有2N3906 可用的话,也无法得到2N3906 在 SPICE 模型中所具有的确切参数。

图5.14:“实际瞬态稳定性测试结果” –––– 缓冲器拓扑 w/o 补偿

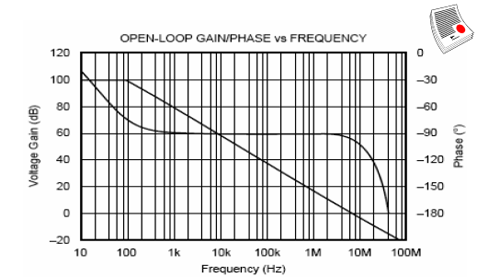

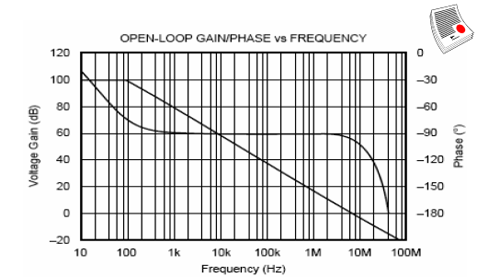

为进一步进行我们的一阶稳定性分析,我们需要从数据资料中找到OPA364 的Aol 曲线,曲线如图5.15 所示。

图5.15:OPA364 数据资料Aol 曲线

图字(上下、左右):开环增益/相位与频率关系、电压增益(dB)、相位 (°)、频率 (Hz)。

本系列的第5部分将着重讨论“实际”应用,我们到目前为止所学会的技巧和经验都将得到应用,帮助我们方便地稳定一个复杂的电路。我们将设计一个通用单电源缓冲放大器(将2.1V 缓冲至4.1V 参考),5V 单电源供电使它能够线性地工作,可提供较大的输出电流(>13mA),并在 -40°C 至 +125°C 工作温度范围的飘移为0.4V。虽然可将该电路用于许多应用中,但我们仍将简要介绍一下促使给出这个设计的原因,并解释为何没有现成的电路可用来完成此项工作。我们这里采用综合技术来开发器件网络,以提供一个证明对许多运放应用都有益的稳定电路。

技术背景:

在实际应用中,惠斯通电桥的一个常见应用就是压力测量。如图5.1 所示,随着所加压力变化,很多这种压力传感器都具有明显的二阶非线性特性。

图5.1 典型实际传感器输出比所加压力

图字(上、下):室温下电桥输出与压力关系、理想传感器、实际传感器;

坐标轴字: X 轴:压力、Y 轴:Vexc=1V 时的电桥输出(V/V 或Vbridge)

除了随所加压力变化而产生的非线性外,许多压力传感器随温度变化在偏移量和范围上也有非线性特性。用来校正这些误差的一种现代解决方法是在压力传感器中内置电子电路,然后将电子电路与压力传感器作为一个模块,随着温度的变化进行数字校准。一种适用于此类用途的IC是由德州仪器公司提供的Burr-Brown产品PGA309(如图5.2 所示)。此输出电压已经过数字校准的传感器,其信号调整IC包含有一个模拟传感器线性化电路,该电路将输出电压的一部分反馈至传感器的电压激励引脚,从而以20:1 的改良比例对二阶非线性进行线性化。因此,VEXC引脚将随传感器所加压力的变化而对其电压进行调整。此电路的一个局限就是其传感器激励引脚VEXC,在工作温度范围内限制在5mA最大输出电流上。这里我们遇到了一个两难的境地,即如何用一个阻抗来激励要求电流超过5mA的传感器。

图 5.2:现代数字校准传感器信号调整器

图字(左右、上下):非线性电传式感器、线性化电路、参考、模拟传感器线性化电路、线性化DAC、故障监视器、自动零点PGIA、过/欠刻度限幅器、模拟信号调整电路、外部温度、数字温度补偿、内部温度、温度ADC、控制寄存器接口电路、线性Vout、数字计算。

设计要求:

图5.3 详细给出了主要的设计指标。我们希望用一个容差为10%的5V电源来供电。我们需要一个统一增益缓冲器,因为我们不希望在PGA309 线性化环路中引入任何误差。由于PGA309 在VEXC引脚上有很宽的可编程范围,因此我们需要容纳从2.1V至4.1V的电压范围。我们最小的传感器阻值为300Ω。因此,对于最大4.1V的输出电压,我们至少需要提供13.6mA的电流。PGA309 线性化电路具有大约35 kHz的带宽。由于环路闭合的方式,我们的缓冲器带宽至少要等于或大于线性化环路的带宽。我们将目标定为100kHz的小信号闭环带宽。对于我们感兴趣的传感器应用来说,大信号响应若有1V/μs的摆动速率就足够了。该设计在从 -40°C 至 +125°C的温度范围内应该是稳定工作的。因为我们不希望由于缓冲器的原因而在最后应用电路中引入任何额外的误差,因此我们需要一个在运放共模输入范围内不会有任何交叉失真的电路。我们将简要讨论一下这个问题,因为它几乎对所有CMOS单电源轨至轨输入 (RRI) 运放来说都是一个问题。

图5.3 单电源、大电流缓冲器指标

图字:

指标:

单电源(4.5V统一增益缓冲器

VIN=2.1V 至4.1V

RL=300Ω到820Ω

IOUT MAX=13.6mA→(4.1V/300Ω)

小信号带宽100kHz

大信号摆动速率1V/μs

-40°C <工作温度<+125°C

在运放的共模范围内不能有交叉失真

对于轨至轨输入运放,传统的解决方案是将N沟道和P沟道MOSFET并联使用来实现轨以外的摆动。问题是这里存在着一个过渡区,如图5.4所示,此处两对晶体管都是打开。在此区域,PSR、CMR、偏移电压及偏移漂移都与通常情况不同。现代解决方法采用正在申请专利的低噪声电荷泵浦技术,来避免使用传统技术中的并联N沟道与P沟道MOSFET。这样就能消除偏移量被打乱的过渡区。在整个共模范围内,OPA363 和 OPA364 均有线性偏移。上面给出的典型曲线是对1.8V电源来说的。当电源电压升到 +5V时,VOS的变化及非线性特性将变得更差。因此,为获得共模输入电压下最好的线性度,我们将采用OPA364。

图5.4:单电源、RRI运放VOS比共模输入电压关系曲线

图字:竞争产品、共模电压(V)

图5.5 给出了OPA364 的一些关键指标:

图5.5:OPA364 关键指标

图字:OPA364 RRIO 运放

电源电压:1.8V 至5.5V

温度范围:-40°C 至+125°C

共模电压范围:(V-)-0.1V 至 (V+)+0.1V

摆动速率:5V/μs

增益带宽:7MHz

输出电压摆动与输出电流之间的关系、输出电压(V)、输出电流(mA)

设计拓扑:

既然我们知道我们所拥有的电压空间很少,那么让我们使用双极型晶体管而不是MOSFET,因为双极型晶体管的Vbe 大约为0.65V,而MOSFET 的栅-源电压可能为2V 或更大。此外,让我们使用如图5.6 所示的射极跟随器结构。由于将超出电压空间,因此,如图5.6 所示,在任何温度下都无法使用射极跟随器结构,且在 -40°C 温度上情况最差。

图5.6:使用射极跟随器?–– 容易稳定!

图字:基极和发射极导通电压与集电极电流关系 、VBE(ON)-基极和发射极导通电压 (V)、IC-集电极电流 (mA)。

让我们先保留双极型晶体管,因为我们还是只有很少的电压空间。但让我们把晶体管变成一个PNP 型,如图5.7所示。现在我们看图5.7 所示的拓扑结构时觉得它看起来有点奇怪。乍一看,我们可能认为它似乎像使用了正反馈而且即将产生振荡!但经过进一步检查后我们会发现,事实上通过T1 我们获得了一个180 度的反相。我们可以直观地看到随着U1 输出的降低,更多的基极电流被驱动流过T1 的基极,这将导致更多的电流流入T1 的集电极并流过负载RL。然后这又会导致VOUT 增加。因此U1 输出的降低将导致VOUT 的增加。由于这个反相,我们的电路拓扑将用负输入U1 来作为输入,而将正输入U1 作为反馈点。

我们将增加一个R1 来限制 OPA364 在启动或瞬态条件下所需的最大瞬态或直流电流。R1 还将运放的输出与晶体管T1的寄生电容进行隔离,这样就提供了一个地方,如果需要的话可方便地加入稳定性网络。

图5.7:基本缓冲放大器电路拓扑

图字:选择PNP 晶体管以得到靠近电源轨的摆动及大电流

要求反馈至运放+由于通过晶体管反相的输入

选择OPA364 避免共模交叉失真

假定最小 VOA =0.1V

选择R1 来限制流入OPA364 输出端的最大Ib 值

最大Ib =4.7V/500 欧姆 =9.4mA:一个合理值

R1 也提供了VOA 和T1 基极之间的“隔离”

R1 还使我们有潜在地方来加入稳定性网络

图5.8 详细给出了我们所需要的有关T1——2N3906 PNP 晶体管的一些关键参数。

图5.8: T1-2N3906 关键参数

图字:开通特性

直流电流增益、集电极-发射极饱和电压、基极-发射极饱和电压

1/β 分析:

现在我们开始对缓冲器电路进行稳定性分析。首先,图5.9 详细给出了直流1/β 项的计算。假设T1 拥有hfe =200 的电流增益,300Ω负载需要从缓冲器电路上得到4.1V 上的13.67mA 电流。这意味着T1 处的基极电流将需要68.35uA。假设T1 的压降Vbe 为0.7V,我们将看到VOA 将需要4.2658V 电压来提供T1 所需的基极电流。如图5.9 所示,这意味着OPA364 的输出电压若有0.0342V 的变化,将导致13.67mA 的电流流入RL。因此,我们可以计算在此电路中与电压有关的β 项,得到的计算值为119.88。对直流1/β,这意味着 -41.5dB 的值。对大多数运放电路而言,1/β 通常是一个正数,但我们所开发的技术仍然有效,并使我们能分析此电路拓扑。通过在运放电路的反馈路径中增加增益,我们就得到了一个负的1/β 值。我们知道,在晶体管T1 中有寄生电容,我们猜测它可能会在反馈路径中引入几个高频极点——亦即1/β 曲线上的零点。但无论是从器件数据资料来看,还是经过和经验丰富的IC 设计者就如何在环路分析中方便地确定电容的影响进行长时间讨论以后,这一点也并不十分明显。因此我们将获取制造商的SPICE 晶体管模型,并用Tina SPICE 仿真来为我们演示它们应位于何处。

图5.9:什么是直流1/β?

图字:我们知道在某些地方会有一些高频极点(由于T1 的寄生电容),但我们不能确定在哪里?

图5.10显示我们如何用Tina SPICE电路来寻找可能出现的高频极点。请注意,我们使用了一个直流电压V1,它设置了我们的直流工作点,这样晶体管T1就在其实际工作点附近被偏置。这能保证我们能获得适当的交流分析结果。

图5.10:“高频极点在哪里?”电路

图字:Aol=VOA/(VOUT-VM)

1/Beta=Vloop/VOUT

环路增益=VOA/Vloop

图5.11 给出了我们寻找高频极点的仿真结果。我们注意到,对RL = 300Ω 来说直流1/β 值为 -30.89dB。我们用一阶分析得到的预测值为 -41.5dB。如同实际的结果,仿真结果也依赖于实际使用的晶体管。对于RL = 820Ω,仿真结果表明直流1/β 值为 -39.6dB。我们确实希望β 值会随负载的增加而增加(1/β 值降低)。VOUT 保持不变,但负载增加时IOUT 减少,因此基极电流变小,ΔVOA 也变小。这就说明,将β 设为较大值(1/β 设为较值)时VOUT /ΔVOA 将变大(负dB 数量级更大)。我们看到高频极点在大约736kHz 处。为便于使用一阶分析,我们取直流 1/β 值为 -40dB 而高频极点为1MHz。根据我们关于稳定性的一阶闭合速度准则,我们发现电流缓冲电路是不稳定的(fcl 处的闭合速度为40dB/Decade)!

图5.11:找到高频极点!

作为对我们的不稳定性预测的快速验证,我们对如图5.12 所示的现有缓冲器电路做了一个Tina 瞬态分析,这类似于我们的实际稳定性测试。如图5.13 所示,我们发现它振荡得很严重!

图5.12:瞬态分析电路 –––– 缓冲器拓扑w/o 补偿

图5.13:瞬态分析结果 –––– 缓冲器拓扑w/o 补偿

我们在实验室建成了缓冲器拓扑w/o补偿结构,以100Hz方波激励的结果如图5.14所示。现在,通过预计电路的不稳定性,我们“闭合了环路”。通过用一阶分析预测,再用Tina SPICE仿真,最后在实际电路中证明这个电路如同预计的一样,是不稳定的。振荡的准确频率与SPICE 仿真结果并不相同,这是因为使用了别的晶体管来代替T1,就算实验室有2N3906 可用的话,也无法得到2N3906 在 SPICE 模型中所具有的确切参数。

图5.14:“实际瞬态稳定性测试结果” –––– 缓冲器拓扑 w/o 补偿

为进一步进行我们的一阶稳定性分析,我们需要从数据资料中找到OPA364 的Aol 曲线,曲线如图5.15 所示。

图5.15:OPA364 数据资料Aol 曲线

图字(上下、左右):开环增益/相位与频率关系、电压增益(dB)、相位 (°)、频率 (Hz)。

德州仪器 电路 放大器 电流 传感器 压力传感器 电子 电压 DAC ADC CMOS MOSFET 电容 PIC 仿真 相关文章:

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)

- 运算放大器的选择(03-18)

- 单端数字音频放大器设计和应用考虑的要素(05-19)

- 为网络监控摄像机设计合适的电源(05-20)

- 改善可编程增益放大器性能的一个技巧(05-21)