可重组多功能大数运算器的小规模硬件实现

时间:12-08

来源:互联网

点击:

2.3 其他功能实现

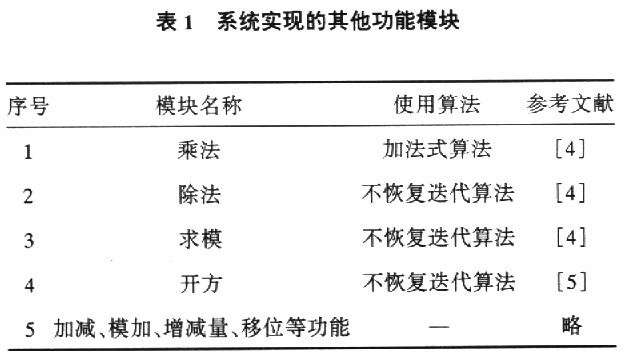

经过对多种公钥加解密算法及签名算法的分析,为提高芯片整体灵活性本设计还给出了对乘法、除法、求模、模加法逆、开方几种常用运算的支持.同样选择基于加减运算的算法实现,充分考虑算法对扫描链等已有逻辑资源的服用,设计出符合产品运算速度的面积最小化的系统.表1列出系统实现的其他功能模块采用的算法名称、详细算法及相关文献.

3 设计实现

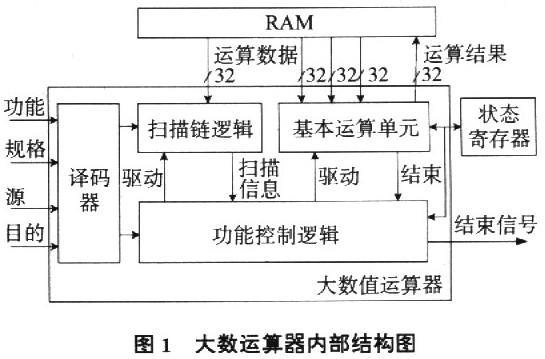

以一个可以完成32位规格加、减、模加、增减量、移位等基本功能的ALU为基本运算单元,在扫描链逻辑的控制下,可以完成乘、除、开方、模乘、模幂乘等多种复杂运算.设计结构如图1所示.大数值运算器的外接口信号分以下三类:

(1)控制:功能,规格以及源、目的指示;

(2)数据:来自体RAM的源操作数,运算结果到RAM的反馈;

(3)状态:运算结束,对体系相应状态寄存器的控制信号。

基本运算单元(ALU):可在单周期内完成32位加减、增(减)量、模加、左右移一位功能,其核心结构如图2所示,由输入选通控制MUX-IN,32位加法器ADD,32位减法器SUB,移位逻辑SF和输出选通控制MUX-OUT组成。

各功能在ALU中的具体实现方式见表2:

功能控制逻辑:完成各个功能的控制,可分为简单功能和复杂功能两类不同的控制.

1)简单功能:32位规格以上的加减、模加、增(减)量、移位功能.功能实现通过多周期迭代调用ALU相应功能实现,多次调用间保持进/借位传递。

2)复杂功能:模乘、模幂乘、乘除、开方功能.根据算法原理设计状态机,根据扫描链逻辑的配合信号,通过调用简单功能实现运算。

扫描链逻辑:当功能控制逻辑在完成复杂功能时,驱动扫描链逻辑动作.核心电路为32位的移位寄存器,扫描链逻辑可完成:待扫描数据的自动装载和切换;扫描数据高位0的自动去除,即自动找到第一个1,并给出标识信号;在使能信号的控制下从高到低自动扫描数据,给出扫描结果;扫描结束给出结束信号。

4 测试及结论

本文提出了一种用于可重组安全芯片的,面积优先、多功能、可重组的大数值运算器的实现方法设计支持的所有功能及规格如表3所示.所有模块均在ModelSim环境下通过了逻辑仿真,并在Xilinx公司的Virtex-Ⅱ系列FPGA产品XC2V6000上经过实际功能验证。

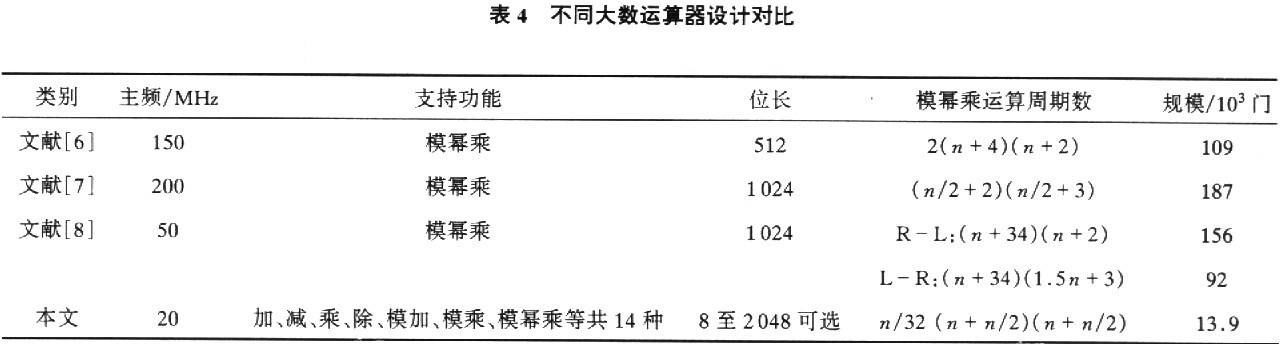

使用Synopsys公司Design Compiler综合工具,在台基电(TSMC)0.25μm工艺和安全芯片要求的20Hz时钟主频下的综合结果为13 887门.设计的结果与近年的几个大数值运算器的对比见表4.可见本设计虽然运算速度稍慢,但设计规模同比大大降低,完全符合CSTU保密终端安全芯片对面积优先的设计要求,速度也在设计允许范围内。

经过对多种公钥加解密算法及签名算法的分析,为提高芯片整体灵活性本设计还给出了对乘法、除法、求模、模加法逆、开方几种常用运算的支持.同样选择基于加减运算的算法实现,充分考虑算法对扫描链等已有逻辑资源的服用,设计出符合产品运算速度的面积最小化的系统.表1列出系统实现的其他功能模块采用的算法名称、详细算法及相关文献.

3 设计实现

以一个可以完成32位规格加、减、模加、增减量、移位等基本功能的ALU为基本运算单元,在扫描链逻辑的控制下,可以完成乘、除、开方、模乘、模幂乘等多种复杂运算.设计结构如图1所示.大数值运算器的外接口信号分以下三类:

(1)控制:功能,规格以及源、目的指示;

(2)数据:来自体RAM的源操作数,运算结果到RAM的反馈;

(3)状态:运算结束,对体系相应状态寄存器的控制信号。

基本运算单元(ALU):可在单周期内完成32位加减、增(减)量、模加、左右移一位功能,其核心结构如图2所示,由输入选通控制MUX-IN,32位加法器ADD,32位减法器SUB,移位逻辑SF和输出选通控制MUX-OUT组成。

各功能在ALU中的具体实现方式见表2:

功能控制逻辑:完成各个功能的控制,可分为简单功能和复杂功能两类不同的控制.

1)简单功能:32位规格以上的加减、模加、增(减)量、移位功能.功能实现通过多周期迭代调用ALU相应功能实现,多次调用间保持进/借位传递。

2)复杂功能:模乘、模幂乘、乘除、开方功能.根据算法原理设计状态机,根据扫描链逻辑的配合信号,通过调用简单功能实现运算。

扫描链逻辑:当功能控制逻辑在完成复杂功能时,驱动扫描链逻辑动作.核心电路为32位的移位寄存器,扫描链逻辑可完成:待扫描数据的自动装载和切换;扫描数据高位0的自动去除,即自动找到第一个1,并给出标识信号;在使能信号的控制下从高到低自动扫描数据,给出扫描结果;扫描结束给出结束信号。

4 测试及结论

本文提出了一种用于可重组安全芯片的,面积优先、多功能、可重组的大数值运算器的实现方法设计支持的所有功能及规格如表3所示.所有模块均在ModelSim环境下通过了逻辑仿真,并在Xilinx公司的Virtex-Ⅱ系列FPGA产品XC2V6000上经过实际功能验证。

使用Synopsys公司Design Compiler综合工具,在台基电(TSMC)0.25μm工艺和安全芯片要求的20Hz时钟主频下的综合结果为13 887门.设计的结果与近年的几个大数值运算器的对比见表4.可见本设计虽然运算速度稍慢,但设计规模同比大大降低,完全符合CSTU保密终端安全芯片对面积优先的设计要求,速度也在设计允许范围内。

电路 ModelSim 仿真 Xilinx FPGA 相关文章:

- 整流电路(11-30)

- 单运放构成的单稳延时电路(11-29)

- 直流稳压电源电路(11-30)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 为太阳能灯供电的低损耗电路的设计(01-22)