减小ADC量化噪声的技术

时间:01-14

来源:互联网

点击:

数模转换器(ADC)提供了许多系统中模拟信号到数字信号的重要转换。它们完成一个模拟输入信号到二元有限长度输出命令的振幅量化,范围通常在6到18b之间,是一个固有的非线性过程。该非线性特性表现为ADC二元输出中的宽带噪声,称作量化噪声,它限制了一个ADC的动态范围。本文描述了两种时下最流行的方法来改善实际ADC应用中的量化噪声性能:过采样和高频抖动。

为理解量化噪声缩减法,首先让我们回顾一下,一个理想的N位ADC的信号与量化噪声比为(单位dB)

SNRQ=6.02N+4.77+20log10(LF)dB,

其中:LF=ADC的输入模拟电压级的加载因子测量(SNRQ由参考资料1提供)。参数LF定义为模拟输入电压的均方根(RMS)除以ADC的峰值输入电压。当ADC的输入电压为一个可以覆盖转换器满量程电压的正弦曲线,LF=0.707。假如那样的话,SNRQ等式中的最后一项变为?3dB,并且ADC的最大输出信号与噪声比为:

SNRQ-max=6.02N+4.77?3=6.02N+1.77dB。

在技术文献中非常普遍的SNRQ-max公式说明了为什么工程师要对ADC的SNR使用一个经验值6dB/b。

作为一个应用问题,SNRQ-max公式是不切实际的乐观。首先,SNR公式描绘了一个在现实世界中不存在的理想ADC。第二,在实际应用中,ADC的输入极少会覆盖全部值。现实世界的模拟信号通常实际上是脉冲信号,而促使ADC的输入变为饱和引发了可大大减小ADC输出SNR的信号切割。但是,本文将假设一个使用大部分输入模拟电压范围的高品质ADC而非研究最坏情况下的场景。

假定ADC的SNR为6dB/b,下一步是考虑作为可能改进SNRQ的过采样法。减小ADC量化噪声的过采样过程简单直观。模拟信号在fs采样率被数字化,该采样率高于满足Nyquist标准(两倍输入模拟信号带宽)所需的最小采样率,然后被低通过滤。

过采样基于如下假设:一个ADC的总量化噪声功率(方差)为转换器最小有效位(LSB)电压的平方除以12:

总量化噪声功率=σ2=(LSB value)/12

过采样同样假设量化噪声值是真实随机的;这意味着在频率范围内,量化噪声有一个平滑的频谱。(如果ADC是由一个覆盖转换器模拟输入电压范围重要部分的模拟信号驱动且周期性不明显,该假设有效)。

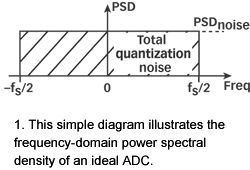

图1显示了量化噪声的另一方面,功率频谱密度(PSD)。这是在每Hz噪声功率下测量的量化噪声的频率范围特征。利用PSD,量化噪声可以被表示为每单位带宽的功率大小。随机噪声假设得到的总量化噪声(基于转换器LSB电压的固定值)被均匀分布在频率范围内,从?fs/2到+fs/2,如图1所示。该量化噪声PSD的振幅为总量化噪声功率除以总带宽fs,其中振幅出现在总带宽上:

PSDnoise=[(LSB value)2/12](1/fs)=(LSB value)2/12fs 单位为W/Hz。

下一个问题是:“怎样才能减小PSDnoise等级?”利用一个具有附加位分解的ADC,可以减小分子中的LSB值,这个ADC将减小LSD值同样也减小PSDnoise。不过这是一个昂贵的解决办法。更好的办法是用更高采样率来增大分母。

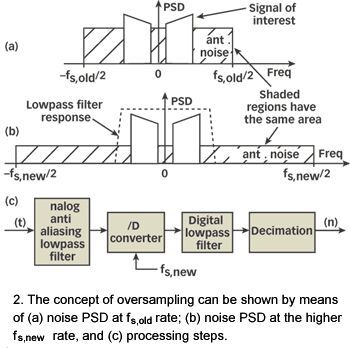

采用更高采样率的结果在图2(a)中用低级离散信号表示。通过将ADC的fs,old 采样率增加到某一更高值fs,new (过采样),总噪声功率(一个不变值)被分布在一个广泛的频率范围内[图2(b)]。由于一个转换器的总量化噪声功率仅依赖于位数而不是采样率,图2(a)和2(b)中阴暗曲线下的面积相等。将一个低通过率器放在转换器的输出来减小量化噪声等级对信号的损害。

通过过采样得到改进的信号与量化噪声比为,以dB为单位:

SNRQ-gain =10log10(fs,new /fs,old )。

SNRQ-gain 表达式的出处在参考资料1中提供。作为一个SNR的函数,N位ADC的位数大约是SNR/6,因此总有效位数为10log(M)/6+N,其中M=fs,new /fs old ,。这意味着如果采样率M为2,则ADC的有效位数是Nos=0.5+N。利用因数为2的过采样,可获得在有效SNR中的一半位。获得一个特殊的K额外有效位数所需的过采样率M由式子M=4K得出,因而有效位数为Nos=K+N。

举例说明,如果fs,old =100kHz,且fs,new=400kHz,SNRQ-gain =10log10(4)=6.02dB。这样,因数为4的过采样(和过滤)将量化噪声减小到1b。从而,有可能由一个N位ADC得到N+1位的性能,因为信号振幅分解是以更高采样速度为代价得到的。经过数字过滤后,输出信号可以被减小到低级fs,old 而不会有损改进了的SNR。

当然,为了能从过采样方案中受益,用于低通滤波器系数和寄存器的位数必需超过ADC的初始位数。通过利用依赖于用x(t)表示的干扰模拟噪声的数字低通过率器,就有可能采用图2(c)中与低采样率下所需的模拟过滤器相对的低性能(更简单)模拟抗混迭滤波器。

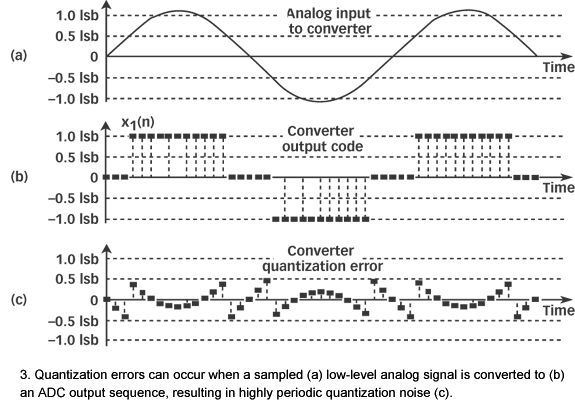

第二个用来最小化ADC量化噪声影响的技术是高频抖动,它在进行模拟数字转换前将噪声加入模拟信号。一个例子是,图3(a)中显示的数字化低级模拟正弦信号。该信号的峰值电压刚刚超过了单个ADC的LSB电压级,引起转换器输出x1 (n)个样本。由于高峰值正弦电压级,x1(n)输出序列被省略,并且在其频谱范围内产生谱谐波,该谐波与图3(c)中的量化噪声周期一样很明显。

为理解量化噪声缩减法,首先让我们回顾一下,一个理想的N位ADC的信号与量化噪声比为(单位dB)

SNRQ=6.02N+4.77+20log10(LF)dB,

其中:LF=ADC的输入模拟电压级的加载因子测量(SNRQ由参考资料1提供)。参数LF定义为模拟输入电压的均方根(RMS)除以ADC的峰值输入电压。当ADC的输入电压为一个可以覆盖转换器满量程电压的正弦曲线,LF=0.707。假如那样的话,SNRQ等式中的最后一项变为?3dB,并且ADC的最大输出信号与噪声比为:

SNRQ-max=6.02N+4.77?3=6.02N+1.77dB。

在技术文献中非常普遍的SNRQ-max公式说明了为什么工程师要对ADC的SNR使用一个经验值6dB/b。

作为一个应用问题,SNRQ-max公式是不切实际的乐观。首先,SNR公式描绘了一个在现实世界中不存在的理想ADC。第二,在实际应用中,ADC的输入极少会覆盖全部值。现实世界的模拟信号通常实际上是脉冲信号,而促使ADC的输入变为饱和引发了可大大减小ADC输出SNR的信号切割。但是,本文将假设一个使用大部分输入模拟电压范围的高品质ADC而非研究最坏情况下的场景。

假定ADC的SNR为6dB/b,下一步是考虑作为可能改进SNRQ的过采样法。减小ADC量化噪声的过采样过程简单直观。模拟信号在fs采样率被数字化,该采样率高于满足Nyquist标准(两倍输入模拟信号带宽)所需的最小采样率,然后被低通过滤。

过采样基于如下假设:一个ADC的总量化噪声功率(方差)为转换器最小有效位(LSB)电压的平方除以12:

总量化噪声功率=σ2=(LSB value)/12

过采样同样假设量化噪声值是真实随机的;这意味着在频率范围内,量化噪声有一个平滑的频谱。(如果ADC是由一个覆盖转换器模拟输入电压范围重要部分的模拟信号驱动且周期性不明显,该假设有效)。

|

图1显示了量化噪声的另一方面,功率频谱密度(PSD)。这是在每Hz噪声功率下测量的量化噪声的频率范围特征。利用PSD,量化噪声可以被表示为每单位带宽的功率大小。随机噪声假设得到的总量化噪声(基于转换器LSB电压的固定值)被均匀分布在频率范围内,从?fs/2到+fs/2,如图1所示。该量化噪声PSD的振幅为总量化噪声功率除以总带宽fs,其中振幅出现在总带宽上:

PSDnoise=[(LSB value)2/12](1/fs)=(LSB value)2/12fs 单位为W/Hz。

下一个问题是:“怎样才能减小PSDnoise等级?”利用一个具有附加位分解的ADC,可以减小分子中的LSB值,这个ADC将减小LSD值同样也减小PSDnoise。不过这是一个昂贵的解决办法。更好的办法是用更高采样率来增大分母。

采用更高采样率的结果在图2(a)中用低级离散信号表示。通过将ADC的fs,old 采样率增加到某一更高值fs,new (过采样),总噪声功率(一个不变值)被分布在一个广泛的频率范围内[图2(b)]。由于一个转换器的总量化噪声功率仅依赖于位数而不是采样率,图2(a)和2(b)中阴暗曲线下的面积相等。将一个低通过率器放在转换器的输出来减小量化噪声等级对信号的损害。

|

通过过采样得到改进的信号与量化噪声比为,以dB为单位:

SNRQ-gain =10log10(fs,new /fs,old )。

SNRQ-gain 表达式的出处在参考资料1中提供。作为一个SNR的函数,N位ADC的位数大约是SNR/6,因此总有效位数为10log(M)/6+N,其中M=fs,new /fs old ,。这意味着如果采样率M为2,则ADC的有效位数是Nos=0.5+N。利用因数为2的过采样,可获得在有效SNR中的一半位。获得一个特殊的K额外有效位数所需的过采样率M由式子M=4K得出,因而有效位数为Nos=K+N。

|

举例说明,如果fs,old =100kHz,且fs,new=400kHz,SNRQ-gain =10log10(4)=6.02dB。这样,因数为4的过采样(和过滤)将量化噪声减小到1b。从而,有可能由一个N位ADC得到N+1位的性能,因为信号振幅分解是以更高采样速度为代价得到的。经过数字过滤后,输出信号可以被减小到低级fs,old 而不会有损改进了的SNR。

当然,为了能从过采样方案中受益,用于低通滤波器系数和寄存器的位数必需超过ADC的初始位数。通过利用依赖于用x(t)表示的干扰模拟噪声的数字低通过率器,就有可能采用图2(c)中与低采样率下所需的模拟过滤器相对的低性能(更简单)模拟抗混迭滤波器。

第二个用来最小化ADC量化噪声影响的技术是高频抖动,它在进行模拟数字转换前将噪声加入模拟信号。一个例子是,图3(a)中显示的数字化低级模拟正弦信号。该信号的峰值电压刚刚超过了单个ADC的LSB电压级,引起转换器输出x1 (n)个样本。由于高峰值正弦电压级,x1(n)输出序列被省略,并且在其频谱范围内产生谱谐波,该谐波与图3(c)中的量化噪声周期一样很明显。

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)