微型高稳定锁相时钟频率源

低电平时,分频比为P。双模前置分频器的输出可同时驱动11位可编程计数器和7位吞脉冲计数器,它们的初值分别为N和A,可进行减计数。在吞脉冲计数器和可编程计数器未计数到零时,模式控制为高电平,双模前置分频器的输出频率为fVCO/(P+1)。当输A(P+1)个脉冲周期后,吞脉冲计数器计数达到零,模式控制电平将变为低电平,同时使吞脉冲计数器停止计数。此时,可编程计数器离预置数还有N-A的数值。由于这时模式控制电平为低,分频比为P,因此,双模前置分频器的输出频率为fVCO/P。之后,再经过N-A个计数周期后,可编程计数器计数也达到零,此时可输出低电平将两个可编程分频器重新预置为N和A,同时将模式控制恢复为高电平,并向鉴相器输出比相脉冲。当比相脉冲频率f参考频率fr存在频差时,鉴相器处于鉴频工作方式。此时无论频差大小,系统都输出较大的电压;而当比相脉冲频率f与参考频率fr相等时,鉴相器转为鉴相工作方式。这种鉴频-鉴相工作方式扩大了环路的快捕带,缩短了频率牵引过程,从而使环路快速进入相位锁定区,最终实现快捕锁定。

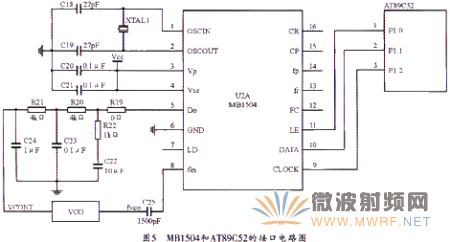

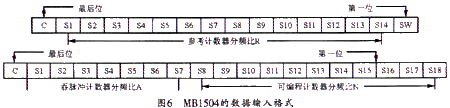

MB1504可通过9脚(Clock)、10脚(Data)和11脚(LE)分别与单片机AT89C52的P1.2、P1.1、P1.0相连,其连接电路如图5所示。其中,CLOCK为时钟信号输入端,DATA为数据信号输入端,LE为数据锁存使能信号输入端。信号是串行输入的,即每输入一个时钟脉冲到CLOCK脚,就有一位数据从DATA脚送入MB1504芯片内的移位寄存器,并由LE信号控制锁存。当LE为高电平时,储存在移位寄存器内的数据被锁存到相应的锁存器中。而当C为高电平时,锁存到15位的锁存器的设置为14位可编程参考分频器中的预置数R和前置分频器的1位分频比SW;当C为低电平时,锁存到18位的锁存器中的设置则为11位可编程计数器中的预置数N和7位吞脉冲计数器中的预置数A。图6所示为MB1504的数据输入格式。

根据MB1504的工作原理,锁相环的输出频率fvco的计算公式为:

式中,fosc为外接晶体振荡器输人参考频率;P为前置分频器的分频比(由位SW决定),当SW为高时,P为32;当SW为低时,P为64;N为11位可编程计数器中的预置数(范围从16~2047);A为7位吞脉冲计数器中的预置数(范围从0~63);R为14位可编程参考分频器中的预置数(范围从8~16383)。

本设计中,频率合成器的频率范围fout为80~88 MHz,频率间隔△f为2 kHz。参考振荡器的振荡频率fosc为4.096 MHz,参考频率fr等于合成器频率间隔△f(2 kHz),所以参考分频比R为:R=fosc/fr=2048,中心频率为84 MHz的分频比(PN+A=fout/△f)为42000。这里采用的前置分频比模式为÷32/33,即P=32,并由此可得:N=1312,A=16。这样,改变N和A,即可改变输出频率,而改变N、R,则可改变输出频率和频率间隔。

4 结束语

本设计的实际电路可以制作在一块50 mm×40mm的双层板上,电源电压为+3.3 V。VCO的频率覆盖范围为80~88MHz,两路输出电平,OUT端为-10 dBm,OUT端为-6 dBm。输出功率大于10dBm,且信号纯度很高,杂散较少。

由于几种LC元件和MAX2620构成的窄带VCO具有稳定性高、受外界分布参数影响小、调试方便、体积小、价格低廉等优点。因此,由该VCO和MB1504芯片构成的锁相时钟频率源的时钟频率源稳定性高、相位噪声较低。