一种SoC芯片在Magma Talus下的物理实现

时间:11-10

来源:互联网

点击:

4.3 动态时钟选择电路的时钟树约束

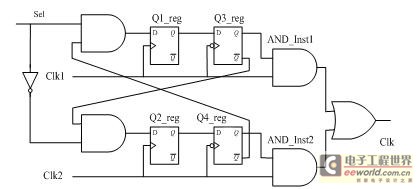

另外,PMC模块中使用动态时钟选择电路用来消除异步时钟间及同步时钟间动态切换过程中的毛刺,其中动态异步时钟选择电路结构如图8所示:

图8 动态异步时钟选择电路结构图

同样,我们针对该电路也做了如下约束:

force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst1/B \

…/PmcSysClkSel_Inst/Q1_reg/CK \

…/PmcSysClkSel_Inst/Q3_reg/CK" -skew_group 1

force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst2/B \

…/PmcSysClkSel_Inst/Q2_reg/CK \

…/PmcSysClkSel_Inst/Q4_reg/CK" -skew_group 2

第五章 总结

在本文中,我们介绍了一种SoC芯片架构,探讨了在0.18um CMOS工艺上以Magma Talus为主导EDA工具的物理实现中的3个难点问题:时序约束设计、布局规划以及时钟树约束设计。鉴于篇幅限制,其它在本SoC物理实现过程中涉及到的诸如信号完整性问题分析与避免、电源完整性分析与避免、与signoff工具间参数相关性的设置、ECO、模拟及数模混合模块建模及其在Magma Talus数字流程中的运用等方面在本文中未能涉及。

该SoC芯片包含41个时钟域,4种低功耗工作模式,2个相互隔离的1.8v内部电源域,约有65万个标准单元,94个宏模块,250个pad,合计约900万个逻辑等效门,3600万个晶体管,芯片面积10.5mmx10.5mm。

该芯片既有多个复杂的数字算法电路,也有多个定制的模拟/数模混合模块,宏模块众多,布局规划和电源规划较为复杂;在前仿真验证过程中方面,功能bug,性能不达标等问题,使RTL迟迟不能冻结,给后端留下的时间不多。我们借助Magma公司Talus软件在后端实现方面的强大能力,集中时间攻关,解决了复杂时序约束、大规模宏模块情况下布线拥塞的技术、多电压域下的电源规划技术以及复杂时钟树设计等难题,节省了大量的后端运行时间和手工工作,同时也实现了较好的时序、面积结果。

目前该芯片已成功流片,实测的性能及功耗指标均达到预期效果,高速总线时钟频率可达110M,normal功耗模式下算法模块全速工作时功耗小于380mW,sleep功耗模式下功耗11mW左右。

感谢Magma公司在物理实现方面持续的努力和进步,使得用户能够在设计中体会到革新所带来的便捷与快乐。在此,希望Magma今后能够不断革新,给用户带来更多的方便,分享更多的成功。

另外,PMC模块中使用动态时钟选择电路用来消除异步时钟间及同步时钟间动态切换过程中的毛刺,其中动态异步时钟选择电路结构如图8所示:

图8 动态异步时钟选择电路结构图

同样,我们针对该电路也做了如下约束:

force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst1/B \

…/PmcSysClkSel_Inst/Q1_reg/CK \

…/PmcSysClkSel_Inst/Q3_reg/CK" -skew_group 1

force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst2/B \

…/PmcSysClkSel_Inst/Q2_reg/CK \

…/PmcSysClkSel_Inst/Q4_reg/CK" -skew_group 2

第五章 总结

在本文中,我们介绍了一种SoC芯片架构,探讨了在0.18um CMOS工艺上以Magma Talus为主导EDA工具的物理实现中的3个难点问题:时序约束设计、布局规划以及时钟树约束设计。鉴于篇幅限制,其它在本SoC物理实现过程中涉及到的诸如信号完整性问题分析与避免、电源完整性分析与避免、与signoff工具间参数相关性的设置、ECO、模拟及数模混合模块建模及其在Magma Talus数字流程中的运用等方面在本文中未能涉及。

该SoC芯片包含41个时钟域,4种低功耗工作模式,2个相互隔离的1.8v内部电源域,约有65万个标准单元,94个宏模块,250个pad,合计约900万个逻辑等效门,3600万个晶体管,芯片面积10.5mmx10.5mm。

该芯片既有多个复杂的数字算法电路,也有多个定制的模拟/数模混合模块,宏模块众多,布局规划和电源规划较为复杂;在前仿真验证过程中方面,功能bug,性能不达标等问题,使RTL迟迟不能冻结,给后端留下的时间不多。我们借助Magma公司Talus软件在后端实现方面的强大能力,集中时间攻关,解决了复杂时序约束、大规模宏模块情况下布线拥塞的技术、多电压域下的电源规划技术以及复杂时钟树设计等难题,节省了大量的后端运行时间和手工工作,同时也实现了较好的时序、面积结果。

目前该芯片已成功流片,实测的性能及功耗指标均达到预期效果,高速总线时钟频率可达110M,normal功耗模式下算法模块全速工作时功耗小于380mW,sleep功耗模式下功耗11mW左右。

感谢Magma公司在物理实现方面持续的努力和进步,使得用户能够在设计中体会到革新所带来的便捷与快乐。在此,希望Magma今后能够不断革新,给用户带来更多的方便,分享更多的成功。

SoC CMOS EDA USB Mentor Cadence 电子 电压 电路 总线 仿真 相关文章:

- 统一功率格式降低SoC的功耗(05-28)

- 第三方IP:SoC设计的一种不稳固基础(09-15)

- 赛普拉斯智能照明解决方案支持欧司朗 DRAGON LED 以精简照明设计流程(11-26)

- 基于改进的遗传算法软硬件划分方法研究(07-20)

- 锂电池均衡处理技术解决SOC和C/E失配问题(06-28)

- PSoC3应用于多通讯接口时的DMA设计 (03-05)