一种SoC芯片在Magma Talus下的物理实现

时间:11-10

来源:互联网

点击:

本文介绍了一种SoC芯片架构,及其在0.18um CMOS工艺上以talus为主导EDA工具的物理实现。该芯片包含41个时钟域,4种低功耗工作模式,2个相互隔离的1.8v内部电源域,约有65万个标准单元,94个宏模块,250个pad,合计约900万个逻辑等效门,3600万个晶体管,芯片面积10.5mmx10.5mm。

关键字索引: 约束设计、布局规划、时钟树设计

第一章 芯片结构及物理实现流程介绍

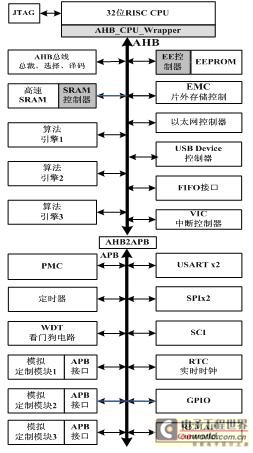

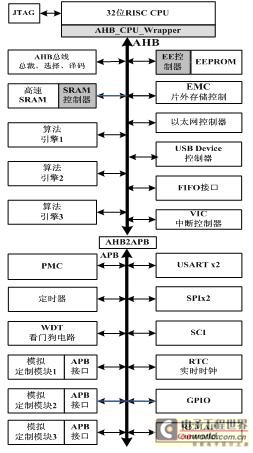

该芯片主要由32位处理器、静态随机存储器、以太网MAC接口、SPI接口、USB1.1 Device接口、USART同异步通信接口、SCI智能卡接口、片外存储器控制器等模块组成。该芯片具备高处理能力、低功耗等特点。其结构框图如图1所示:

图1 SoC芯片的结构框图

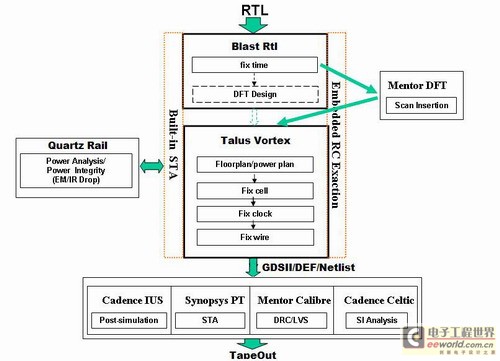

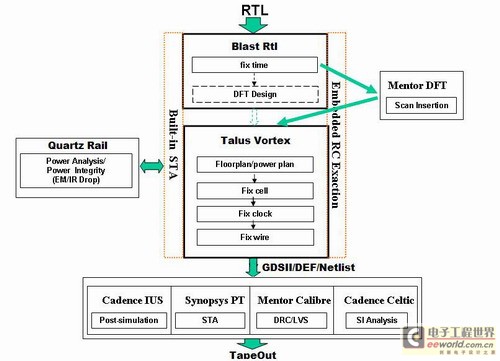

我们采用以Magma工具为主,Mentor、Cadence、Synopsys工具为辅的工具套件来完成RTL2GDSII的整个后端流程,如图2所示:

图2 SoC后端实现流程

逻辑实现阶段:用Magma Blast Rtl 来进行逻辑综合,综合完成后利用Mentor DFT进行扫描链的插入。

某算法模块在进行物理综合时,无论采取何种措施(包括优化宏模块位置,添加blockage,加大库单元的outline尺寸等),std cell 部分的Congestion都很严重,如图3所示。而采用Magma Blast Rtl进行逻辑综合,再采用Magma Talus Vortex来进行物理综合时,std cell部分的congestion可以消除。

图3 某算法模块congestion图

物理实现阶段:用Magma Talus Vortex来进行布局规划和电源网络规划、物理综合、时钟树插入及布线工作。

在整个实现过程中,我们采用Magma工具内嵌的静态时序分析引擎和RC参数提取引擎来进行MMMC(Multi-Mode Multi-Corner,多模式多功能角)时序分析,参数提取,信号完整性的分析、避免和修复工作;使用Quartz Rail工具来进行功耗分析,以及包括电子迁移和电压降在内的电源完整性分析。

第二章 时序约束设计

本SoC芯片时序约束设计的关键在于功耗管理控制模块的时序约束。

2.1 功耗管理控制(Power Management Controller, PMC)模块简介

整个设计中首先考虑的是PMC模块的约束。PMC模块是系统用来控制系统功耗的的控制器,可以通过寄存器配置,使SoC芯片在不同工作模式之间进行切换:Slow、Normal、Idle 和Sleep。这些工作模式可以让用户根据芯片不同的应用,通过动态地管理芯片内部各子模块的时钟源供给和系统的工作频率来控制芯片的整体功耗。另外,PMC 还包含了各个子模块的初粒度的时钟门控电路,通过寄存器配置可以集中控制、关闭不必要打开的模块,从而达到降低功耗的目的。模块具有以下性能指标:

?内置锁相环、可动态变频;

? 支持Slow、Normal、Idle、Sleep等4种工作模式;

? 支持模块工作时钟集中控制策略,芯片各模块的时钟可以通过PMC来关闭和打开;

? 低功耗sleep模式下支持DRAM/SDRAM 的数据自刷新,使得DRAM 中的数据可以得到保持;

? 内部具有完整的reset 解决方案,提供3 种reset 选择:hard reset、soft reset、watchdog reset;

? 内部具有完整的唤醒功能。

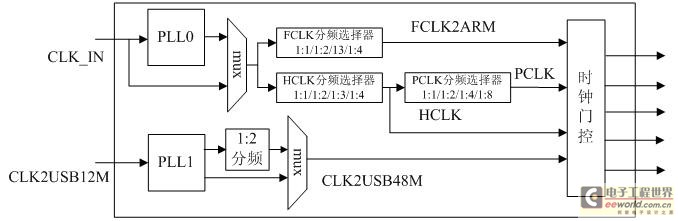

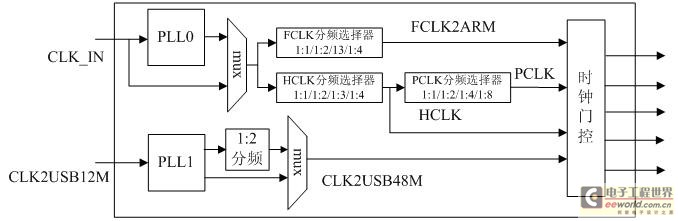

PMC模块包含了异步时钟动态选择电路、同步时钟动态选择电路、时钟分频电路、时钟门控电路、跨时钟域电路,既存在输入时钟,又存在输出时钟,是一个与时钟高度相关、时序违例集中、时序分析较为复杂的电路。PMC模块的时钟生成电路结构示意图如图4所示:

图4 时钟生成图

系统时钟经过可配置参数的系统PLL和动态选择逻辑后分频(有1:1、1:2、1:3、1:4四种)。选择默认的2分频为CPU 提供时钟,动态选择默认的3分频为高速总线提供时钟,高速总线时钟通过分频后(有1:1、1:2、1:4、1:8四种),动态选择默认的2分频为低速总线提供时钟。

2.2 时序约束的一些策略

一个完整的时序约束文件包含时钟的创建、时钟的约束、输入输出端口的约束及时序违例等。SDC格式的约束可以采用丰富的语法表达出上述内容。而Magma后端工具可以比较容易地识别出该格式的约束。我们采用SDC v1.7格式编写时序约束,这样既能为后端实现工具blast、talus识别,又能被静态时序分析工具PrimeTime识别。

首先根据设计规格要求确定时钟周期,在整个后端设计过程中的不同阶段加以调整和修改。为保守计,我们采取冗余设计,最终设定的周期值比规格要求的值严格。Clock latency和clock skew的设置也要根据实际的时钟树结构不断地进行调整和修改。最终合理的时序约束文件是经过反复地实验不断地修正而得到的。

复杂的时钟,复杂的功能模式,必然带来复杂的时序约束。对其正确、完备的约束施加,是保证后端设计时序分析和优化有效的关键所在。

而PMC模块的主要电路,如时钟门控电路、分频电路,动态选择电路等,采用例化的标准单元以网表的形式直接给出,在用Magma Blast Rtl进行逻辑综合前,将这些以网表形式存在的单元使用force keep命令,保证时序约束施加点的固定。

在Fix Time前设置时序约束时,采用的方法是3分频PLL后的源时钟作为高速总线上的时钟,低速总线时钟与高速总线时钟频率一致,这样在逻辑综合阶段时因为还没有真正的时钟树,而设置的约束又比较保守,使综合结果的时序有较大的冗余,又加快了综合的速度。

在时钟树优化时,采用MMMC来进行。我们仅以功耗模式中Normal模式里的两种在应用时较常用的时钟使用模式来设置MMMC:一种是3分频PLL后的源时钟作为高速总线上的时钟,低速总线时钟是高速总线时钟的2分频;另外一种模式是使用 1分频PLL后的源时钟作为高速总线时钟,低速总线时钟与高速总线时钟频率及PLL后的源时钟频率一致,此时低速总线时钟频率高于前一种模式下的时钟频率,达到低速总线上模块能达到的最高频率。其他模式仅用来分析及优化。这样可以有效加速时钟树创建的时间及分析效率。

在约束设计过程中,不可避免的会涉及到各种模式下时钟间异步关系的设置,我们采用SDC v1.7里面的set_clock_group命令来进行,该命令能有效的表征各个时钟之间的异步关系,避免了set_false_path繁琐的设置,并且能够被Magma Talus软件转换为force timing clockgroups命令。下面是该设计中的两个clock group设置的例子:

set_clock_group -name func_async_ck1 -logically_exclusive \

-group [get_clocks "fck2_n"] \

-group [get_clocks "hck3_n hck2anu3_n"] \

-group [get_clocks "hck2anu4_n"]

set_clock_group -name func_async_ck2 -asynchronous \

-group [get_clocks "usb_dev_ck"] \

-group [get_clocks "usb_pll_ck"

另外分频时钟与源时钟关系的设置上,我们根据仿真波形来确定分频时钟与源时钟之间的相位关系,从而为create_generated_clock命令在-divide_by,-edges,-invert,-combinational间选择不同的选项,使分频时钟和源时钟之间的source latency关系很容易就能确定下来,简化了时序分析。 下面是该设计中几个分频时钟约束的例子:

create_generated_clock -name usb_dev_ck \

-divide_by 4 -invert \

-source [get_pins "…/OR2CLK_Inst/Z"] \

-master_clock [get_clocks "pllout48m"] -add \

[get_pins "…/clk_1x_reg/Q"]

create_generated_clock -name rngck8\

-edges "7 15 23" \

-source [get_pins "…/OR4CLK_Inst/Z"] \

-master_clock [get_clocks "pck_n"] -add \

[get_pins "…/CLK_CNT_reg/Q"]

create_generated_clock -name pck8_n \

-edges "3 11 19" \

-source [get_pins "…/OR4CLK_Inst/Z"] \

-master_clock [get_clocks "hck3_n"] -add \

[get_pins "…/PCLK_div8_reg/Q"]

create_generated_clock -name hck_out \

-combinational \

-source [get_pins "…/OR2CLK_Inst/Z"] \

-master_clock [get_clocks "hck3_n"] -add \

[get_ports "hclk"]

关键字索引: 约束设计、布局规划、时钟树设计

第一章 芯片结构及物理实现流程介绍

该芯片主要由32位处理器、静态随机存储器、以太网MAC接口、SPI接口、USB1.1 Device接口、USART同异步通信接口、SCI智能卡接口、片外存储器控制器等模块组成。该芯片具备高处理能力、低功耗等特点。其结构框图如图1所示:

图1 SoC芯片的结构框图

我们采用以Magma工具为主,Mentor、Cadence、Synopsys工具为辅的工具套件来完成RTL2GDSII的整个后端流程,如图2所示:

图2 SoC后端实现流程

逻辑实现阶段:用Magma Blast Rtl 来进行逻辑综合,综合完成后利用Mentor DFT进行扫描链的插入。

某算法模块在进行物理综合时,无论采取何种措施(包括优化宏模块位置,添加blockage,加大库单元的outline尺寸等),std cell 部分的Congestion都很严重,如图3所示。而采用Magma Blast Rtl进行逻辑综合,再采用Magma Talus Vortex来进行物理综合时,std cell部分的congestion可以消除。

图3 某算法模块congestion图

物理实现阶段:用Magma Talus Vortex来进行布局规划和电源网络规划、物理综合、时钟树插入及布线工作。

在整个实现过程中,我们采用Magma工具内嵌的静态时序分析引擎和RC参数提取引擎来进行MMMC(Multi-Mode Multi-Corner,多模式多功能角)时序分析,参数提取,信号完整性的分析、避免和修复工作;使用Quartz Rail工具来进行功耗分析,以及包括电子迁移和电压降在内的电源完整性分析。

第二章 时序约束设计

本SoC芯片时序约束设计的关键在于功耗管理控制模块的时序约束。

2.1 功耗管理控制(Power Management Controller, PMC)模块简介

整个设计中首先考虑的是PMC模块的约束。PMC模块是系统用来控制系统功耗的的控制器,可以通过寄存器配置,使SoC芯片在不同工作模式之间进行切换:Slow、Normal、Idle 和Sleep。这些工作模式可以让用户根据芯片不同的应用,通过动态地管理芯片内部各子模块的时钟源供给和系统的工作频率来控制芯片的整体功耗。另外,PMC 还包含了各个子模块的初粒度的时钟门控电路,通过寄存器配置可以集中控制、关闭不必要打开的模块,从而达到降低功耗的目的。模块具有以下性能指标:

?内置锁相环、可动态变频;

? 支持Slow、Normal、Idle、Sleep等4种工作模式;

? 支持模块工作时钟集中控制策略,芯片各模块的时钟可以通过PMC来关闭和打开;

? 低功耗sleep模式下支持DRAM/SDRAM 的数据自刷新,使得DRAM 中的数据可以得到保持;

? 内部具有完整的reset 解决方案,提供3 种reset 选择:hard reset、soft reset、watchdog reset;

? 内部具有完整的唤醒功能。

PMC模块包含了异步时钟动态选择电路、同步时钟动态选择电路、时钟分频电路、时钟门控电路、跨时钟域电路,既存在输入时钟,又存在输出时钟,是一个与时钟高度相关、时序违例集中、时序分析较为复杂的电路。PMC模块的时钟生成电路结构示意图如图4所示:

图4 时钟生成图

系统时钟经过可配置参数的系统PLL和动态选择逻辑后分频(有1:1、1:2、1:3、1:4四种)。选择默认的2分频为CPU 提供时钟,动态选择默认的3分频为高速总线提供时钟,高速总线时钟通过分频后(有1:1、1:2、1:4、1:8四种),动态选择默认的2分频为低速总线提供时钟。

2.2 时序约束的一些策略

一个完整的时序约束文件包含时钟的创建、时钟的约束、输入输出端口的约束及时序违例等。SDC格式的约束可以采用丰富的语法表达出上述内容。而Magma后端工具可以比较容易地识别出该格式的约束。我们采用SDC v1.7格式编写时序约束,这样既能为后端实现工具blast、talus识别,又能被静态时序分析工具PrimeTime识别。

首先根据设计规格要求确定时钟周期,在整个后端设计过程中的不同阶段加以调整和修改。为保守计,我们采取冗余设计,最终设定的周期值比规格要求的值严格。Clock latency和clock skew的设置也要根据实际的时钟树结构不断地进行调整和修改。最终合理的时序约束文件是经过反复地实验不断地修正而得到的。

复杂的时钟,复杂的功能模式,必然带来复杂的时序约束。对其正确、完备的约束施加,是保证后端设计时序分析和优化有效的关键所在。

而PMC模块的主要电路,如时钟门控电路、分频电路,动态选择电路等,采用例化的标准单元以网表的形式直接给出,在用Magma Blast Rtl进行逻辑综合前,将这些以网表形式存在的单元使用force keep命令,保证时序约束施加点的固定。

在Fix Time前设置时序约束时,采用的方法是3分频PLL后的源时钟作为高速总线上的时钟,低速总线时钟与高速总线时钟频率一致,这样在逻辑综合阶段时因为还没有真正的时钟树,而设置的约束又比较保守,使综合结果的时序有较大的冗余,又加快了综合的速度。

在时钟树优化时,采用MMMC来进行。我们仅以功耗模式中Normal模式里的两种在应用时较常用的时钟使用模式来设置MMMC:一种是3分频PLL后的源时钟作为高速总线上的时钟,低速总线时钟是高速总线时钟的2分频;另外一种模式是使用 1分频PLL后的源时钟作为高速总线时钟,低速总线时钟与高速总线时钟频率及PLL后的源时钟频率一致,此时低速总线时钟频率高于前一种模式下的时钟频率,达到低速总线上模块能达到的最高频率。其他模式仅用来分析及优化。这样可以有效加速时钟树创建的时间及分析效率。

在约束设计过程中,不可避免的会涉及到各种模式下时钟间异步关系的设置,我们采用SDC v1.7里面的set_clock_group命令来进行,该命令能有效的表征各个时钟之间的异步关系,避免了set_false_path繁琐的设置,并且能够被Magma Talus软件转换为force timing clockgroups命令。下面是该设计中的两个clock group设置的例子:

set_clock_group -name func_async_ck1 -logically_exclusive \

-group [get_clocks "fck2_n"] \

-group [get_clocks "hck3_n hck2anu3_n"] \

-group [get_clocks "hck2anu4_n"]

set_clock_group -name func_async_ck2 -asynchronous \

-group [get_clocks "usb_dev_ck"] \

-group [get_clocks "usb_pll_ck"

另外分频时钟与源时钟关系的设置上,我们根据仿真波形来确定分频时钟与源时钟之间的相位关系,从而为create_generated_clock命令在-divide_by,-edges,-invert,-combinational间选择不同的选项,使分频时钟和源时钟之间的source latency关系很容易就能确定下来,简化了时序分析。 下面是该设计中几个分频时钟约束的例子:

create_generated_clock -name usb_dev_ck \

-divide_by 4 -invert \

-source [get_pins "…/OR2CLK_Inst/Z"] \

-master_clock [get_clocks "pllout48m"] -add \

[get_pins "…/clk_1x_reg/Q"]

create_generated_clock -name rngck8\

-edges "7 15 23" \

-source [get_pins "…/OR4CLK_Inst/Z"] \

-master_clock [get_clocks "pck_n"] -add \

[get_pins "…/CLK_CNT_reg/Q"]

create_generated_clock -name pck8_n \

-edges "3 11 19" \

-source [get_pins "…/OR4CLK_Inst/Z"] \

-master_clock [get_clocks "hck3_n"] -add \

[get_pins "…/PCLK_div8_reg/Q"]

create_generated_clock -name hck_out \

-combinational \

-source [get_pins "…/OR2CLK_Inst/Z"] \

-master_clock [get_clocks "hck3_n"] -add \

[get_ports "hclk"]

SoC CMOS EDA USB Mentor Cadence 电子 电压 电路 总线 仿真 相关文章:

- 统一功率格式降低SoC的功耗(05-28)

- 第三方IP:SoC设计的一种不稳固基础(09-15)

- 赛普拉斯智能照明解决方案支持欧司朗 DRAGON LED 以精简照明设计流程(11-26)

- 基于改进的遗传算法软硬件划分方法研究(07-20)

- 锂电池均衡处理技术解决SOC和C/E失配问题(06-28)

- PSoC3应用于多通讯接口时的DMA设计 (03-05)