用0.18um CMOS设计2.5Gb/s收发器的复用器电路

时间:10-31

来源:互联网

点击:

1 引言

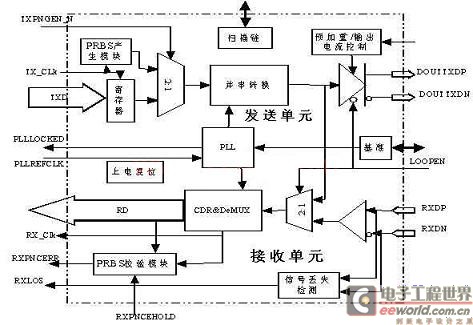

近年来,随着传统电信业务和互联网业务的迅猛发展,它们对网络带宽提出了越来越高的要求,由此导致了高速串行接口的出现。目前国内关于2.5 Gb/s超高速串行收发器CMOS芯片及IP核研究开发尚处于起步阶段。设计开发具有自主知识产权的高性能串行收发器芯片及IP核,打破国外对高端路由器、交换器芯片的垄断,不仅能够直接大幅度降低通信、网络设备成本,产生显著的经济效益,还能带来巨大的社会效益。本文所设计的复用器,应用在2.5Gb/s收发器系统中,该收发器的系统框图如图1所示。

众所周知在高速的数据传输系统中,收发器对于实现整个系统的功能起着至关重要的作用。而在收发器系统中,复用器是工作在最高速度的电路单元之一,因此复用器电路设计的好坏直接影响整个系统的性能。本文所设计的复用器,采用SMIC 0.18μm CMOS工艺实现。

2 电路结构及其设计

2.1 16:1复用器结构设计

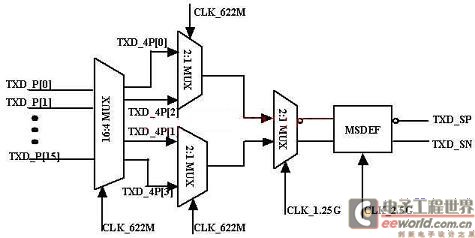

本文设计的16:1复用器是将发送数据选择模块输出的16位156.25Mb/s并行数据转换为2.5Gb/s串行数据输出,其实现框图如图2所示,该电路主要由1个16:4复用器电路和1个采用树形结构(包括3个2:1复用器)实现的4:1的复用器电路构成。其中16:4复用器用数字电路实现,4:1复用器电路用模拟电路实现。该电路接收从PLL送出的2.5GHz、1.25GHz和625MHz差分时钟,为16:4复用器和2:1复用器电路提供所需要的时钟。16位并行输入数据经过16:4复用器后输出4位并行数据送入4:1复用器,经4:1复用器后,数据变换成1比特宽度的串行数据流,发送顺序最低位在前,即TXD_P[0]最先出现在TXD_S上,TXD_P[15]最后发出。由于本电路是数模混合信号设计,仿真时需要给数字电路和模拟电路分别加激励,对于4:1复用器电路,输入采用互补的方波电压源,峰峰值为0.4V。对于16:4复用器电路,通过用Verilog语言描述的方式加激励。由于两个模块分别用数字电路和模拟电路实现,因此在两个模块的连接处要进行电平的转换。

Virtuoso AMS Simulator中将接口模型划分为A2D型和D2A型两类。本设计是由数字电路送信号给模拟电路,因此要用到D2A接口模型,该模型主要有4个参数:d2a_tf,d2a_tr,d2a_vh和d2a_vl。其中d2a_tf和d2a_tr分别表示接口模型的输出从当前值上升到d2a_vh所需要的时间和下降到d2a_vl所需要的时间;d2a_vh和d2a_vl分别表示对应数字电路中的逻辑“1”和“0”而转换成的最终电压值。本设计的设置如下: d2a_tf=20ps, d2a_tr=20ps,d2a_vh=1.8V,d2a_vl=1.4V。

2.2 单元电路设计

2.2.1 16:4复用器电路

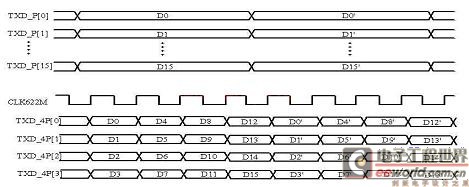

16:4复用器电路由4个4:1复用器模块和一个赋值语句模块构成,本电路均采用Verilog语言来描述。4个4:1复用器的作用是将16路156.25M数据TXD_P[15:0]复用为4路625M数据,这里我们用移位寄存器实现4:1复用器。首先将16位并行数据,分为四个4位并行数据,然后将4位并行数据送入4:1复用器,数据经过4位移位寄存器后的输出如图3所示。由于后级的模拟电路需要差分输入,因此本模块输出均为互补输出。

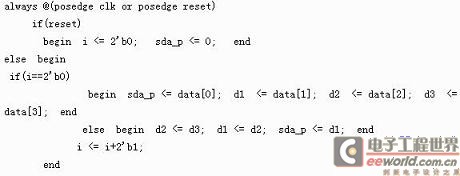

4:1复用器电路的Verilog实现的关键代码如下:

2.2.2 4:1复用器电路

4:1复用器采用树形结构实现,其实现如图2所示,它主要由三个2:1的高速复用器和一个主从D触发器(MSDEF)构成。2:1复用器由一个主从D触发器(由两个锁存器级连构成),一个主从主D触发器(由三个锁存器级连构成)和一个2:1数据选择器构成。

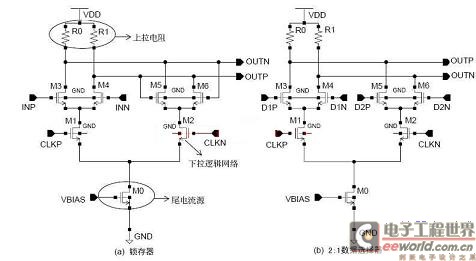

本文所设计的锁存器和2:1数据选择器均采用CML(电流模式逻辑)逻辑实现,其基本结构如图4(a)所示,按其功能可分为下拉逻辑网络、尾电流源和上拉电阻三个部分。它可以在电压摆幅较小的情况下正常工作。由于尾电流源的存在,CML电路的功耗近似为恒定值P=vdd*I,其中vdd是电源电压,I为直流尾电流。众所周知,传统CMOS电路的功耗为P=CL`*f*vdd2,其中f是电路的开关频率,CL`是输出节点的负载电容。因此,在高速率的条件下,CML电路的功耗比与其相似的CMOS电路的功耗要小得多。此外,降低CML电路的电压摆幅,还可以减小整个电路的延时,从而提高电路的工作速度。

3 仿真结果

该电路采用SMIC 0.18μm工艺模型,使用Virtuoso AMS Simulator 工具进行了仿真。输入信号为16位156.25Mb/s并行数据,如图5(a)所示。仿真的corner包括:ff(fast model)、tt(typical model)、ss(slow model)。不同corner下的仿真输出波形如图5(b)-(d)所示。从仿真的结果可以看出,输入数据为156.25Mb/s时,能较好的实现复用功能,输出数据速率为2.5Gb/s,整个电路的功耗约为6mW。

图5 不同corner下的仿真波形

近年来,随着传统电信业务和互联网业务的迅猛发展,它们对网络带宽提出了越来越高的要求,由此导致了高速串行接口的出现。目前国内关于2.5 Gb/s超高速串行收发器CMOS芯片及IP核研究开发尚处于起步阶段。设计开发具有自主知识产权的高性能串行收发器芯片及IP核,打破国外对高端路由器、交换器芯片的垄断,不仅能够直接大幅度降低通信、网络设备成本,产生显著的经济效益,还能带来巨大的社会效益。本文所设计的复用器,应用在2.5Gb/s收发器系统中,该收发器的系统框图如图1所示。

图1 Transceiver结构示意图

众所周知在高速的数据传输系统中,收发器对于实现整个系统的功能起着至关重要的作用。而在收发器系统中,复用器是工作在最高速度的电路单元之一,因此复用器电路设计的好坏直接影响整个系统的性能。本文所设计的复用器,采用SMIC 0.18μm CMOS工艺实现。

2 电路结构及其设计

2.1 16:1复用器结构设计

本文设计的16:1复用器是将发送数据选择模块输出的16位156.25Mb/s并行数据转换为2.5Gb/s串行数据输出,其实现框图如图2所示,该电路主要由1个16:4复用器电路和1个采用树形结构(包括3个2:1复用器)实现的4:1的复用器电路构成。其中16:4复用器用数字电路实现,4:1复用器电路用模拟电路实现。该电路接收从PLL送出的2.5GHz、1.25GHz和625MHz差分时钟,为16:4复用器和2:1复用器电路提供所需要的时钟。16位并行输入数据经过16:4复用器后输出4位并行数据送入4:1复用器,经4:1复用器后,数据变换成1比特宽度的串行数据流,发送顺序最低位在前,即TXD_P[0]最先出现在TXD_S上,TXD_P[15]最后发出。由于本电路是数模混合信号设计,仿真时需要给数字电路和模拟电路分别加激励,对于4:1复用器电路,输入采用互补的方波电压源,峰峰值为0.4V。对于16:4复用器电路,通过用Verilog语言描述的方式加激励。由于两个模块分别用数字电路和模拟电路实现,因此在两个模块的连接处要进行电平的转换。

Virtuoso AMS Simulator中将接口模型划分为A2D型和D2A型两类。本设计是由数字电路送信号给模拟电路,因此要用到D2A接口模型,该模型主要有4个参数:d2a_tf,d2a_tr,d2a_vh和d2a_vl。其中d2a_tf和d2a_tr分别表示接口模型的输出从当前值上升到d2a_vh所需要的时间和下降到d2a_vl所需要的时间;d2a_vh和d2a_vl分别表示对应数字电路中的逻辑“1”和“0”而转换成的最终电压值。本设计的设置如下: d2a_tf=20ps, d2a_tr=20ps,d2a_vh=1.8V,d2a_vl=1.4V。

图2 16:1复用器实现框图

2.2 单元电路设计

2.2.1 16:4复用器电路

16:4复用器电路由4个4:1复用器模块和一个赋值语句模块构成,本电路均采用Verilog语言来描述。4个4:1复用器的作用是将16路156.25M数据TXD_P[15:0]复用为4路625M数据,这里我们用移位寄存器实现4:1复用器。首先将16位并行数据,分为四个4位并行数据,然后将4位并行数据送入4:1复用器,数据经过4位移位寄存器后的输出如图3所示。由于后级的模拟电路需要差分输入,因此本模块输出均为互补输出。

图3 16:4复用器实现时序图

4:1复用器电路的Verilog实现的关键代码如下:

2.2.2 4:1复用器电路

4:1复用器采用树形结构实现,其实现如图2所示,它主要由三个2:1的高速复用器和一个主从D触发器(MSDEF)构成。2:1复用器由一个主从D触发器(由两个锁存器级连构成),一个主从主D触发器(由三个锁存器级连构成)和一个2:1数据选择器构成。

本文所设计的锁存器和2:1数据选择器均采用CML(电流模式逻辑)逻辑实现,其基本结构如图4(a)所示,按其功能可分为下拉逻辑网络、尾电流源和上拉电阻三个部分。它可以在电压摆幅较小的情况下正常工作。由于尾电流源的存在,CML电路的功耗近似为恒定值P=vdd*I,其中vdd是电源电压,I为直流尾电流。众所周知,传统CMOS电路的功耗为P=CL`*f*vdd2,其中f是电路的开关频率,CL`是输出节点的负载电容。因此,在高速率的条件下,CML电路的功耗比与其相似的CMOS电路的功耗要小得多。此外,降低CML电路的电压摆幅,还可以减小整个电路的延时,从而提高电路的工作速度。

图4 锁存器及2:1数据选择器电路图

3 仿真结果

该电路采用SMIC 0.18μm工艺模型,使用Virtuoso AMS Simulator 工具进行了仿真。输入信号为16位156.25Mb/s并行数据,如图5(a)所示。仿真的corner包括:ff(fast model)、tt(typical model)、ss(slow model)。不同corner下的仿真输出波形如图5(b)-(d)所示。从仿真的结果可以看出,输入数据为156.25Mb/s时,能较好的实现复用功能,输出数据速率为2.5Gb/s,整个电路的功耗约为6mW。

图5 不同corner下的仿真波形

收发器 CMOS 电路 模拟电路 仿真 电压 Verilog 电流 电阻 电容 电路图 相关文章:

- 采用0.18um CMOS设计用于2.5Gb/s收发器系统的16:1复用器电路(09-15)

- RS-485自收发电路的参考设计(01-20)

- 利用电荷泵为高速CAN收发器供电(02-23)

- 信号链基础知识 RS-485:总线电流要求与收发器驱动能力(04-27)

- 压控振荡器(VCO)的设计(03-25)

- 基于LPC2119的配电控制模块设计(02-27)