一种应用于SoC的高速数模转换器的设计

时间:10-28

来源:互联网

点击:

3 仿真结果

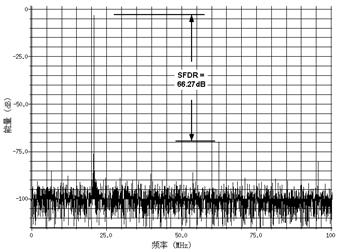

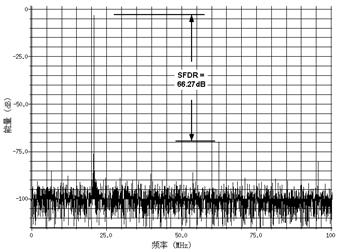

本文的DAC设计在SMIC 0.18μm CMOS工艺下实现,使用Cadence的Spectre软件进行仿真。仿真结果表明,该DAC的最高采样率可达到300MS/s(所有corner最坏情况)。在200MS/s采样率、20.8MHz输入信号条件下(1.8V电源电压、TT corner),DAC的输出信号的频谱如图4所示。从图中可以看到,此时DAC的SFDR可以达到66.27dB,这一数值也接近所有corner下SFDR的平均结果。在SS corner下DAC的SFDR最低,但也超过了60dB。

Monte Carlo仿真表明,该DAC的INL和DNL均小于0.5LSB的百分比大于99%。该DAC的电源电压为1.8V,最大输出电压为1.5Vpp(差分),在采样率为200MS/s时功耗仅为22.7mW,IP硬核的面积约为0.55mm2。

图4 200MS/s采样率、20.8MHz输入信号下DAC的输出频谱(TT corner)

4 结论

本文提出了一种应用于SoC的高速高精度DAC的设计,并在深亚微米CMOS工艺下实现了IP硬核形式的设计。该设计在高速条件下具有良好的性能,且功耗与面积都较小,能够有效满足通信、测量、自动控制、多媒体等领域的SoC系统设计的应用需求。

本文作者创新点:

通过采用同步电路设计原则以及自动综合与布局布线的设计方法,实现了高速的温度计码译码电路。通过改进开关单元以及合理设计共源共栅电流源的尺寸,保证了DAC良好的线性度以及在高速条件下的良好性能。

本文的DAC设计在SMIC 0.18μm CMOS工艺下实现,使用Cadence的Spectre软件进行仿真。仿真结果表明,该DAC的最高采样率可达到300MS/s(所有corner最坏情况)。在200MS/s采样率、20.8MHz输入信号条件下(1.8V电源电压、TT corner),DAC的输出信号的频谱如图4所示。从图中可以看到,此时DAC的SFDR可以达到66.27dB,这一数值也接近所有corner下SFDR的平均结果。在SS corner下DAC的SFDR最低,但也超过了60dB。

Monte Carlo仿真表明,该DAC的INL和DNL均小于0.5LSB的百分比大于99%。该DAC的电源电压为1.8V,最大输出电压为1.5Vpp(差分),在采样率为200MS/s时功耗仅为22.7mW,IP硬核的面积约为0.55mm2。

图4 200MS/s采样率、20.8MHz输入信号下DAC的输出频谱(TT corner)

4 结论

本文提出了一种应用于SoC的高速高精度DAC的设计,并在深亚微米CMOS工艺下实现了IP硬核形式的设计。该设计在高速条件下具有良好的性能,且功耗与面积都较小,能够有效满足通信、测量、自动控制、多媒体等领域的SoC系统设计的应用需求。

本文作者创新点:

通过采用同步电路设计原则以及自动综合与布局布线的设计方法,实现了高速的温度计码译码电路。通过改进开关单元以及合理设计共源共栅电流源的尺寸,保证了DAC良好的线性度以及在高速条件下的良好性能。

SoC 集成电路 电路 DAC CMOS 电流 Verilog 仿真 电路图 电压 Cadence 相关文章:

- 统一功率格式降低SoC的功耗(05-28)

- 第三方IP:SoC设计的一种不稳固基础(09-15)

- 赛普拉斯智能照明解决方案支持欧司朗 DRAGON LED 以精简照明设计流程(11-26)

- 基于改进的遗传算法软硬件划分方法研究(07-20)

- 锂电池均衡处理技术解决SOC和C/E失配问题(06-28)

- PSoC3应用于多通讯接口时的DMA设计 (03-05)