帧同步电路的设计

时间:10-26

来源:互联网

点击:

3.3 调整单元

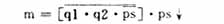

该单元在检测到q1=1后,就进入待调整状态。在进行调整后,将输出一个调整指令。产生调整指令的逻辑关系可表示为:

图5为调整单元波形。在q1=1时,即系统失步时,调整单元开始进入工作状态。在该状态下,如果检测到pc与ps不同步,则通过pc的上升沿把状态量q2置为高电平并保持,即q2=1。在q1=1,q2=1的情况下,当检测到下一个ps脉冲时,ps的下降沿会触发产生一个置位负脉冲m=0;并在时钟信号的控制下,m延时半个系统时钟周期后重新将置位脉冲恢复为高电平m=1。该置位脉冲用于帧时标发生单元复位。

3.4 帧时标发生单元

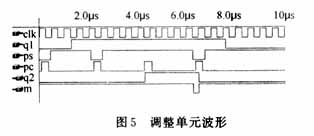

? 该单元的功能是定时的产生帧时标pc,每个相邻pc的间隔时间为一个帧周期。实现该功能就是将系统时钟计数分频,计数周期值为一个帧的长度,每隔一个帧周期就产生一个pc脉冲,脉冲宽度为一个时钟周期。在帧时标发生单元检测到一个低电平的复位脉冲时,计数器复位清零并重新开始计数。波形如图6所示。图中clr为复位清零端;clk为系统时钟;pc是发生器产生的帧时标。

3.5 同步单元的整体设计

我们用VHDL设计完成各模块,并在MaxPlusII开发软件上编译通过,其设计波形分别已做说明。在MaxPlusII开发软件上采用原理图输入方式,根据同步单元各个功能块的划分,将各个功能模块连接起来,同步单元设计如图7所示。

图中,ZJC模块是帧定位码检测单元;PCFS模块是帧时标发生单元;SBBJ模块是同步保护及校核单元;TZ模块是调整单元。输入端pcm为合路信号码流,clk为系统时钟;输出端中pc为所需要的帧时标,其他的输出为同步单元的一些状态参考量, q1指示了系统所处的状态是同步还是失步;ps是检测到帧同步码后产生的同步时标;m为调整单元的调整指令。

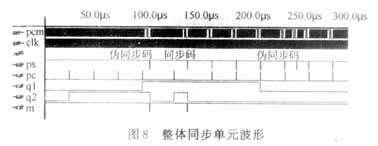

图8是整体设计在MaxPlusII软件中的波形图。在第1个帧时标pc脉冲出现时没有同步时标ps脉冲,则状态量q2=1。该同步系统的前方保护系数β=4,在连续4个帧时标pc脉冲与同步时标ps脉冲不同步后,状态量q1=1。当q1,q2同时为高电平时,该系统进入搜捕状态。由于在下一个pc脉冲出现前,该系统检测到了一个同步时标(该时标为伪同步码产生的),马上输出调整指令脉冲m=0。此时,帧时标pc脉冲发生器被置位,重新开始计数;状态量恢复为q2=0。再经过一个帧周期,出现了置位后产生的第一个帧时标pc脉冲,因为没有出现同步时标ps脉冲,则q2=1。此后,又重新搜捕。当搜捕到同步码后,如果出现帧时标pc脉冲与同步时标ps脉冲连续3次同步(后方保护系数α=3),则表示捕捉成功,系统重新进入同步状态。图中,在恢复到同步态后出现了一个伪同步码,由于采取了保护措施(连续4个帧时标pc脉冲与同步时标ps脉冲不同步时,才判为失步),因此他没有影响系统的正常工作。

4 结语

置位调整法是帧同步电路设计中通常采用的方法,为降低系统的漏检概率和虚警概率,设计中采用前方保护和后方保护。同步系统各模块全部用VHDL编程实现,整体设计在MaxPlusII软件中调试通过。

- 整流电路(11-30)

- 单运放构成的单稳延时电路(11-29)

- 直流稳压电源电路(11-30)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 为太阳能灯供电的低损耗电路的设计(01-22)