24位高性能模数转换器ADS1274/ADS1278及其应用

时间:10-23

来源:互联网

点击:

1 概述

ADS1274/ADS1278是德州仪器(TI)推出的多通道24位工业模数转换器(ADC),内部集成有多个独立的高阶斩波稳定调制器和FIR数字滤波器,可实现4/8通道同步采样,支持高速、高精度、低功耗、低速4种工作模式;ADS1274/ADS1278具有优良的AC和DC特性,采样率最高可以达128 Ks/s,62 kHz带宽时信噪比(SNR)可达111 dB,失调漂移为0.8μV/℃。

ADS1274/ADS1278可通过设置相应的输入/输出引脚选择工作模式,无需寄存器编程,其数据输出可选帧同步或SPI串行接口,便于连接至DSP、FPGA及微控制器。每个接口均支持菊花链,简化多通道计数系统中的多个ADS1274或ADS1278的回读功能(readback)。ADS1274工作温度范围为-40℃~+125℃,ADS1278则为-40℃~+105℃,可满足要求严格的多通道信号采集应用,包括振动分析、医疗监控、声学/动态应变测量及压力测量设备等。

2 性能特点

传统的具有较高漂移性能的工业△-∑ADC采用导通带宽滑落幅度很大的数字滤波器,来得尽可能满足DC测量需求的有限信号带宽。针对音频应用的高分辨率ADC能够提供更大的可用带宽,但偏移与漂移规范远低于工业ADC。ADS1274/ADS1278将两种类型的转换器相结合,实现最佳DC与AC规范的高精度工业测量。具体特点如下:

允许4/8通道同步采样;

采样率最高可达128 Ks/s;

AC性能:工作在高精度模式下,输入信号带宽为62 kHz时,SNR为111 dB,总谐波失真(THD)为-108 dB;

DC性能:0.8μV/℃失调漂移,1.3 ppm/℃增益漂移;

4种可选工作模式:高速模式为128 Ks/s,信噪比106 dB;高精度模式为52 Ks/s,信噪比111 dB;低功耗模式为52 ks/s,31 mW/通道;而低速模式为10 ks/s,7 mW/通道;

片上线性相位数字滤波器;

SPI或帧同步串行接口;

低采样孔径误差;

调制器输出选择。

3 引脚功能说明

ADS1274/1278均采用64引脚HTQFP封装,两者引脚兼容以便于扩展,引脚功能说明如表1所示。

4 功能描述

4.1 工作原理

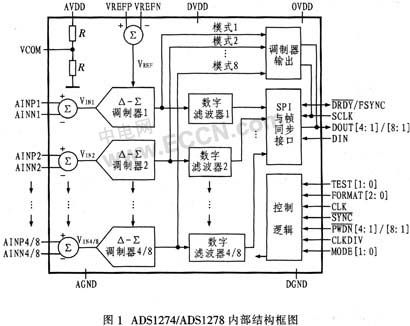

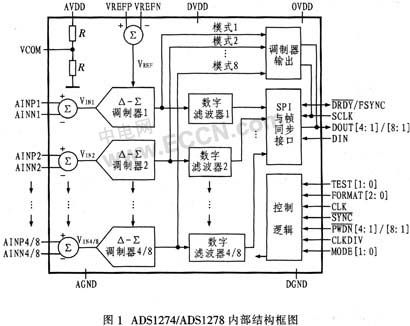

ADS1274/ADS1278是△-∑型模数转换器,其结构框图如图1所示,两者除内部所含模/数转换器(ADC)数目不同外,功能完全相同。它们主要由4/8个独立的ADC并行实现4/8通道输入信号的数字化,每个ADC由先进的6阶斩波、△-∑调制器,后接低纹波、线性相位的有限冲积响应(FIR)数字滤波器构成。调制器检测差分输入信号VIN=(AINP-AINN),并与差分参考电压VREF=(VREFP-VREFN)相比较得到一个1秒密度的位流输出,输出的位流经内部的数字滤波器滤波后得到一个低噪声的数字输出。

工作时调制器以高速采样输入信号(典型值输出数据率的64倍),调制器产生的量化噪声被移人高频带,由其内部的数字滤波器滤除,调制器的过采样倍率与工作模式有关,分别可取64(高速、低速、低功耗模式)或128(高精度模式),数字滤波器可对截止频率外的信号衰减达100 dB,使信号导通带宽在90%的奈奎斯特频率时,纹波低于0.005 dB。

4.2 工作模式设置

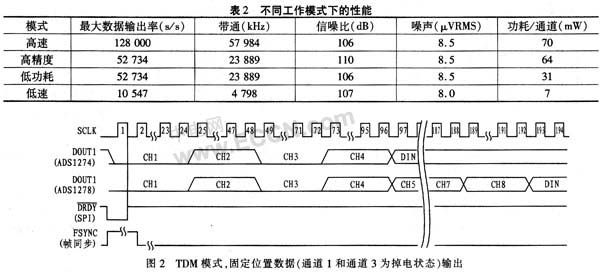

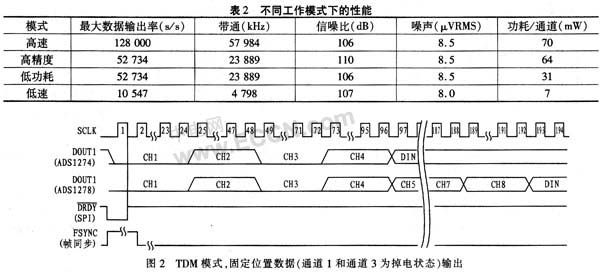

ADS1274/ADS1278允许在速度、精度、功耗方面权衡从4种工作模式中选择一种,各种工作模式下的性能如表2所示,而模式选择是由MODE[1:0]引脚的输入状态确定。

4.3 数据输出接口

ADS1274/ADS1278转换后的数据输出采用串行接口,可采用两种接口协议:SPI协议和帧同步协议,同时也可选择不同的数据输出格式,协议和数据输出格式的选择是由FORFMAT[2:0]引脚的输入状态确定。

对应SPI和帧同步接口协议,转换后的数据或通过独立的DOUT引脚以并行数据形式(离散模式)移位输出或通过一个共同的引脚DOUT1(TDM模式)移位输出。

在TDM数据输出模式中,多通道输出数据的位置有两种选择,即位置固定和位置动态分配。位置固定时,每个通道输出数据的位置严格按照顺序输出(即使某些通道掉电,也占有一个输出位置),动态分配时多通道输出数据的位置可根据通道使用情况随机调整,后续通道数据可占有前面掉电不用通道数据的位置,图2和图3描述了TDM模式时,固定位置和动态位置时的数据输出形式,表3列出接口协议、输出格式和数据位置关系。

5 应用接口电路

5.1 基本差分输入信号接口电路

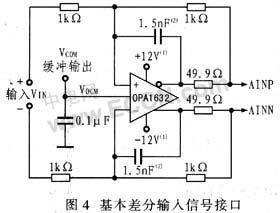

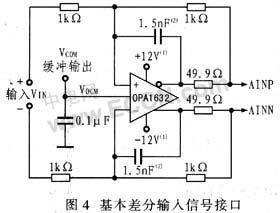

基本差分输入信号接口电路如图4所示,采用运算放大器OPA1632和RC构成的低通滤波器对输入信号进行调理,其中VCOM端可直接连接至ADC的VCOM引脚,也可通过OPA350缓冲输出,12 V电源可采用10μF和0.1μF的电容旁路,对于电容(2),当工作在低功耗模式时可选用2.7 nF的电容,在低速模式时则选用15 nF的电容。

5.2 ADS1724与TMS320的接口电路

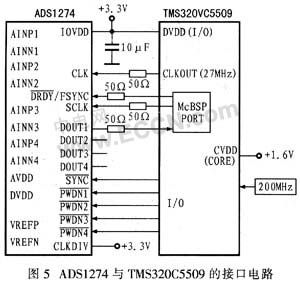

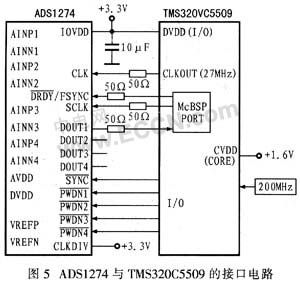

图5给出了ASD1274与TMS320VC5509的接口电路,ADS1274与TMS320VC5509之间采用帧同步串行接口,CLKdiv接3.3 V,采样主时钟频率为27 MHz,四路模拟输入信号可采用图4所示的连接接入AINP和AINN。

ADS1274/ADS1278是德州仪器(TI)推出的多通道24位工业模数转换器(ADC),内部集成有多个独立的高阶斩波稳定调制器和FIR数字滤波器,可实现4/8通道同步采样,支持高速、高精度、低功耗、低速4种工作模式;ADS1274/ADS1278具有优良的AC和DC特性,采样率最高可以达128 Ks/s,62 kHz带宽时信噪比(SNR)可达111 dB,失调漂移为0.8μV/℃。

ADS1274/ADS1278可通过设置相应的输入/输出引脚选择工作模式,无需寄存器编程,其数据输出可选帧同步或SPI串行接口,便于连接至DSP、FPGA及微控制器。每个接口均支持菊花链,简化多通道计数系统中的多个ADS1274或ADS1278的回读功能(readback)。ADS1274工作温度范围为-40℃~+125℃,ADS1278则为-40℃~+105℃,可满足要求严格的多通道信号采集应用,包括振动分析、医疗监控、声学/动态应变测量及压力测量设备等。

2 性能特点

传统的具有较高漂移性能的工业△-∑ADC采用导通带宽滑落幅度很大的数字滤波器,来得尽可能满足DC测量需求的有限信号带宽。针对音频应用的高分辨率ADC能够提供更大的可用带宽,但偏移与漂移规范远低于工业ADC。ADS1274/ADS1278将两种类型的转换器相结合,实现最佳DC与AC规范的高精度工业测量。具体特点如下:

允许4/8通道同步采样;

采样率最高可达128 Ks/s;

AC性能:工作在高精度模式下,输入信号带宽为62 kHz时,SNR为111 dB,总谐波失真(THD)为-108 dB;

DC性能:0.8μV/℃失调漂移,1.3 ppm/℃增益漂移;

4种可选工作模式:高速模式为128 Ks/s,信噪比106 dB;高精度模式为52 Ks/s,信噪比111 dB;低功耗模式为52 ks/s,31 mW/通道;而低速模式为10 ks/s,7 mW/通道;

片上线性相位数字滤波器;

SPI或帧同步串行接口;

低采样孔径误差;

调制器输出选择。

3 引脚功能说明

ADS1274/1278均采用64引脚HTQFP封装,两者引脚兼容以便于扩展,引脚功能说明如表1所示。

4 功能描述

4.1 工作原理

ADS1274/ADS1278是△-∑型模数转换器,其结构框图如图1所示,两者除内部所含模/数转换器(ADC)数目不同外,功能完全相同。它们主要由4/8个独立的ADC并行实现4/8通道输入信号的数字化,每个ADC由先进的6阶斩波、△-∑调制器,后接低纹波、线性相位的有限冲积响应(FIR)数字滤波器构成。调制器检测差分输入信号VIN=(AINP-AINN),并与差分参考电压VREF=(VREFP-VREFN)相比较得到一个1秒密度的位流输出,输出的位流经内部的数字滤波器滤波后得到一个低噪声的数字输出。

工作时调制器以高速采样输入信号(典型值输出数据率的64倍),调制器产生的量化噪声被移人高频带,由其内部的数字滤波器滤除,调制器的过采样倍率与工作模式有关,分别可取64(高速、低速、低功耗模式)或128(高精度模式),数字滤波器可对截止频率外的信号衰减达100 dB,使信号导通带宽在90%的奈奎斯特频率时,纹波低于0.005 dB。

4.2 工作模式设置

ADS1274/ADS1278允许在速度、精度、功耗方面权衡从4种工作模式中选择一种,各种工作模式下的性能如表2所示,而模式选择是由MODE[1:0]引脚的输入状态确定。

4.3 数据输出接口

ADS1274/ADS1278转换后的数据输出采用串行接口,可采用两种接口协议:SPI协议和帧同步协议,同时也可选择不同的数据输出格式,协议和数据输出格式的选择是由FORFMAT[2:0]引脚的输入状态确定。

对应SPI和帧同步接口协议,转换后的数据或通过独立的DOUT引脚以并行数据形式(离散模式)移位输出或通过一个共同的引脚DOUT1(TDM模式)移位输出。

在TDM数据输出模式中,多通道输出数据的位置有两种选择,即位置固定和位置动态分配。位置固定时,每个通道输出数据的位置严格按照顺序输出(即使某些通道掉电,也占有一个输出位置),动态分配时多通道输出数据的位置可根据通道使用情况随机调整,后续通道数据可占有前面掉电不用通道数据的位置,图2和图3描述了TDM模式时,固定位置和动态位置时的数据输出形式,表3列出接口协议、输出格式和数据位置关系。

5 应用接口电路

5.1 基本差分输入信号接口电路

基本差分输入信号接口电路如图4所示,采用运算放大器OPA1632和RC构成的低通滤波器对输入信号进行调理,其中VCOM端可直接连接至ADC的VCOM引脚,也可通过OPA350缓冲输出,12 V电源可采用10μF和0.1μF的电容旁路,对于电容(2),当工作在低功耗模式时可选用2.7 nF的电容,在低速模式时则选用15 nF的电容。

5.2 ADS1724与TMS320的接口电路

图5给出了ASD1274与TMS320VC5509的接口电路,ADS1274与TMS320VC5509之间采用帧同步串行接口,CLKdiv接3.3 V,采样主时钟频率为27 MHz,四路模拟输入信号可采用图4所示的连接接入AINP和AINN。

德州仪器 ADC 滤波器 DSP FPGA 电压 电路 放大器 低通滤波器 电容 相关文章:

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)

- 运算放大器的选择(03-18)

- 单端数字音频放大器设计和应用考虑的要素(05-19)

- 为网络监控摄像机设计合适的电源(05-20)

- 改善可编程增益放大器性能的一个技巧(05-21)