流水线ADC中高速比较器的设计和分析

时间:10-06

来源:互联网

点击:

3.3 传输延迟时间的改善

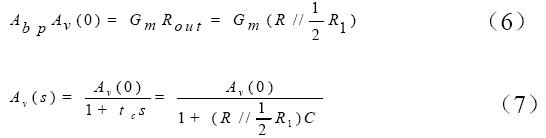

有两种方法减小传输比较器的延迟:1)降低前置增益运放的时间常数;2)加大前置增益运放的A(s)。

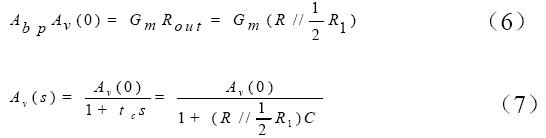

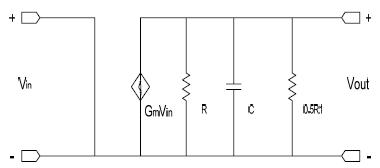

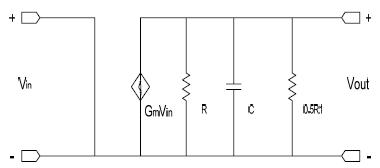

图3 为前置增益运放的交流小信号等效模型。根据图3,可得到等式(6),(7)

图3 前置增益运放的小信号等效模型

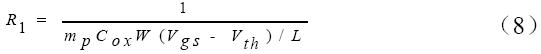

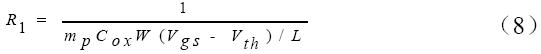

在上面的式子中,Av(0)为前置增益运放的直流小信号增益,Rout 是运放的等效输出阻抗, c t 为时间常数。R1 可以通过工作在深线性区的PMOS 管来代替,表达式为,

根据公式(6)(7),减小R1 可以使得 c t 减少,从而使响应速度指数增加,但是,同时减小R1,也使得Av(0)变小,从而使得响应速度线性下降。由此可见,与Av(0)相比, c t 对延迟时间的影响要显著多。因此,在设计时,对Av(0)要有个合理的设置。

4 模拟仿真与结果分析

在Cadence Composer 环境,使用Spectre 对本文的比较器进行仿真。时钟的模拟频率为100MHz,电源电压为3.3v,模拟的条件为Typical。

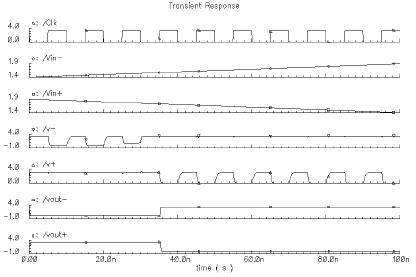

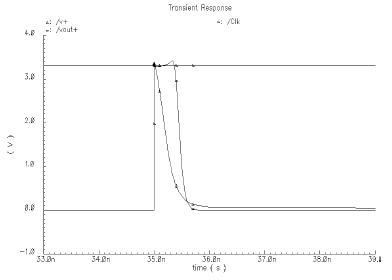

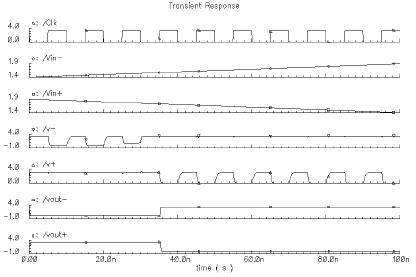

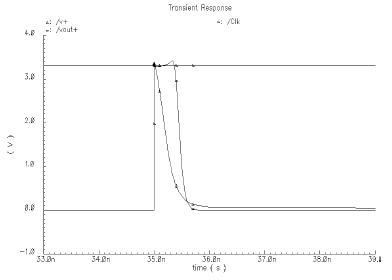

在图4 中,Vin+和Vin-为差分三角波信号,频率为2.5MHz,峰-峰值为1.455v"1.855v。Vref+和Vref-为差分直流信号,它们的差值为31.25mv,4 位子FlashADC 的1/2LSB。信号的共模电压为1.65v。V+和V-分别为锁存比较器的正负端输出,Vout+和Vout-分别为最终输出的正端和负端。从图4可以看出当Vin+和Vin-的差值小于1/2LSB 时,Vout+和Vout-的电压值发生翻转。图5为图4的局部放大图,可以看出传输比较器的延迟为680ps。在这种情况下整个电路消耗0.29mw 的功耗。

图4 比较器的仿真波形

图5 图4的局部放大图

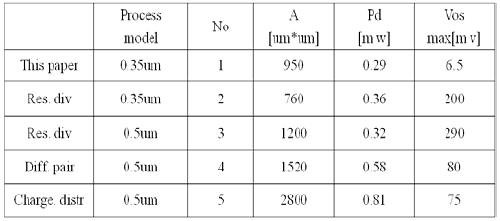

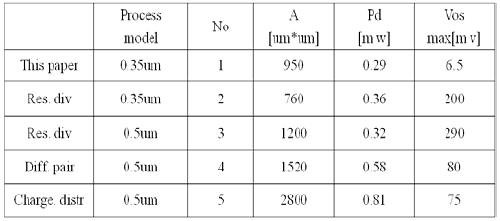

表1 中,前置增益动态比较器,电阻分配比较器(0.35um 和0.5um)、差分对比较器和电荷分配型比较器的性能进行总结。从表1中,可以看出与其它比较器相比,前置增益运放动态比较器拥有最低的功耗和失调电压。

表1 五种比较器的性能

5 结论

本文介绍了一种高速电压比较器,采用了前置增益运放锁存比较器。根据仿真结果,比较器在100MHz 的采样频率下消耗0.29mw 的功耗,并且具有6.5mv的低失调电压。因此,此比较器较适合用于流水线ADC。

本文作者的创新点:采用前置增益运放锁存的结构并结合版图,减小了失调电压;增加了隔离电路,减小了踢回噪声;分析了前置增益运放,改善了传输延迟时间。

有两种方法减小传输比较器的延迟:1)降低前置增益运放的时间常数;2)加大前置增益运放的A(s)。

图3 为前置增益运放的交流小信号等效模型。根据图3,可得到等式(6),(7)

图3 前置增益运放的小信号等效模型

在上面的式子中,Av(0)为前置增益运放的直流小信号增益,Rout 是运放的等效输出阻抗, c t 为时间常数。R1 可以通过工作在深线性区的PMOS 管来代替,表达式为,

根据公式(6)(7),减小R1 可以使得 c t 减少,从而使响应速度指数增加,但是,同时减小R1,也使得Av(0)变小,从而使得响应速度线性下降。由此可见,与Av(0)相比, c t 对延迟时间的影响要显著多。因此,在设计时,对Av(0)要有个合理的设置。

4 模拟仿真与结果分析

在Cadence Composer 环境,使用Spectre 对本文的比较器进行仿真。时钟的模拟频率为100MHz,电源电压为3.3v,模拟的条件为Typical。

在图4 中,Vin+和Vin-为差分三角波信号,频率为2.5MHz,峰-峰值为1.455v"1.855v。Vref+和Vref-为差分直流信号,它们的差值为31.25mv,4 位子FlashADC 的1/2LSB。信号的共模电压为1.65v。V+和V-分别为锁存比较器的正负端输出,Vout+和Vout-分别为最终输出的正端和负端。从图4可以看出当Vin+和Vin-的差值小于1/2LSB 时,Vout+和Vout-的电压值发生翻转。图5为图4的局部放大图,可以看出传输比较器的延迟为680ps。在这种情况下整个电路消耗0.29mw 的功耗。

图4 比较器的仿真波形

图5 图4的局部放大图

表1 中,前置增益动态比较器,电阻分配比较器(0.35um 和0.5um)、差分对比较器和电荷分配型比较器的性能进行总结。从表1中,可以看出与其它比较器相比,前置增益运放动态比较器拥有最低的功耗和失调电压。

表1 五种比较器的性能

5 结论

本文介绍了一种高速电压比较器,采用了前置增益运放锁存比较器。根据仿真结果,比较器在100MHz 的采样频率下消耗0.29mw 的功耗,并且具有6.5mv的低失调电压。因此,此比较器较适合用于流水线ADC。

本文作者的创新点:采用前置增益运放锁存的结构并结合版图,减小了失调电压;增加了隔离电路,减小了踢回噪声;分析了前置增益运放,改善了传输延迟时间。

比较器 ADC 电子 电压 电路 电阻 电容 放大器 电流 仿真 Cadence 相关文章:

- 建立比较器的外部滞回电压(11-28)

- 比较器的合理选择(06-09)

- 采用新型放大器实现高性能的电流检测(05-10)

- 适用于SAR ADC的CMOS比较器的设计(01-02)

- 利用低功耗比较器自动检测音频附件(05-11)

- 高性能CMOS集成电压比较器设计(10-07)