使用电容实现LVDS连接交流耦合的优点分析

时间:09-28

来源:互联网

点击:

LVDS(低压差分信号)是物理层数据接口标准,由TIA/EIA-644和IEEE 1596.3标准定义,主要为在平衡阻抗可控的100Ω介质上实现高速、低功耗和低噪声点对点通信而设计。与其它差分信号标准一样,LVDS由于消除了电磁辐射,它比单端信号辐射的噪声要低得多。同时外部噪声作为共模信号耦合到两条线上,被作为共模信号抑制掉,因此它的抗噪声能力比单端信号要强得多。另外,LVDS驱动器的输出采用电流驱动方式,与其它差分信号标准中电压驱动相比较,它减少了地线回流,消除了浪涌电流。降低电压摆幅(只有±350mV,PECL是±800mV,RS-422是2V)使LVDS能达到与PECL(>800Mbps)等同的数据速率,而功耗只有PECL的十分之一。

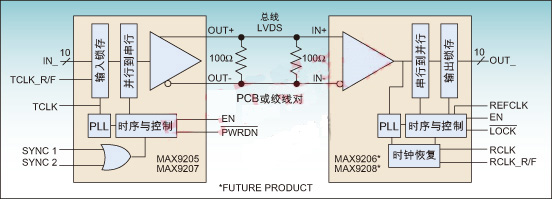

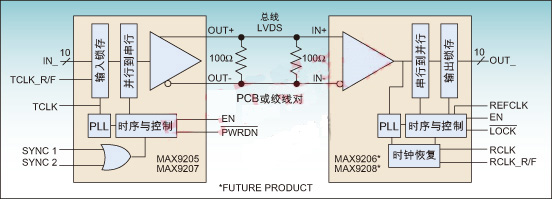

LVDS的高速、低功耗和低噪声特性使其成为电信和网络设备的背板互连、3G蜂窝电话基站中机架内部的互连、数字视频接口等应用的理想选择。除上述优点外,LVDS串行器和解串器(图1)还为系统设计节省了大量的空间和金钱。采用这种方案可以把互连密度降低5倍,在3G及其它具有大量板卡的通信应用中,节省大量的空间和费用。

图1:串行器-解串器典型应用电路。

使用电容实现LVDS数据连接的交流耦合有很多益处,比如电平转换、去除共模误差以及避免输入电压故障的发生。本文不仅介绍了电容的适当选型,也为和终端拓扑提供指导,同时也讨论了共模故障分析的问题。

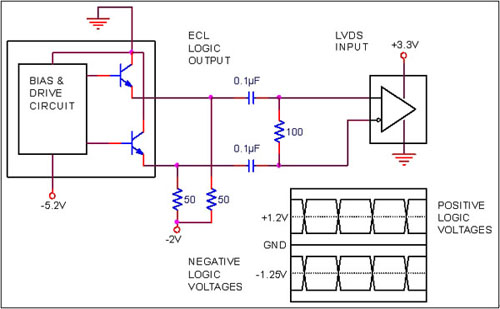

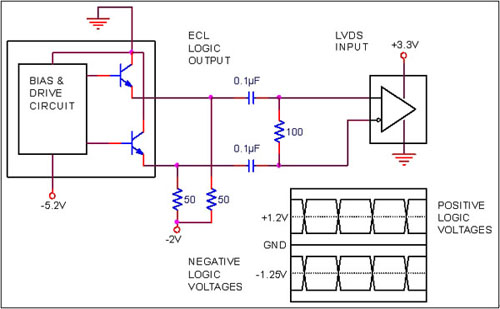

LVDS逻辑输入是众多现有逻辑标准的一种。只要信号源可以为LVDS输入提供足够的幅度,典型值为差分100mV Vp-p,采用交流耦合就可以提供所需的电平转换。图2描述了一个负压ECL逻辑经交流耦合后将信号转换到LVDS逻辑的电路图。

图2:ECL-LVDS电平转换配置。

优化共模电压

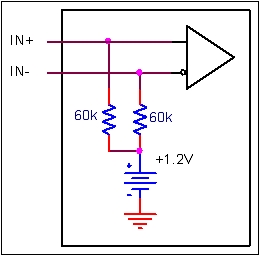

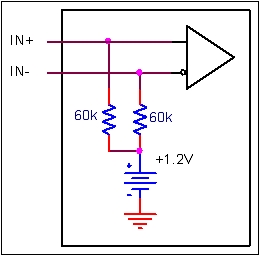

交流耦合LVDS的另外一个优点是允许接收IC设置其最优的共模电压。图3展示了一个典型的LVDS输入电路。一个通常为1.2V的内部参考电压为两个高阻端接电阻提供偏置。如果输入是交流耦合,接收IC可以将允许共模电压设置为内部的偏置电平。

图3:LVDS输入偏置电路。

过压保护

LVDS信号在汽车电子的串行解串器(SerDes)链路中总是采用交流耦合,因为这种配置可以防止汽车电池短路。对于任何通过电源配线槽的信号线,一个基本要求是必须能够忍受与电池电压短路而不损坏。采用交流耦合的LVDS链路,当耦合电容充电到电池电压时,仅仅会有一个短暂的大电流脉冲。电流的幅度峰值是短路时实际阻抗的函数。电流毛刺的持续时间是耦合电容以及LVDS输入输出保护结构的函数。虽然SerDes链路在短路时并不工作,但当短路故障解除后可恢复工作。

图4:LVDS端接电路。

电容选择

有以下几个因素影响到电容的选择。

1.参数值

LVDS链路交流耦合电容的选择与一系列的参数相关,包括:输出驱动电平、输入门限电平、负载阻抗、电缆长度、最长的脉冲周期。

标准的LVDS输出驱动电平通常定义为最小250mV,且输入电平门限定义为最大100mV。因此,确保有效电平值的最大的衰减量为:

换句话说,由直流电阻产生的衰减、交流衰减以及电容耦合衰减的总合必须小于8dB。两端差分负载阻抗通常为100Ω,分析电缆长度时需要同时考虑电缆的交流和直流衰减以及连接器阻抗导致的衰减。最后,还必须考虑数据本身,LVDS连接可以传输的最大脉冲宽度取决于工作频率和数据传输协议对连续1(或0)的数量限制。

对于具体应用,精确的计算可能过于棘手,也可以简单选用0.1uF电容,能够满足大多数应用的要求。当数据速率降到10MHz以下或采用更长的电缆时(例如>5米),需要重新核实电容值,也可以通过计算、仿真或实际测量获取电容值。

2.电压和介质

电容的工作电压应远大于出现故障状况时的最大峰值电压。在汽车电子应用中,峰值故障电压是18V。一般不需要将故障条件下的电压加倍,例如:将电池电压加倍或考虑甩负载电压。

使用X5R、X7R或类似介质的电容,避免使用那些电压或温度系数有明显变化的介质电容,如Y5V或Z5U。

端接拓扑

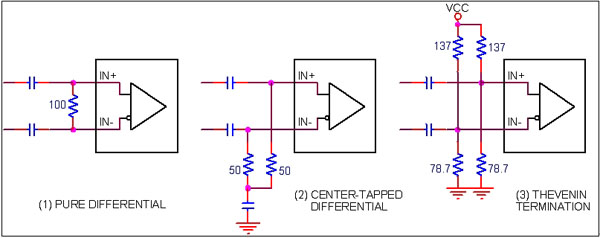

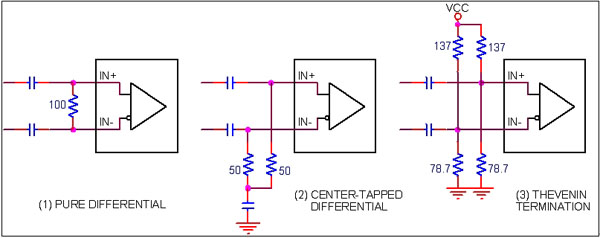

端接拓扑可以从三个主要电路中选择:(1)纯差分,(2)中心抽头差分,(3)戴维宁端接。图3给出了这三个电路,纯差分是最常用的配置,且在良好屏蔽环境中用于信号端接可以提供很好的工作性能。中心抽头的差分端子将100Ω分为两个50Ω电阻,且在中心抽头位置使用旁路电容。由于任何耦合到LVDS线对上的共模能量对地都有一个低阻通路,这种方式在噪声环境下工作很好。纯差分和中心抽头差分端接必须用于包含内部偏置的LVDS输入电路。

如果LVDS接收器不提供内部偏置,且输入信号为交流耦合,则必须使用戴维宁端接。所选电阻必须使每条线上的戴维宁等效电阻为50Ω,且每条线的戴维宁等效电压为1.2V,图5数值工作于3.3V电源。

LVDS的高速、低功耗和低噪声特性使其成为电信和网络设备的背板互连、3G蜂窝电话基站中机架内部的互连、数字视频接口等应用的理想选择。除上述优点外,LVDS串行器和解串器(图1)还为系统设计节省了大量的空间和金钱。采用这种方案可以把互连密度降低5倍,在3G及其它具有大量板卡的通信应用中,节省大量的空间和费用。

图1:串行器-解串器典型应用电路。

使用电容实现LVDS数据连接的交流耦合有很多益处,比如电平转换、去除共模误差以及避免输入电压故障的发生。本文不仅介绍了电容的适当选型,也为和终端拓扑提供指导,同时也讨论了共模故障分析的问题。

LVDS逻辑输入是众多现有逻辑标准的一种。只要信号源可以为LVDS输入提供足够的幅度,典型值为差分100mV Vp-p,采用交流耦合就可以提供所需的电平转换。图2描述了一个负压ECL逻辑经交流耦合后将信号转换到LVDS逻辑的电路图。

图2:ECL-LVDS电平转换配置。

优化共模电压

交流耦合LVDS的另外一个优点是允许接收IC设置其最优的共模电压。图3展示了一个典型的LVDS输入电路。一个通常为1.2V的内部参考电压为两个高阻端接电阻提供偏置。如果输入是交流耦合,接收IC可以将允许共模电压设置为内部的偏置电平。

图3:LVDS输入偏置电路。

过压保护

LVDS信号在汽车电子的串行解串器(SerDes)链路中总是采用交流耦合,因为这种配置可以防止汽车电池短路。对于任何通过电源配线槽的信号线,一个基本要求是必须能够忍受与电池电压短路而不损坏。采用交流耦合的LVDS链路,当耦合电容充电到电池电压时,仅仅会有一个短暂的大电流脉冲。电流的幅度峰值是短路时实际阻抗的函数。电流毛刺的持续时间是耦合电容以及LVDS输入输出保护结构的函数。虽然SerDes链路在短路时并不工作,但当短路故障解除后可恢复工作。

图4:LVDS端接电路。

电容选择

有以下几个因素影响到电容的选择。

1.参数值

LVDS链路交流耦合电容的选择与一系列的参数相关,包括:输出驱动电平、输入门限电平、负载阻抗、电缆长度、最长的脉冲周期。

标准的LVDS输出驱动电平通常定义为最小250mV,且输入电平门限定义为最大100mV。因此,确保有效电平值的最大的衰减量为:

换句话说,由直流电阻产生的衰减、交流衰减以及电容耦合衰减的总合必须小于8dB。两端差分负载阻抗通常为100Ω,分析电缆长度时需要同时考虑电缆的交流和直流衰减以及连接器阻抗导致的衰减。最后,还必须考虑数据本身,LVDS连接可以传输的最大脉冲宽度取决于工作频率和数据传输协议对连续1(或0)的数量限制。

对于具体应用,精确的计算可能过于棘手,也可以简单选用0.1uF电容,能够满足大多数应用的要求。当数据速率降到10MHz以下或采用更长的电缆时(例如>5米),需要重新核实电容值,也可以通过计算、仿真或实际测量获取电容值。

2.电压和介质

电容的工作电压应远大于出现故障状况时的最大峰值电压。在汽车电子应用中,峰值故障电压是18V。一般不需要将故障条件下的电压加倍,例如:将电池电压加倍或考虑甩负载电压。

使用X5R、X7R或类似介质的电容,避免使用那些电压或温度系数有明显变化的介质电容,如Y5V或Z5U。

端接拓扑

端接拓扑可以从三个主要电路中选择:(1)纯差分,(2)中心抽头差分,(3)戴维宁端接。图3给出了这三个电路,纯差分是最常用的配置,且在良好屏蔽环境中用于信号端接可以提供很好的工作性能。中心抽头的差分端子将100Ω分为两个50Ω电阻,且在中心抽头位置使用旁路电容。由于任何耦合到LVDS线对上的共模能量对地都有一个低阻通路,这种方式在噪声环境下工作很好。纯差分和中心抽头差分端接必须用于包含内部偏置的LVDS输入电路。

如果LVDS接收器不提供内部偏置,且输入信号为交流耦合,则必须使用戴维宁端接。所选电阻必须使每条线上的戴维宁等效电阻为50Ω,且每条线的戴维宁等效电压为1.2V,图5数值工作于3.3V电源。

电流 电压 电路 电容 电路图 电阻 汽车电子 连接器 仿真 电子 相关文章:

- ECL电源开关的应用研究(11-30)

- 电流源电路(01-23)

- 什么是权电流型DAC(数模转换器)(01-24)

- 高速应用中电流反馈运放电路设计分析(01-06)

- 线性光电耦合器在开关电源中的应用(01-15)

- 可对储能器件进行安全且快速充电的通用型电流源(03-13)