一种基于DSP的软件锁相环模型与实现

时间:09-18

来源:互联网

点击:

4 软件锁相环的DSP实现

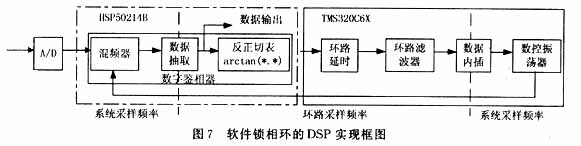

在宽带数字化接收机的实现中,数字下变频采用通用可编程下变频器HSP50214B。在实现载波同步、码元同步软件锁相环的整个反馈环路中,数控振荡器、鉴相器由HSP50214B完成,环路滤波在TMS320C6X中完成。DSP实现框图如图7所示。

??????

环路延时是一个应该重视的因素。带来软件锁相环环路延时主要有以下2种原因:

(1)环路内FIR滤波器带来的延时;

(2)数据等待处理带来的额外延时。

在数字化接收机中,采用粗同步与细同步两级。粗同步环路时延大,反应速度慢;细同步环路时延小,反应速度快,粗同步保证有效信号落在滤波器的通带之内,细同步可以在粗同步基础上获得较大捕获带和同步带。此外还采用抛弃若干采样点,消除不必要的环路延时。

可以看出,软件锁相环具有处理灵活的优点,他摆脱了复杂的硬件电路设计,解决了许多模拟环遇到的难题。目前,由于DSP功能越来越强大,工作速度越来越高,也为软件锁相技术的发展创造了必要的条件。?

在宽带数字化接收机的实现中,数字下变频采用通用可编程下变频器HSP50214B。在实现载波同步、码元同步软件锁相环的整个反馈环路中,数控振荡器、鉴相器由HSP50214B完成,环路滤波在TMS320C6X中完成。DSP实现框图如图7所示。

??????

环路延时是一个应该重视的因素。带来软件锁相环环路延时主要有以下2种原因:

(1)环路内FIR滤波器带来的延时;

(2)数据等待处理带来的额外延时。

在数字化接收机中,采用粗同步与细同步两级。粗同步环路时延大,反应速度慢;细同步环路时延小,反应速度快,粗同步保证有效信号落在滤波器的通带之内,细同步可以在粗同步基础上获得较大捕获带和同步带。此外还采用抛弃若干采样点,消除不必要的环路延时。

可以看出,软件锁相环具有处理灵活的优点,他摆脱了复杂的硬件电路设计,解决了许多模拟环遇到的难题。目前,由于DSP功能越来越强大,工作速度越来越高,也为软件锁相技术的发展创造了必要的条件。?

集成电路 无线电 DSP 电路 电阻 电容 振荡器 滤波器 仿真 相关文章:

- 基于新型ASSP LTC3455的硬盘MP3电源设计(06-07)

- 单片彩色LCoS显示系统的设计实现(09-09)

- 具有开关电源通路管理的下一代电源管理集成电路(08-28)

- 如何利用DCP获得更精确的性能(10-01)

- 集成电路的种类与用途(09-20)

- CMOS集成电路中ESD保护技术研究(10-17)