一种基于DSP的软件锁相环模型与实现

时间:09-18

来源:互联网

点击:

随着大规模集成电路及高速数字信号处理器的发展,通信领域的信号处理越来越多地在数字域付诸实现。软件锁相技术是随着软件无线电的发展和高速DSP的出现而开展起来的一个研究课题。在软件无线电接收机中采用的锁相技术是基于数字信号处理技术在DSP等通用可编程器件上的实现形式,由于这一类型锁相环的功能主要通过软件编程实现,因此可将其称为软件锁相环(software PLL)。

尽管软件锁相环采用的基本算法思想与模拟锁相环和数字锁相环相比并没有太大变化,然而其实现方式却完全不同。本文将建立软件锁相环的Z 域模型,分析软件锁相环中的延时估计、捕获速度及多速率条件下的软件锁相环模型问题。?

1 软件锁相环的基本模型

在模拟锁相环的基础上,利用数字、模拟系统彼此之间的联系,以二阶二型锁相环为例建立软件锁相环的Z 域模型。

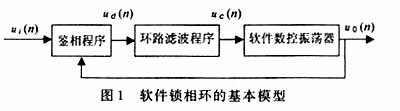

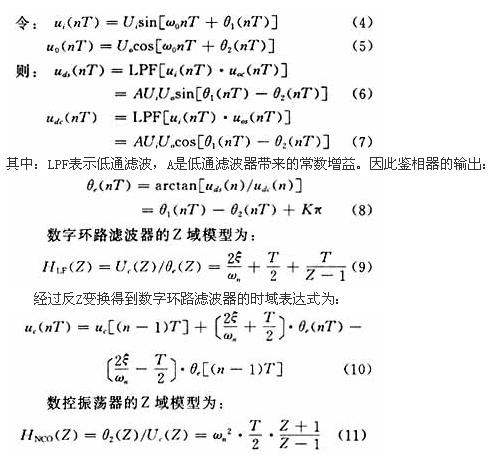

如果将锁相环的基本部件采用软件编程的形式实现,就可以得到软件锁相环的基本组成,如图1所示。

首先从模拟锁相环的S域模型出发得到软件锁相环的Z 域模型。由于双线性变换是联系模拟系统与数字系统的一个重要方法,具有转换简单且表达式清晰明了的特点,因此本文选择双线性变换法作为模拟锁相环与软件锁相环之间的转换基础。

?

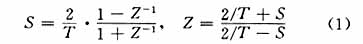

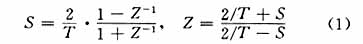

式(1)是双线性变换法的复频域表达式:

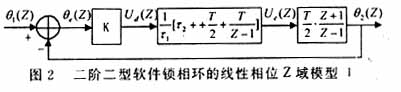

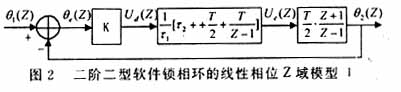

其中:T是联系数字系统与模拟系统的采样时间间隔,1/T表示采样频率。根据该转换关系,对S域模型各部分对应的数字复频域表达式进行转换,可以得到如图2所示的复频域模型。?

在实际应用中,二阶线性系统常采用阻尼因子ξ、无阻尼振荡频率ωn描述。在二阶二型锁相环中,τ1,τ2 ,K 与ξ,ωn之间的对应关系如下:

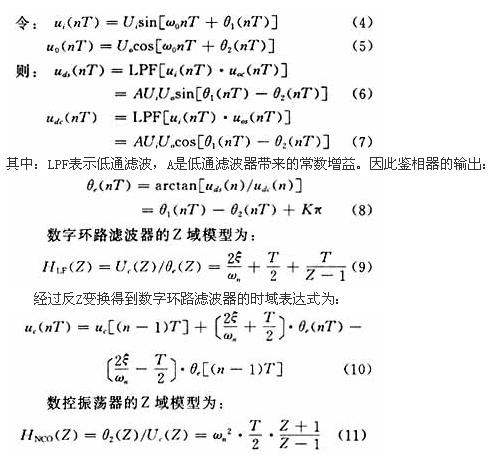

在式(1)和式(2)的基础上对图2进行等效变换,可以得到软件锁相环的另一个线性相位Z域模型,如图3所示。?

在模型Ⅰ中,参数τ1,τ2和K与实现电路功能的电阻、电容、压控振荡器密切相关。而实现软件锁相功能的却是乘法器、加法器与寄存器,因此采用模型Ⅱ表征软件锁相环线性相位Z域模型显得更有实际意义。

?

2 软件锁相环的数学模型

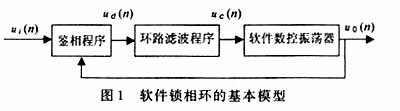

数字鉴相器的Z域模型如下:

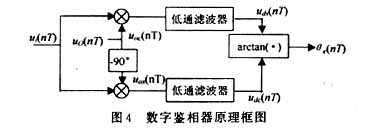

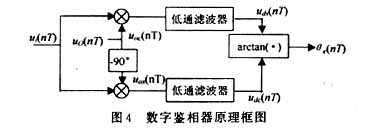

实现数字鉴相器的方法之一就是借助信号的正交分解,图4是该方法的原理框图。

?

?

?

如果以数字频率描述数控振荡器,则称其数字中心频率为ω0T,数字偏置频率为ωn2·uc(nT)·T。因此,该数控振荡器的灵敏度与数字灵敏度分别为·T。

3 多速率条件下的软件锁相环

在数字化接收机中,经常碰到多速率条件下的抽样率转换问题。所谓多速率系统是指在一个数字系统中存在2个或2个以上的抽样率。构成软件锁相环鉴相器的混频器通常工作在系统采样频率上。在满足奈奎斯特采样定律的前提下,数字化接收机的系统采样率一般高达数10 M。而数字鉴相器组成部分的反正切表,由于混频之后的数据经过多倍抽取,工作频率已经下降到与信号波特率相近的水平。数据抽取同时也降低DSP的运算量,由DSP完成的环路滤波的处理速度近似等于信号波特率。此外由于软件锁相环中的数控振荡器需要给混频器提供同样速率的正交载波,其工作速率与混频器相等,需要进行内插来调整速率。

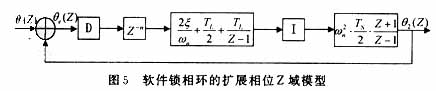

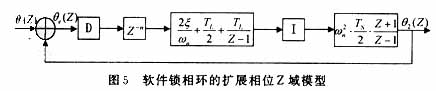

为了合理利用DSP有限的计算资源,总是在满足同步需要的前提下尽可能地降低环路滤波的工作速率,也就是通常所说的环路频率。环路频率是软件锁相环的一个重要参数,他同时决定着锁相环算法的计算量与捕获速度。环路频率过高将带来额外的计算负担,环路频率太低又不能满足捕获速度的需要,在应用中通常取系统波特率作为环路频率的大小。该扩展模型对应的线性相位Z域模型如图5所示。

其中:D表示数据抽取,I表示数据内插。数据在抽取之前先要进行抗混叠滤波,可用于抗混叠滤波的FIR滤波器有CIC滤波器、半带滤波器等。

实际情形中,由于零阶保持内插几乎不需要额外的运算量,因此经常被采用。实际上环路频率fL总是能够跟上环路滤波器输出信号的变化速率。换言之,对环路滤波器输出信号按照fL的速率进行采样保留了他的全部信息,因此零阶保持内插对系统性能不会有太大影响。

结合上述软件锁相环的基本原理,下面借助Matlab仿真观察软件锁相环的系统响应。本文以频率阶跃信号作为输入,观察软件锁相环的系统响应从而进一步验证本文建立的一系列软件锁相环模型。

设定系统采样频率为1 MHz,仿真时间0.1 s,信号中心频率125 kHz,起始相位-π/4,输入频率阶跃100 Hz,起始点为0.02 s,抽取因子为8。一般情况下,都希望环路工作在欠阻尼状态,取阻尼因子ξ=0.707,ωn由2π ΔF(快捕带宽)决定,分别取2π*40,2π*50,2π*100。仿真出相位误差响应曲线、NCO偏置频率曲线和频率阶跃信号的相位曲线,如图6所示。

从图6可以看出,软件锁相环在[0,0.02]区间内相位误差为0,处于锁定状态。在t=0.02 s时刻,输入信号频率产生了大小为100 Hz的阶跃,导致软件锁相环进入捕获过程。由于软件锁相环的校正作用,当ωn=2π*50时,系统在t=0.05 s时刻重又进入同步状态,相位误差依旧为0。由相位误差响应曲线可以看到,锁相环可以无相差的跟踪频率阶跃信号,同时表明虽然锁相环鉴相误差为0,但是由于环路滤波器的理想积分作用其输出的控制信号并不为0,由该控制信号产生的100 Hz偏置频率保证了NCO输出与输入信号的同步。当快捕带宽发生变化导致改变时,锁相环的捕获速度也发生了变化,快捕带宽越宽,捕获速度越快。?

尽管软件锁相环采用的基本算法思想与模拟锁相环和数字锁相环相比并没有太大变化,然而其实现方式却完全不同。本文将建立软件锁相环的Z 域模型,分析软件锁相环中的延时估计、捕获速度及多速率条件下的软件锁相环模型问题。?

1 软件锁相环的基本模型

在模拟锁相环的基础上,利用数字、模拟系统彼此之间的联系,以二阶二型锁相环为例建立软件锁相环的Z 域模型。

如果将锁相环的基本部件采用软件编程的形式实现,就可以得到软件锁相环的基本组成,如图1所示。

首先从模拟锁相环的S域模型出发得到软件锁相环的Z 域模型。由于双线性变换是联系模拟系统与数字系统的一个重要方法,具有转换简单且表达式清晰明了的特点,因此本文选择双线性变换法作为模拟锁相环与软件锁相环之间的转换基础。

?

式(1)是双线性变换法的复频域表达式:

其中:T是联系数字系统与模拟系统的采样时间间隔,1/T表示采样频率。根据该转换关系,对S域模型各部分对应的数字复频域表达式进行转换,可以得到如图2所示的复频域模型。?

在实际应用中,二阶线性系统常采用阻尼因子ξ、无阻尼振荡频率ωn描述。在二阶二型锁相环中,τ1,τ2 ,K 与ξ,ωn之间的对应关系如下:

在式(1)和式(2)的基础上对图2进行等效变换,可以得到软件锁相环的另一个线性相位Z域模型,如图3所示。?

在模型Ⅰ中,参数τ1,τ2和K与实现电路功能的电阻、电容、压控振荡器密切相关。而实现软件锁相功能的却是乘法器、加法器与寄存器,因此采用模型Ⅱ表征软件锁相环线性相位Z域模型显得更有实际意义。

?

2 软件锁相环的数学模型

数字鉴相器的Z域模型如下:

实现数字鉴相器的方法之一就是借助信号的正交分解,图4是该方法的原理框图。

?

?

?如果以数字频率描述数控振荡器,则称其数字中心频率为ω0T,数字偏置频率为ωn2·uc(nT)·T。因此,该数控振荡器的灵敏度与数字灵敏度分别为·T。

3 多速率条件下的软件锁相环

在数字化接收机中,经常碰到多速率条件下的抽样率转换问题。所谓多速率系统是指在一个数字系统中存在2个或2个以上的抽样率。构成软件锁相环鉴相器的混频器通常工作在系统采样频率上。在满足奈奎斯特采样定律的前提下,数字化接收机的系统采样率一般高达数10 M。而数字鉴相器组成部分的反正切表,由于混频之后的数据经过多倍抽取,工作频率已经下降到与信号波特率相近的水平。数据抽取同时也降低DSP的运算量,由DSP完成的环路滤波的处理速度近似等于信号波特率。此外由于软件锁相环中的数控振荡器需要给混频器提供同样速率的正交载波,其工作速率与混频器相等,需要进行内插来调整速率。

为了合理利用DSP有限的计算资源,总是在满足同步需要的前提下尽可能地降低环路滤波的工作速率,也就是通常所说的环路频率。环路频率是软件锁相环的一个重要参数,他同时决定着锁相环算法的计算量与捕获速度。环路频率过高将带来额外的计算负担,环路频率太低又不能满足捕获速度的需要,在应用中通常取系统波特率作为环路频率的大小。该扩展模型对应的线性相位Z域模型如图5所示。

其中:D表示数据抽取,I表示数据内插。数据在抽取之前先要进行抗混叠滤波,可用于抗混叠滤波的FIR滤波器有CIC滤波器、半带滤波器等。

实际情形中,由于零阶保持内插几乎不需要额外的运算量,因此经常被采用。实际上环路频率fL总是能够跟上环路滤波器输出信号的变化速率。换言之,对环路滤波器输出信号按照fL的速率进行采样保留了他的全部信息,因此零阶保持内插对系统性能不会有太大影响。

结合上述软件锁相环的基本原理,下面借助Matlab仿真观察软件锁相环的系统响应。本文以频率阶跃信号作为输入,观察软件锁相环的系统响应从而进一步验证本文建立的一系列软件锁相环模型。

设定系统采样频率为1 MHz,仿真时间0.1 s,信号中心频率125 kHz,起始相位-π/4,输入频率阶跃100 Hz,起始点为0.02 s,抽取因子为8。一般情况下,都希望环路工作在欠阻尼状态,取阻尼因子ξ=0.707,ωn由2π ΔF(快捕带宽)决定,分别取2π*40,2π*50,2π*100。仿真出相位误差响应曲线、NCO偏置频率曲线和频率阶跃信号的相位曲线,如图6所示。

从图6可以看出,软件锁相环在[0,0.02]区间内相位误差为0,处于锁定状态。在t=0.02 s时刻,输入信号频率产生了大小为100 Hz的阶跃,导致软件锁相环进入捕获过程。由于软件锁相环的校正作用,当ωn=2π*50时,系统在t=0.05 s时刻重又进入同步状态,相位误差依旧为0。由相位误差响应曲线可以看到,锁相环可以无相差的跟踪频率阶跃信号,同时表明虽然锁相环鉴相误差为0,但是由于环路滤波器的理想积分作用其输出的控制信号并不为0,由该控制信号产生的100 Hz偏置频率保证了NCO输出与输入信号的同步。当快捕带宽发生变化导致改变时,锁相环的捕获速度也发生了变化,快捕带宽越宽,捕获速度越快。?

集成电路 无线电 DSP 电路 电阻 电容 振荡器 滤波器 仿真 相关文章:

- 基于新型ASSP LTC3455的硬盘MP3电源设计(06-07)

- 单片彩色LCoS显示系统的设计实现(09-09)

- 具有开关电源通路管理的下一代电源管理集成电路(08-28)

- 如何利用DCP获得更精确的性能(10-01)

- 集成电路的种类与用途(09-20)

- CMOS集成电路中ESD保护技术研究(10-17)