嵌入式设备静止图像编码

|

在INTRA帧量化中,

时,F(u,v)量化为0,即

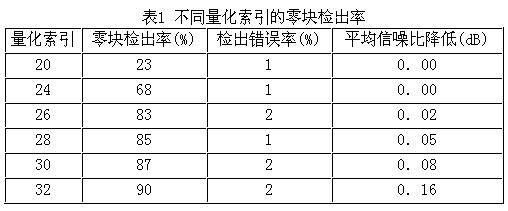

时,所有变换系数量化为0。由于该式是量化系数全为零的充分条件,而不是必要条件。实验结果显示,使用该门限检测出零块的正确性为100%,大量的量化系数为全零块却检测不出来。为了大幅提高零块检出率,增大该门限T为3Qstep,测量miss.qcf 20帧编码的平均情况,测试结果见表1。从表1可以看出,零块检测率随着量化索引增大而增大,可能将部分非零块检测成零块,但这对信噪比影响不大。

|

2 缩减存储器需求

减少运算中的存储器需求对于嵌入式设备十分重要。宏块编码的过程包含预测、模式选择、变换量化扫描、逆量化等。从图2可以看出,在INTRA16×16的4种预测模式中,只使用上边和左边的各16个像素作为预测参考,在INTRA 4×4 的9种预测模式中,仅使用左边4个像素和上边9个像素作为预测参考,因而重建图像并不需要整帧存储,只需存储这几个参考点就可以了。假设宏块编码按照从左到右、从上到下顺序进行,则水平方向的像素需要存储一整行。在INTRA 4×4模式编码时,由于相邻的4×4块模式高度相关,采用相邻块的预测模式预测当前块的最可能模式,同样只需要存储上边一行4×4和左边一个4×4块的编码模式(如图3)。

图3

在对量化后变字长编码(VLC)系数的个数进行编码时,需要利用相邻两块的非零系数个数对该块进行预测,也只需要存储上边一行4×4和左边一个4×4块的编码模式的非零系数个数,如图3。在对整帧图像的数据比特串(SODB)添加原始字节序列载荷(RBSP)结尾比特(RBSP trailing bits,添加一比特的“1”和若干比特“0”,以便字节对齐)后,再检查RBSP 中是否存在连续的三字节“00000000 00000000 000000xx”;若存在这种连续的三字节码,在第三字节前插入一字节的“0×03”,以免与起始码竞争,形成EBSP码流,这需要将近两倍的整帧图像码流大小。为了减小存储器需求,在每个宏块编码结束后即检查该宏块SODB中的起始码竞争问题,并保留SODB最后两字节的零字节个数,以便与下一宏块的SODB的开始字节形成连续的起始码竞争检测;对一帧图像的最后一个宏块,先添加结尾停止比特,再检测起始码竞争。采用这种方法产生H.264 附录B中的字节流时,存储器需求从两帧码流大小缩小到两个宏块码流大小。通过对码流输出过程的改进,使INTRA帧编码需要的存储器大小不随图像大小的增加而增加,这时编码过程中的存储器不超过9K个整数。对于基于片上存储器的多媒体处理器,存储器需求的减少可以大量缩减中间结果的片外片上转移,减小数据转移的负担,提高程序的运行速度。

采用H.264 INTRA帧对静止图像进行编码时,在编码器端不需要显示本地重建图像,可省掉去方块效应滤波器;利用模式选择时计算的绝对差值和,可提前判断量化后全零系数块,节省大量的计算。分阶段地对各个宏块的码流插入竞争阻止字节(emulation prevention byte),以保证原始字节序列载荷中不含起始码,有效减少存储器的需求。运算复杂性和存储器需求极低的H.264 INTRA编码模式,可代替JPEG2000,用于嵌入式设备的静止图像编码。

- 单片机嵌入式系统在运程电网监测系统中的应用(05-13)

- 嵌入式测试为串行I/O提供真正的价值(05-26)

- 今天的绿色 POL DC/DC 转换器设计需要高效率和低 IQ(07-11)

- flash接口电路的实现(07-18)

- RS485串行总线可靠性的研究(03-24)

- 一种支持ISP的Flash在嵌入式设计中的应用(08-19)