如何加强信号路径的性能

时间:08-30

来源:互联网

点击:

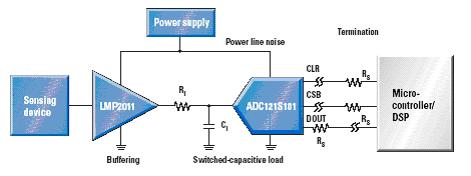

高精度信号路径图

信号路径的设计为系统设计工程师提供不少可供他们发挥的机会。以设有模拟/数字转换器的信号路径为例来说,工程师进行设计时不但要为传感器提供缓冲,而且还要解决模拟/数字转换器开关电容的输入充电问题,以及要尽量减少系统的噪声源,只要构思的设计能解决这些问题,便可大幅提升系统的性能。今期的信号路径设计专辑将会深入讨论这方面的问题。

为传感器提供缓冲

若传感器无法驱动模拟/数字转换器的电容负载,我们可以利用运算放大器为其提供缓冲。由于许多系统都规定只可采用一个电源供应,因此选用的运算放大器必须采用与模拟/数字转换器相同的电压操作,这一点非常重要。虽然共用供电电压有助精简系统设计及节省成本,但运算放大器因为受供电电压的掣肘,以致其输入及输出的能力无法得到充分的发挥。以 ADC121S101 这类模拟/数字转换器芯片为例

来说,由于这类芯片的参考电压 (VREF) 也同时是供电电压,因此选用设有轨到轨输出 (RRO) 功能的运算放大器如 LMP2011 较为理想。正因为 LMP2011 放大器芯片设有轨到轨输出功能,所以系统设计工程师可以利用模拟/数字转换器的整个动态范围,以确保可以使用所有输出代码。

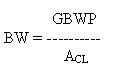

我们选定具备适当输入/输出能力的运算放大器之后,便要考量放大器的增益带宽。若信号源的最高输出低于参考电压,缓冲级便可能需要为其提供增益。若运算放大器配置为单位增益放大器,其频率会受增益带宽积 (GBWP) 所限,以致只能选用 -3dB 频率。由于运算放大器的增益带宽积属于不变的常数,因此我们只要采用增益为 ACL 的闭环配置便可降低放大器的带宽,降幅高达 ACL 倍,其计算公式如下:

例如,若 LMP2011 运算放大器的增益带宽积为 3MHz,而 ACL 增益则设定为 10V/V,那么运算放大器的带宽便可达 300kHz。

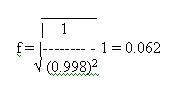

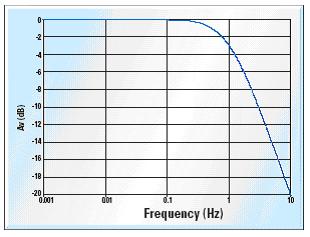

由于闭环带宽与放大器的频率同样是 -3dB,放大器若以这个频率操作,其输出是输入值的 70.7%,因此若以 -3dB 频率作为基准衡量,输出振幅的误差会高达 29.3%。模拟/数字转换器的误差以最低有效位 (LSB) 作为计算单位。1 LSB定义为 VREF/2n,定义中的 VREF 是指参考电压,而 n 则是模拟/数字转换器的分辨度。例如,8 位模拟/数字转换器的 1 LSB 是 VREF/256。对于模拟/数字转换器最低有效位准确度必须高达 1/2 LSB的系统来说,8 位模拟/数字转换器的输入增益准确度必须高达 1-1/2n+1,亦即 99.8%。为了保证运算放大器的增益准确度足以满足系统的特定要求,我们必须计算出运算放大器的最高操作频率 (fmax)。以下是这个频率的计算方法:先假定运算放大器的频率大约相当于单极滤波器的频率响应。图 1 所示的曲线图显示增益 (AV) 及 -3dB 频率 (fo) 已按照 1 加以规范化。

以下是这条曲线的公式:

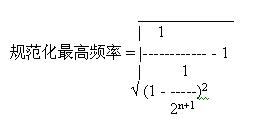

为了确保 8 位系统符合 1/2 最低有效位错误的要求,运算放大器的规范化最高频率 (fmax) 是:

以 8 位的模拟/数字转换器为例来说,若准确度规定为 1/2 最低有效位,运算放大器的实际带宽只有 0.062 x GBWP (增益带宽积)。换言之,若LMP2011 运算放大器的增益带宽积为 3MHz,而且采用的是配合单位增益的配置,那么其实际带宽只有 186kHz。若增益必须超过 1 倍,实际带宽更会进一步下跌。以不同分辨度的模拟/数字转换器来说,1/2 最低有效位错误的规范化最高频率可以根据以下公式计算出来:

图1:运算放大器的频率响应

为开关电容负载充电

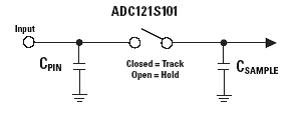

由于上述设有模拟/数字转换器的信号路径添加了运算放大器,因此可以驱动电容负载。但模拟/数字转换器的输入端本身便是开关电容负载 (参看图 2)。

图 2:ADC121S101 芯片的输入端

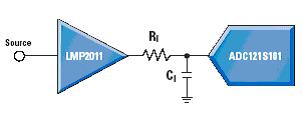

ADC121S101 模拟/数字转换器芯片处于“保持”模式时,其输入电容 (CPIN) 不会超过 4pF,若处于“跟踪”模式时,其输入电容 (CSAMPLE + CPIN) 则不会超过 30pF。输入电容的改变会导致误差的出现,为了将误差减至最少,CI 电容器必须通过输入引脚连接接地。模拟/数字转换器处于“跟踪”模式时,CI 电容器的电容远远大于转换器的输入电容,因此 CI 电容器可为模拟/数字转换器的取样电容器提供充电电流,迅速为其充电。一般来说,我们要为有关的电容器添加隔离电阻,以便额外添加的负载电 容可与运算放大器的输出端分隔开 (参看图 3)。

图3:快速充电电路

为 RC 网络选用适当的数值时,我们必须考量三个重要的因素。首先,设计工程师必须知道 RC 网络实际上可视为信号路径上的低通滤波器,因此每当输入频率偏向 1/2pRC 所界定的电极时,RC 网络便会减弱取样信号。对于部分应用来说,模拟/数字转换器的增益非常重要,若这类系统不采用增益校正,便必须在上述情况下将取样信号减弱,这是系统优劣成败的关键。第二,采用的串联电阻也不可太大。虽然电阻值越大,运算放大器输出端的相位延迟便越少,运算放大器也就更加稳定,但缺点是与模拟/数字转换器输入端并行连接的内、外电容器便无法在模拟/数字转换器的“跟踪”时间内完成充电。一般来说,电阻值都低于 100W。第三,采用“跟踪”模式时,外置电容器必须比输入电容大很多倍。这样才可在模拟/数字转换器由“保持”模式切换为 “跟踪” 模式时将电容器出现的压降减至最少。

运算放大器需要多少建立时间完全取决于模拟/数字转换器的“跟踪”模式持续了多久。运算放大器要赶紧在模拟/数字转换器改用“保持”模式之前,利用这段“跟踪”时间为电容器补充充电,确保电容器储存足够的电压。利用输入引脚为电容器充电需要一段固定的时间,这个时间常数取决于串联电阻值及并行连接的内外电容器的电容值。运算放大器若无法在模拟/数字转换器进入“保持”模式之前稳定输入端的电压,数据的转换便会出现错误,而且数据会前后不一致。

我们若要寻找适当的 RI 电阻值及 CI 电容值,开始时可以按照模拟/数字转换器的取样频率设定 RC 网络的电极。若这个设定会令最高输入频率出现过大幅度的衰减,设计工程师可以相应调低有关的电容值或电阻值。设定最低电阻值时,应充分考虑运算放大器有多大的输出驱动能力。较小的电阻值比较理想,因为失真会较少。但我们必须保证放大器可在有关应用的整个输入频率范围内、以至在不同的振幅及温度下都能保持稳定。

传感器 电容 放大器 运算放大器 电压 ADC 滤波器 电容器 电流 电阻 电路 低通滤波器 模拟电路 CMOS 相关文章:

- 新型永磁同步电机控制芯片IRMCK203及其应用(01-16)

- AD698型LVDT信号调理电路的原理与应用(01-17)

- 带全速USB接口的PICl8F4550应用设计(04-12)

- 毫欧姆电阻在汽车电子系统中的应用(05-11)

- 利用双电机控制技术简化高能效电器设计(07-20)

- 为多路、多信号的快速扫描测量构建适当的数据采集系统(09-20)