如何加强信号路径的性能

时间:08-30

来源:互联网

点击:

如何管理元件的容错能力

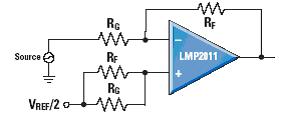

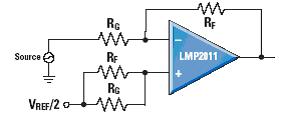

若果放大器配置采用反相放大器 (参看图4),我们便很容易计算出元件容错率所派生的错误系数。由于增益可定义为 – RF/RG,因此若选用最高值的 RF 搭配最低值的 RG,或者选用最低值的 RF 搭配最高值的 RG,那么实际的增益与理想的数字便会出现极大的差距。我们若使用 1% 容错度的电阻,错误率最高可达 2%。

图4 :反相放大器配置

对于没有加设增益校正电路的应用来说,模拟/数字转换器的动态范围必须限定在一定的范围之内。以 8 位的模拟/数字转换器为例来说,1 最低有效位 (LSB) 相当于参考电压的 0.39% (VREF/2n)。因此,电阻容错度产生的 2% 增益错误相当于动态范围失去 12 LSB ,比最高输出代码少 6 LSB (5.13 的约数),但比最低输出代码则多 6 LSB。

减低供电线路所产生的噪声

元件容错度是导致模拟/数字转换器信号路径出现错误的其中一个原因,而数字电路也会将噪声带进供电干线,这是信号路径出现错误的另一个原因。噪声会通过供电引脚混入模拟/数字转换器及运算放大器。一般来说,像 LMP2011 这类芯片都有卓越的电源抑制比 (PSRR),因此不会受噪声影响。但以 ADC121S101 这类模拟/数字转换器为例来说,其供电电压也同时是参考电压,而电源抑制比只有 0dB (亦即 PSRR 为零)。由于模拟/数字转换器的输出驱动器以极快的边缘率操作,因此模拟/数字转换器需要的供电量便会变化不定。混入输入供电线路的噪声可以干扰线路上的模拟/数字转换器及其他相连的模拟电路。若要有效抑制供电线路噪声而又没有其他更佳选择之前,加设两个超小型电容器的双电容器去耦电路设计不失为一个初步而又较为理想的方案,这个设计的其中一个电容器设于距离供电引脚一厘米之内的位置,其电容为 0.1mF (典型值),而另一电容器则设于附近,其电容则为1.0mF 至 10mF。若模拟及数字供电引脚都连接同一电源,我们可以在这

两条引脚之间加设扼流圈。这个扼流圈可视为直流电的短路,而且进行高频操作时若需要为电路提供隔离,这个扼流圈也可作为电阻提供隔离功能。

虽然能够将供电线路有效隔离总是好的,但最好还是尽量将模拟/数字转换器输出端的相对负载电容减至最少,以便转换器耗用较少电流。负载电容进行充电时会令供电线路出现噪声尖峰,而负载电容进行放电时则会将噪声带入模拟/数字转换器的基底。目前有几个方法可以将负载电容减至最少。最容易的方法是只驱动一颗芯片,但有关芯片须尽量置于靠近模拟/数字转换器输出端的位置。此外,我们也可采用串联电阻减低驱动负载电容所产生的影响。这个设计的优点是负载电容器进行充电或放电所需的电流会受到限制,而且输出的转换率也可降低。我们要确保串联电阻值不可超过 100W,以便符合数字电路的定时规定。串联电阻可能无法符合高频系统的要求,因此被驱动的电路必须尽量靠近模拟/数字转换器的输出端。

保持时钟信号的完整性

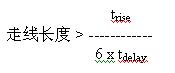

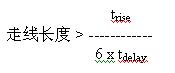

模拟/数字转换器的时钟线路与其输出端一样,可以将噪声带入系统。若时钟线路的长度超过其上升时间除以线迹延迟的 6 倍,时钟线路便应视为传输线路,其计算方法如下:

FR4 电路板的线迹延迟是每英吋 150ps (典型值)。若将线迹当作传输线路,线迹必须具备受控阻抗的特性,而且还须设有适当的终端装置,以免出现信号反射,导致失真情况出现。时钟波形一旦失真,便会导致每一时钟周期出现变化,这种变化情况一般称为抖动。时钟的定时时间一旦有变,模拟/数字转换器选取波形的确实地点便会不同。信号若出现抖动,模拟/数字转换器的取样点总是位于比理想取样点较高或较低的位置。由于信号取样过程出现时间的落差,噪声也就因此而起。1 LSB 的错误最高只能容许 1/2pfin 的抖动。若错误为 1/2 LSB,计算时可将 n+1 取代 n。

我们可以为线路加设终端装置,这是另一个可以避免线路出现反射现象的方法。线迹的终端装置分为两种,一种是近端终端装置,另一种是远端终端装置。若采用近端终端装置,电阻必须与靠近信号源输出端的线路串联一起。信号源与串联电阻的电阻值总和应相等于线路的特性阻抗。若近端终端装置无法满足要求,则必须采用远端终端装置。若采用远端终端装置,电阻必须在模拟/数字转换器的时钟输入端连接接地。终端电阻要尽量置于靠近模拟/数字转换器输入引脚的位置,而电阻值应相等于线路的特性阻抗。

系统若需要利用时钟源驱动多个不同的输入端,单靠远端终端装置可能并不足够。远端终端装置会减弱信号电平。若时钟源同时驱动多个输入端,而每一输入端都设有终端电阻,那么时钟电压可能会因此减弱,以致永远无法达到逻辑阈值。以上述例子来说,采用交流电终端装置较为理想。若采用交流电终端装置,便需要加设一个与电容器串联一起的电阻,而且这个电阻必须在模拟/数字转换器的输入端连接接地。这个设计可以减弱采用交流电的元件,但对采用直流电的元件则没有影响。以设有交流电终端装置的系统为例来说,振幅介于 0 伏与 5 伏之间的信号会以 2.5 伏作为中心点。时钟仍会被减弱,但会置于各个 CMOS 跳转点之间的最中心位置,确保信号振幅可以减至最少,以符合逻辑电平的规定。

若果放大器配置采用反相放大器 (参看图4),我们便很容易计算出元件容错率所派生的错误系数。由于增益可定义为 – RF/RG,因此若选用最高值的 RF 搭配最低值的 RG,或者选用最低值的 RF 搭配最高值的 RG,那么实际的增益与理想的数字便会出现极大的差距。我们若使用 1% 容错度的电阻,错误率最高可达 2%。

图4 :反相放大器配置

对于没有加设增益校正电路的应用来说,模拟/数字转换器的动态范围必须限定在一定的范围之内。以 8 位的模拟/数字转换器为例来说,1 最低有效位 (LSB) 相当于参考电压的 0.39% (VREF/2n)。因此,电阻容错度产生的 2% 增益错误相当于动态范围失去 12 LSB ,比最高输出代码少 6 LSB (5.13 的约数),但比最低输出代码则多 6 LSB。

减低供电线路所产生的噪声

元件容错度是导致模拟/数字转换器信号路径出现错误的其中一个原因,而数字电路也会将噪声带进供电干线,这是信号路径出现错误的另一个原因。噪声会通过供电引脚混入模拟/数字转换器及运算放大器。一般来说,像 LMP2011 这类芯片都有卓越的电源抑制比 (PSRR),因此不会受噪声影响。但以 ADC121S101 这类模拟/数字转换器为例来说,其供电电压也同时是参考电压,而电源抑制比只有 0dB (亦即 PSRR 为零)。由于模拟/数字转换器的输出驱动器以极快的边缘率操作,因此模拟/数字转换器需要的供电量便会变化不定。混入输入供电线路的噪声可以干扰线路上的模拟/数字转换器及其他相连的模拟电路。若要有效抑制供电线路噪声而又没有其他更佳选择之前,加设两个超小型电容器的双电容器去耦电路设计不失为一个初步而又较为理想的方案,这个设计的其中一个电容器设于距离供电引脚一厘米之内的位置,其电容为 0.1mF (典型值),而另一电容器则设于附近,其电容则为1.0mF 至 10mF。若模拟及数字供电引脚都连接同一电源,我们可以在这

两条引脚之间加设扼流圈。这个扼流圈可视为直流电的短路,而且进行高频操作时若需要为电路提供隔离,这个扼流圈也可作为电阻提供隔离功能。

虽然能够将供电线路有效隔离总是好的,但最好还是尽量将模拟/数字转换器输出端的相对负载电容减至最少,以便转换器耗用较少电流。负载电容进行充电时会令供电线路出现噪声尖峰,而负载电容进行放电时则会将噪声带入模拟/数字转换器的基底。目前有几个方法可以将负载电容减至最少。最容易的方法是只驱动一颗芯片,但有关芯片须尽量置于靠近模拟/数字转换器输出端的位置。此外,我们也可采用串联电阻减低驱动负载电容所产生的影响。这个设计的优点是负载电容器进行充电或放电所需的电流会受到限制,而且输出的转换率也可降低。我们要确保串联电阻值不可超过 100W,以便符合数字电路的定时规定。串联电阻可能无法符合高频系统的要求,因此被驱动的电路必须尽量靠近模拟/数字转换器的输出端。

保持时钟信号的完整性

模拟/数字转换器的时钟线路与其输出端一样,可以将噪声带入系统。若时钟线路的长度超过其上升时间除以线迹延迟的 6 倍,时钟线路便应视为传输线路,其计算方法如下:

FR4 电路板的线迹延迟是每英吋 150ps (典型值)。若将线迹当作传输线路,线迹必须具备受控阻抗的特性,而且还须设有适当的终端装置,以免出现信号反射,导致失真情况出现。时钟波形一旦失真,便会导致每一时钟周期出现变化,这种变化情况一般称为抖动。时钟的定时时间一旦有变,模拟/数字转换器选取波形的确实地点便会不同。信号若出现抖动,模拟/数字转换器的取样点总是位于比理想取样点较高或较低的位置。由于信号取样过程出现时间的落差,噪声也就因此而起。1 LSB 的错误最高只能容许 1/2pfin 的抖动。若错误为 1/2 LSB,计算时可将 n+1 取代 n。

我们可以为线路加设终端装置,这是另一个可以避免线路出现反射现象的方法。线迹的终端装置分为两种,一种是近端终端装置,另一种是远端终端装置。若采用近端终端装置,电阻必须与靠近信号源输出端的线路串联一起。信号源与串联电阻的电阻值总和应相等于线路的特性阻抗。若近端终端装置无法满足要求,则必须采用远端终端装置。若采用远端终端装置,电阻必须在模拟/数字转换器的时钟输入端连接接地。终端电阻要尽量置于靠近模拟/数字转换器输入引脚的位置,而电阻值应相等于线路的特性阻抗。

系统若需要利用时钟源驱动多个不同的输入端,单靠远端终端装置可能并不足够。远端终端装置会减弱信号电平。若时钟源同时驱动多个输入端,而每一输入端都设有终端电阻,那么时钟电压可能会因此减弱,以致永远无法达到逻辑阈值。以上述例子来说,采用交流电终端装置较为理想。若采用交流电终端装置,便需要加设一个与电容器串联一起的电阻,而且这个电阻必须在模拟/数字转换器的输入端连接接地。这个设计可以减弱采用交流电的元件,但对采用直流电的元件则没有影响。以设有交流电终端装置的系统为例来说,振幅介于 0 伏与 5 伏之间的信号会以 2.5 伏作为中心点。时钟仍会被减弱,但会置于各个 CMOS 跳转点之间的最中心位置,确保信号振幅可以减至最少,以符合逻辑电平的规定。

传感器 电容 放大器 运算放大器 电压 ADC 滤波器 电容器 电流 电阻 电路 低通滤波器 模拟电路 CMOS 相关文章:

- 新型永磁同步电机控制芯片IRMCK203及其应用(01-16)

- AD698型LVDT信号调理电路的原理与应用(01-17)

- 带全速USB接口的PICl8F4550应用设计(04-12)

- 毫欧姆电阻在汽车电子系统中的应用(05-11)

- 利用双电机控制技术简化高能效电器设计(07-20)

- 为多路、多信号的快速扫描测量构建适当的数据采集系统(09-20)