基于CCD的图像采集处理系统的研究

时间:08-30

来源:互联网

点击:

CCD是一种光电转换式图像传感器。它利用光电转换原理把图像信息直接转换成电信号,这样便实现了非电量的电测量。同时它还具有体积小、重量轻、噪声低、自扫描、工作速度快、测量精度高、寿命长等诸多优点,因此受到人们的高度重视,在精密测量、非接触无损检测、文件扫描与航空遥感等领域中,发挥着重要的作用。对被测图像信息进行快速采样、存储及数据处理,是线阵CCD数据采集发展的新方向。寻找满足要求的处理器已成当务之急。DSP(数字信号处理器)是一种具有高速性、实时性和丰富的芯片内部资源的处理器,它的出现为人们解决了这个难题。为了节约成本、减少体积,本文用CPLD控制图像的读入,以TMS320VC5402 DSP作为处理器,并结合CA3318CE A/D转换器介绍一种CCD图像采集处理系统的设计方法。根据课题研究,将此系统应用于手写体数字的采集和识别中。如果配以适当的光学系统,便可以实现光-机-电-算一体化设计。

1 系统概述

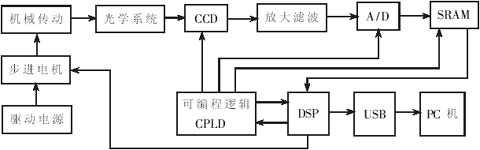

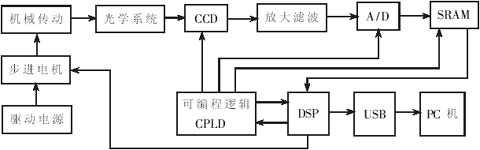

本系统主要由线阵CCD、ADC、DSP、可编程逻辑器件CPLD等几部分组成。待输入图像经光源照明后,经物镜成像在CCD光敏元件阵列上,CCD通过驱动电路完成一次Y方向的自扫描。在控制电路的作用下,CCD输出信号进行滤波放大处理,并经A/D转换电路进行数字化处理。一行图像数据通过数据通道进入帧存储器。以上操作与CCD自扫描同步进行,不受CPU的控制。随后,控制电路启动步进电机,带动进纸机构移动到下一采样位置,CCD又进行Y方向的自扫描,并重复上述过程,输入第二行的数据,直至整幅画面输入完毕。DSP读取存储器存储的处理数据,并根据用户的要求将处理结果上传给主机供用户使用。系统结构图如图1所示。

图1 系统结构图

2 基本硬件组成

2.1 线阵CCD传感器

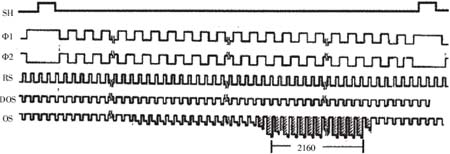

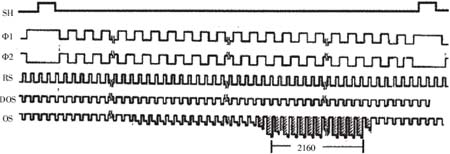

本系统采用TCD1208AP线阵CCD作为图像传感器。TCD1208AP是日本TOSHIBA公司生产的线阵CCD传感芯片,具有2160个像元,像元尺寸及间距为14μm×14μm;TCD1208AP具有灵敏度高、暗电流低等特点,工作电压为单一的5V,是二相输出的线阵CCD器件。主要用于通信传真、图像扫描、光学字符阅读机等场合。TCD1208AP传感器共需要四个5V的驱动时钟(SH、RS、Ф1、Ф2)。时序图如图2所示。

图2 TCD1208AP 传感器时序图

2.2 放大滤波及A/D转换

TCD1208AP传感器输出信号OS有以下特点:

·负极性信号

·包含有周期性的复位脉冲串扰

·有效信号幅值较小

CCD输出信号的上述特点决定了它不能直接送入A/D转换器,必须先从硬件上对其进行一系列的预处理,消除信号中的驱动脉冲(主要是复位脉冲)及噪声等所造成的干扰,因此需将信号进行前置反向、滤波及放大。在电路设计中,选用一片CA3450运算放大器进行反向、放大;并在CA3450的输出端接一级RC滤波器滤除噪声。经过上述处理的信号就可以被送入A/D转换器进行数字化处理。8位、高速、并行闪速结构的A/D转换芯片(CA3318CE)的转换速率(最大为15MHz)完全可以满足CCD(1MHz)的工作要求,利用A/D转换技术将信号转换成与之相应的、能够反应图像灰度变化的数字量,提高了测量精度和分辨率。当CA3318CE的输出使能有效时,就可以将A/D转换结果送至8位数据线上。这样,在数据存储器写允许及地址有效的前提下,就能将数据写入数据存储器SRAM中。

2.3 可编程逻辑电路CPLD

CPLD的主要作用有:用来控制CCD的驱动时钟、各种同步控制时钟(A/D转换,数字信号存取)以及存储器地址的产生。合适的CPLD是根据实际需要在实验过程中选定的,在设计中选用了ALTERA公司的MAX7000系列芯片EPM7128S,该系列芯片是典型的通过JTEG在线编程的CPLD器件。外部时钟信号作为CPLD的基准信号,其它时序信号的产生都是以此为基础的。

2.4 步进机构

线性CCD是逐行扫描的,要想得到清晰的图像,对步进机构的速度是有要求的。步进机构应该匀速运动,其速度必需和扫描速度保持一致。影响水平方向分辨率的主要原因是转动电机的转速。虽然转速越高,越节省时间,但是扫描间隔却相应增大,分辨率下降;转速越低,则分辨率越高。

2.5 TMS320VC5402处理器

TMS320VC5402是定点数字信号处理器,体系结构为哈佛结构,具有先进的多总线结构,40位算术逻辑单元(ALU)包括一个40位桶形移位寄存器和两个40位累加器,数据/程序寻址空间为64K/1MB,内置16KB的RAM和4KB的ROM,有两个缓冲串口。另外,它还提供DMA方式和多种片内外设,操作速度最高为100MIPS。

3 系统的硬件设计

3.1 CPLD控制信号

根据驱动脉冲时序关系确定时钟驱动信号SH、Φ1、Φ2和RS的参数。各路脉冲的技术指标如下:RS=1MHz,占空比为1:3,方波;Φ1=Φ2=0.5MHz,占空比为 1:1,方波,Φ1、Φ2在并行转移时是一个大于SH=1持续时间的宽脉冲;在SH的光积分时间内,至少有2212个RS脉冲。在设计中,SH波形采用计数器的形式进行设计。Φ1、Φ2、RS的波形由分频产生。行同步信号Фc与SH同周期,利用Фc的上升沿使A/D转换器进入工作状态(Фc为低电平时,A/D转换无法启动),它的上升沿对应CCD输出信号的第一个有效像素。SP是像元同步信号,它的脉冲频率是复位信号RS的整数倍。为了保证CCD输出、A/D转换、地址发生三者同步,将CCD驱动电路的RS与ADC的时钟CLK相连,存储器的写允许端与ADC的允许端相连。部分设计程序如下:

PROCESS(CLK,RESET)

BEGIN

IF RESET=‘1’ THEN CNTB<=0;

ELSE

IF CLK′EVENT AND CLK=‘1’ THEN

IF CNTB>2212 THEN CNTB<=0;

ELSE CNTB<=CNTB+1;

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(RESET,CNTB)

BEGIN

IF RESET=′1′ THEN SH<=′1′;

ELSE

CASE CNTB IS

WHEN 0 TO 2212=> SH<=‘0’;

WHEN OTHERS=> SH<=‘1’;

END CASE;

END IF;

END PROCESS;

PROCESS(CLK,RESET)

BEGIN

IF RESET=‘1’ THEN CNT<=0;

ELSE

IF CLK′EVENT AND CLK=‘1’ THEN

IF CNT<5 THEN

CNT<=CNT+1;

ELSE CNT<=0;

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CNT,RESET)

BEGIN

IF RESET=‘1’ THEN F1<=‘1’;F2<=‘0’;

ELSE

CASE CNT IS

WHEN 0 =>F1<=‘1’;F2<=‘0’;

WHEN 4 =>F1<=‘1’;F2<=‘0’;

WHEN 5 =>F1<=‘1

’;F2<=‘0’;

WHEN OTHERS=> F1<=‘0’;F2<=‘1’;

END CASE;

END IF;

END PROCESS;

根据所要摄取图像的数据量,选用三片IS61LV5128AL-12T SRAM(共1.5M),用来存放一帧图像数据。它们的地址线和读写控制线是由CPLD提供的。

SRAM地址信号的产生是通过计数器实现的,这里将A/D转换的时钟同步信号作为计数器的计数时钟信号。每次采样前,设初始地址为零,时钟同步信号每出现一次下降沿,地址值加1。在采集完一帧数据时地址自动复位。考虑到延时的问题,数据信号与地址信号不能同时发生。如果写信号一直有效,会造成同一地址存放不同的数据,从而影响了输出数据的正确性。针对这一问题,在设置写信号WR时,检测地址ADDR最后一位(ADDR[0])和时钟同步信号的上升沿的变化。当检测到ADDR[0]变化时,WR置低,说明有效;当检测到时钟同步信号上升沿到来时,WR置高,此时无效。这样每一位数据都能被写入相应的地址中。

在设计中,时序发生器产生的所有驱动和控制时序信号都是在MUXPLUSII开发环境下设计完成并经编译、校验后在线下载到CPLD器件内部的。可见,一片CPLD可以替代原来的几十个分立元件来实现CCD图像读入系统中各种驱动和控制时序逻辑,而且CPLD还允许设计编程保密位。总之采用CPLD有利于减小系统电路板的面积、提高系统的安全保密性、降低系统功耗和保证产品的质量。

1 系统概述

本系统主要由线阵CCD、ADC、DSP、可编程逻辑器件CPLD等几部分组成。待输入图像经光源照明后,经物镜成像在CCD光敏元件阵列上,CCD通过驱动电路完成一次Y方向的自扫描。在控制电路的作用下,CCD输出信号进行滤波放大处理,并经A/D转换电路进行数字化处理。一行图像数据通过数据通道进入帧存储器。以上操作与CCD自扫描同步进行,不受CPU的控制。随后,控制电路启动步进电机,带动进纸机构移动到下一采样位置,CCD又进行Y方向的自扫描,并重复上述过程,输入第二行的数据,直至整幅画面输入完毕。DSP读取存储器存储的处理数据,并根据用户的要求将处理结果上传给主机供用户使用。系统结构图如图1所示。

图1 系统结构图

2 基本硬件组成

2.1 线阵CCD传感器

本系统采用TCD1208AP线阵CCD作为图像传感器。TCD1208AP是日本TOSHIBA公司生产的线阵CCD传感芯片,具有2160个像元,像元尺寸及间距为14μm×14μm;TCD1208AP具有灵敏度高、暗电流低等特点,工作电压为单一的5V,是二相输出的线阵CCD器件。主要用于通信传真、图像扫描、光学字符阅读机等场合。TCD1208AP传感器共需要四个5V的驱动时钟(SH、RS、Ф1、Ф2)。时序图如图2所示。

图2 TCD1208AP 传感器时序图

2.2 放大滤波及A/D转换

TCD1208AP传感器输出信号OS有以下特点:

·负极性信号

·包含有周期性的复位脉冲串扰

·有效信号幅值较小

CCD输出信号的上述特点决定了它不能直接送入A/D转换器,必须先从硬件上对其进行一系列的预处理,消除信号中的驱动脉冲(主要是复位脉冲)及噪声等所造成的干扰,因此需将信号进行前置反向、滤波及放大。在电路设计中,选用一片CA3450运算放大器进行反向、放大;并在CA3450的输出端接一级RC滤波器滤除噪声。经过上述处理的信号就可以被送入A/D转换器进行数字化处理。8位、高速、并行闪速结构的A/D转换芯片(CA3318CE)的转换速率(最大为15MHz)完全可以满足CCD(1MHz)的工作要求,利用A/D转换技术将信号转换成与之相应的、能够反应图像灰度变化的数字量,提高了测量精度和分辨率。当CA3318CE的输出使能有效时,就可以将A/D转换结果送至8位数据线上。这样,在数据存储器写允许及地址有效的前提下,就能将数据写入数据存储器SRAM中。

2.3 可编程逻辑电路CPLD

CPLD的主要作用有:用来控制CCD的驱动时钟、各种同步控制时钟(A/D转换,数字信号存取)以及存储器地址的产生。合适的CPLD是根据实际需要在实验过程中选定的,在设计中选用了ALTERA公司的MAX7000系列芯片EPM7128S,该系列芯片是典型的通过JTEG在线编程的CPLD器件。外部时钟信号作为CPLD的基准信号,其它时序信号的产生都是以此为基础的。

2.4 步进机构

线性CCD是逐行扫描的,要想得到清晰的图像,对步进机构的速度是有要求的。步进机构应该匀速运动,其速度必需和扫描速度保持一致。影响水平方向分辨率的主要原因是转动电机的转速。虽然转速越高,越节省时间,但是扫描间隔却相应增大,分辨率下降;转速越低,则分辨率越高。

2.5 TMS320VC5402处理器

TMS320VC5402是定点数字信号处理器,体系结构为哈佛结构,具有先进的多总线结构,40位算术逻辑单元(ALU)包括一个40位桶形移位寄存器和两个40位累加器,数据/程序寻址空间为64K/1MB,内置16KB的RAM和4KB的ROM,有两个缓冲串口。另外,它还提供DMA方式和多种片内外设,操作速度最高为100MIPS。

3 系统的硬件设计

3.1 CPLD控制信号

根据驱动脉冲时序关系确定时钟驱动信号SH、Φ1、Φ2和RS的参数。各路脉冲的技术指标如下:RS=1MHz,占空比为1:3,方波;Φ1=Φ2=0.5MHz,占空比为 1:1,方波,Φ1、Φ2在并行转移时是一个大于SH=1持续时间的宽脉冲;在SH的光积分时间内,至少有2212个RS脉冲。在设计中,SH波形采用计数器的形式进行设计。Φ1、Φ2、RS的波形由分频产生。行同步信号Фc与SH同周期,利用Фc的上升沿使A/D转换器进入工作状态(Фc为低电平时,A/D转换无法启动),它的上升沿对应CCD输出信号的第一个有效像素。SP是像元同步信号,它的脉冲频率是复位信号RS的整数倍。为了保证CCD输出、A/D转换、地址发生三者同步,将CCD驱动电路的RS与ADC的时钟CLK相连,存储器的写允许端与ADC的允许端相连。部分设计程序如下:

PROCESS(CLK,RESET)

BEGIN

IF RESET=‘1’ THEN CNTB<=0;

ELSE

IF CLK′EVENT AND CLK=‘1’ THEN

IF CNTB>2212 THEN CNTB<=0;

ELSE CNTB<=CNTB+1;

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(RESET,CNTB)

BEGIN

IF RESET=′1′ THEN SH<=′1′;

ELSE

CASE CNTB IS

WHEN 0 TO 2212=> SH<=‘0’;

WHEN OTHERS=> SH<=‘1’;

END CASE;

END IF;

END PROCESS;

PROCESS(CLK,RESET)

BEGIN

IF RESET=‘1’ THEN CNT<=0;

ELSE

IF CLK′EVENT AND CLK=‘1’ THEN

IF CNT<5 THEN

CNT<=CNT+1;

ELSE CNT<=0;

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CNT,RESET)

BEGIN

IF RESET=‘1’ THEN F1<=‘1’;F2<=‘0’;

ELSE

CASE CNT IS

WHEN 0 =>F1<=‘1’;F2<=‘0’;

WHEN 4 =>F1<=‘1’;F2<=‘0’;

WHEN 5 =>F1<=‘1

’;F2<=‘0’;

WHEN OTHERS=> F1<=‘0’;F2<=‘1’;

END CASE;

END IF;

END PROCESS;

根据所要摄取图像的数据量,选用三片IS61LV5128AL-12T SRAM(共1.5M),用来存放一帧图像数据。它们的地址线和读写控制线是由CPLD提供的。

SRAM地址信号的产生是通过计数器实现的,这里将A/D转换的时钟同步信号作为计数器的计数时钟信号。每次采样前,设初始地址为零,时钟同步信号每出现一次下降沿,地址值加1。在采集完一帧数据时地址自动复位。考虑到延时的问题,数据信号与地址信号不能同时发生。如果写信号一直有效,会造成同一地址存放不同的数据,从而影响了输出数据的正确性。针对这一问题,在设置写信号WR时,检测地址ADDR最后一位(ADDR[0])和时钟同步信号的上升沿的变化。当检测到ADDR[0]变化时,WR置低,说明有效;当检测到时钟同步信号上升沿到来时,WR置高,此时无效。这样每一位数据都能被写入相应的地址中。

在设计中,时序发生器产生的所有驱动和控制时序信号都是在MUXPLUSII开发环境下设计完成并经编译、校验后在线下载到CPLD器件内部的。可见,一片CPLD可以替代原来的几十个分立元件来实现CCD图像读入系统中各种驱动和控制时序逻辑,而且CPLD还允许设计编程保密位。总之采用CPLD有利于减小系统电路板的面积、提高系统的安全保密性、降低系统功耗和保证产品的质量。

传感器 DSP CPLD ADC 电路 步进电机 电流 电压 放大器 滤波器 LTE 总线 MIPS 电子 相关文章:

- 新型永磁同步电机控制芯片IRMCK203及其应用(01-16)

- AD698型LVDT信号调理电路的原理与应用(01-17)

- 带全速USB接口的PICl8F4550应用设计(04-12)

- 毫欧姆电阻在汽车电子系统中的应用(05-11)

- 利用双电机控制技术简化高能效电器设计(07-20)

- 为多路、多信号的快速扫描测量构建适当的数据采集系统(09-20)