基于TLV1562的4通道高速实时数据采集系统的设计

时间:08-30

来源:互联网

点击:

引 言

在雷达杂波对消器设计中,传统的方法是采用中频对消,即杂波的抑制在中频上实现。早期的中频对消器常采用SAW和CCD等模拟延时线。由于数字信号处理所具有的突出优点,尤其是数字集成电路的发展以及可编程逻辑器件功能的日益强大,使得数字式矢量对消器成为当前及今后的主要工作模式。 而对雷达信号的采集与处理成为最为关键的环节,在设计中笔者选择了10位高速低功耗可重配置TLV1562,在较低成本下实现了多通道数据采集处理。

系统设计与实现

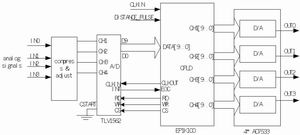

系统框图如图1所示,以TLV1562为核心的前端采集系统是整个系统的一部分。整个系统由信号调理、信号采样、高速信号处理(数字对消)以及波形回放等组成。信号调理电路是对经相干检波送来的信号进行压缩调整以满足TLV1562的采样电平;信号采样是完 成模拟信号的数字化(由TLV1562完成);高速数字信号处理是在CPLD内完成数字式对消算法;由AD7533构成的波形回放部分是将对消处理过的信号送到显示屏显示。

图1 雷达对消器系统框图

信号调理电路与A/D参考基准源

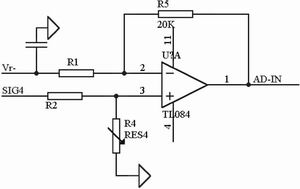

由于对于规定的电源电压AVDD,TLV1562的模拟输入信号的范围为0.8V(AVDD-1.9伏),所以必须要对相干检波出来的模拟信号进行处理,使其满足要求。设计中,采用如图2所示的调理电路,R4用来调整输入信号SIG4的幅度范围,Vr-是由TL431调整出来的一个基准电压,用来控制信号的直流电压。

图2 信号调理电路

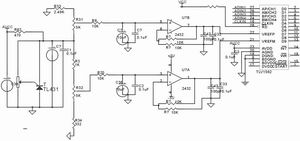

TLV1562有两个基准输入引脚—REFP和REFM。这两个引脚上的电平分别是产生满度和零度读数的模拟输入的上下限。根据要求基准电压必须满足下列条件:

VREFP<=AVDD-1V

AGND+0.9V<VREFM

3V>=(VREFP-VREFM)>=0.8V

所以设计中采用图3所示的基准设计。通过调整R31和R32,使VREFP与VREFM满足上诉要求。

图3 基准电路设计

采集系统

CPLD与TLV1562的接口时序图见图4。DISTANCE_PULSE是距离门脉冲,周期为512μs(80Km)或1024μs(160Km),SAMPLE_PULSE是采样开始脉冲,一旦监测到其上升沿采集系统就开始启动,START被置为高电平,TLV1562的CS置为低。WR、RD、INT的时序图是TLV1562的内部转换模式时序图。当WR出现两次低电平后,便完成了对寄存器CR0和CR1的配置,即实现了A/D转换的初始化。A/D转换结束,输出低电平信号INT有效,信号RD读取A/D转换结果并复位INT信号,完成一个转换周期,并开始准备下一次转换。

图4 EP1K100与TLV1562的接口时序图

由于TLV1562芯片是可配置A/D转换器,所以如何利用CPLD实现对TLV1562的配置与读写是关键技术之一。对于TLV1562的读写控制易于实现,而对于其配置,由于是对四通道循环采集,较为复杂。在TLV1562中有两个寄存器需要配置,也就是要有两次写,而每次配置的数据还不一样,所以应该在每次写的时候都应相应的提供数据。整个配置过程用VHDL语言采用有限状态机的方式来实现。定义5个状态:st0,st1,st2,st3,st4,st0是空闲态,st1,st2,st3,st4是对应相应采集通道的状态,INDEXREG[10]是用来监测写信号的第几次写的标识码。 程序如下:

type states is (st0,st1,st2,st3,ST4);

signal current_state,next_state :states :=st0;

signal indexreg:STD_LOGIC_vector(1 downto 0);

signal chanel_data: STD_LOGIC_vector(9 downto 0);

begin

indexreg<=index_reg; cs<=not start;

process(current_state,indexreg,ad_ale)

begin

if ad_ale='0' then

chanel_data<="ZZZZZZZZZZ";

else

if indexreg="10" then

chanel_data<="0100000100";

else

case current_state is

when st0=>ad_end<='0';

chanel<="00";

next_state<=st1;

chanel_data<="0011000000";

when st1=> ad_end<='0';chanel<="01";

n ext_state<=st2;

chanel_data<="0011000001";

when st2=> ad_end<='0';chanel<="10";

next_state<=st3;

chanel_data<="0011000010";

when st3=> ad_end<='1';chanel<="11";

next_state<=st0;

chanel_data<="0011000011";

when st4=> next_state<=st0;

chanel_data<="0011000000";

when others=> ad_end<='1';

next_state<=st0;

chanel_data<="0011000000";

end case;

end if;

end if;

end process;

在雷达杂波对消器设计中,传统的方法是采用中频对消,即杂波的抑制在中频上实现。早期的中频对消器常采用SAW和CCD等模拟延时线。由于数字信号处理所具有的突出优点,尤其是数字集成电路的发展以及可编程逻辑器件功能的日益强大,使得数字式矢量对消器成为当前及今后的主要工作模式。 而对雷达信号的采集与处理成为最为关键的环节,在设计中笔者选择了10位高速低功耗可重配置TLV1562,在较低成本下实现了多通道数据采集处理。

系统设计与实现

系统框图如图1所示,以TLV1562为核心的前端采集系统是整个系统的一部分。整个系统由信号调理、信号采样、高速信号处理(数字对消)以及波形回放等组成。信号调理电路是对经相干检波送来的信号进行压缩调整以满足TLV1562的采样电平;信号采样是完 成模拟信号的数字化(由TLV1562完成);高速数字信号处理是在CPLD内完成数字式对消算法;由AD7533构成的波形回放部分是将对消处理过的信号送到显示屏显示。

图1 雷达对消器系统框图

信号调理电路与A/D参考基准源

由于对于规定的电源电压AVDD,TLV1562的模拟输入信号的范围为0.8V(AVDD-1.9伏),所以必须要对相干检波出来的模拟信号进行处理,使其满足要求。设计中,采用如图2所示的调理电路,R4用来调整输入信号SIG4的幅度范围,Vr-是由TL431调整出来的一个基准电压,用来控制信号的直流电压。

图2 信号调理电路

TLV1562有两个基准输入引脚—REFP和REFM。这两个引脚上的电平分别是产生满度和零度读数的模拟输入的上下限。根据要求基准电压必须满足下列条件:

VREFP<=AVDD-1V

AGND+0.9V<VREFM

3V>=(VREFP-VREFM)>=0.8V

所以设计中采用图3所示的基准设计。通过调整R31和R32,使VREFP与VREFM满足上诉要求。

图3 基准电路设计

采集系统

CPLD与TLV1562的接口时序图见图4。DISTANCE_PULSE是距离门脉冲,周期为512μs(80Km)或1024μs(160Km),SAMPLE_PULSE是采样开始脉冲,一旦监测到其上升沿采集系统就开始启动,START被置为高电平,TLV1562的CS置为低。WR、RD、INT的时序图是TLV1562的内部转换模式时序图。当WR出现两次低电平后,便完成了对寄存器CR0和CR1的配置,即实现了A/D转换的初始化。A/D转换结束,输出低电平信号INT有效,信号RD读取A/D转换结果并复位INT信号,完成一个转换周期,并开始准备下一次转换。

图4 EP1K100与TLV1562的接口时序图

由于TLV1562芯片是可配置A/D转换器,所以如何利用CPLD实现对TLV1562的配置与读写是关键技术之一。对于TLV1562的读写控制易于实现,而对于其配置,由于是对四通道循环采集,较为复杂。在TLV1562中有两个寄存器需要配置,也就是要有两次写,而每次配置的数据还不一样,所以应该在每次写的时候都应相应的提供数据。整个配置过程用VHDL语言采用有限状态机的方式来实现。定义5个状态:st0,st1,st2,st3,st4,st0是空闲态,st1,st2,st3,st4是对应相应采集通道的状态,INDEXREG[10]是用来监测写信号的第几次写的标识码。 程序如下:

type states is (st0,st1,st2,st3,ST4);

signal current_state,next_state :states :=st0;

signal indexreg:STD_LOGIC_vector(1 downto 0);

signal chanel_data: STD_LOGIC_vector(9 downto 0);

begin

indexreg<=index_reg; cs<=not start;

process(current_state,indexreg,ad_ale)

begin

if ad_ale='0' then

chanel_data<="ZZZZZZZZZZ";

else

if indexreg="10" then

chanel_data<="0100000100";

else

case current_state is

when st0=>ad_end<='0';

chanel<="00";

next_state<=st1;

chanel_data<="0011000000";

when st1=> ad_end<='0';chanel<="01";

n ext_state<=st2;

chanel_data<="0011000001";

when st2=> ad_end<='0';chanel<="10";

next_state<=st3;

chanel_data<="0011000010";

when st3=> ad_end<='1';chanel<="11";

next_state<=st0;

chanel_data<="0011000011";

when st4=> next_state<=st0;

chanel_data<="0011000000";

when others=> ad_end<='1';

next_state<=st0;

chanel_data<="0011000000";

end case;

end if;

end if;

end process;

- 基于新型ASSP LTC3455的硬盘MP3电源设计(06-07)

- 单片彩色LCoS显示系统的设计实现(09-09)

- 具有开关电源通路管理的下一代电源管理集成电路(08-28)

- 如何利用DCP获得更精确的性能(10-01)

- 集成电路的种类与用途(09-20)

- CMOS集成电路中ESD保护技术研究(10-17)