揭秘HDTV的“内芯”世界-分量模拟接口AD9883A

时间:08-30

来源:互联网

点击:

AD9883A的应用

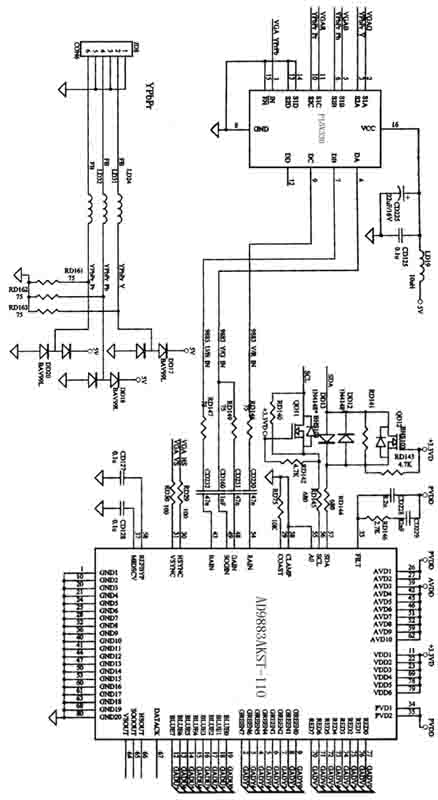

图3是以AD9883AKST-110(AD9883A的一种)为核心的典型高清电视的模拟分量视频信号解码电路。电路中PVDD为PLL供电电源,AVDD为模拟部分供电电源,均为3.3V;“3.3VD”为数字部分供电电源;电路工作原理如下。

图3 AD9883A应用电路图

两组模拟分量视频信号YPbPr(逐行分量576P、480P和高清分量1080i、720P)、RGB(计算机格式VGA—SXGA)经切换选择电路P15V330,由CPU发出的VGA YPrPb控制信号控制P15V330的选择输出。当VGA YPrPb="0时",选择RGB输出;当VGA YPrPb="1时",选择YPbPr输出。YPbPr的同步脉冲包含在Y信号中。Y/G信号还通过CD160输入SOGIN,以便在SOGOUT脚产生包含行场同步信息的复合同步信号。计算机格式VGA-SXGA的行同步(HSYNC)信号、场同步(VSYNC)信号输入到AD9883A的HSYNC和VSYNC。

从CPU的CLK和DATA输出的I2C控制信号,被外接的QD11、QD12构成的电平转换电路进行电平转换后连接到AD9883A的SCL和SDA,对ADC进行控制设定。

AD9883A在I2C控制信号的控制下,同时根据输入的行、场同步信号的频率及极性,以及第33脚输入的滤波值,将输入的行频信号分频成与输入信号格式变化频率相适应的采样时钟。另一方面, AD9883A根据I2C控制信号设定的相位、钳位电平及增益等,按照新分频得到采样时钟频率对输入的模拟分量视频信号进行数字化采样,转换成数字分量视频信号。

数字化后的数字分量视频信号分别从AD9883A中各自的通道中输出,分别经缓冲后,输出给后级的图像处理芯片。

在ADC内形成的时钟信号从其第67脚输出,G信号复合同步输出SOGOUT、经过相位调整的行同步输出HSOUT和场同步输出VSOUT分别经AD9883A的65、66和64脚输出。这些信号分别输出到后级的图像处理芯片。

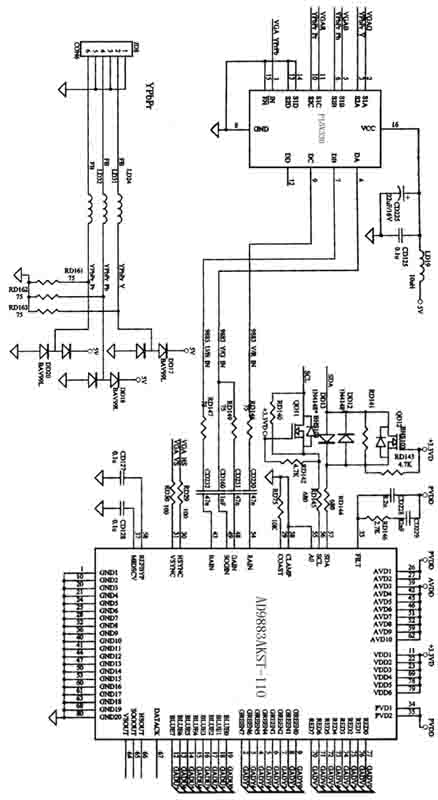

图3是以AD9883AKST-110(AD9883A的一种)为核心的典型高清电视的模拟分量视频信号解码电路。电路中PVDD为PLL供电电源,AVDD为模拟部分供电电源,均为3.3V;“3.3VD”为数字部分供电电源;电路工作原理如下。

图3 AD9883A应用电路图

两组模拟分量视频信号YPbPr(逐行分量576P、480P和高清分量1080i、720P)、RGB(计算机格式VGA—SXGA)经切换选择电路P15V330,由CPU发出的VGA YPrPb控制信号控制P15V330的选择输出。当VGA YPrPb="0时",选择RGB输出;当VGA YPrPb="1时",选择YPbPr输出。YPbPr的同步脉冲包含在Y信号中。Y/G信号还通过CD160输入SOGIN,以便在SOGOUT脚产生包含行场同步信息的复合同步信号。计算机格式VGA-SXGA的行同步(HSYNC)信号、场同步(VSYNC)信号输入到AD9883A的HSYNC和VSYNC。

从CPU的CLK和DATA输出的I2C控制信号,被外接的QD11、QD12构成的电平转换电路进行电平转换后连接到AD9883A的SCL和SDA,对ADC进行控制设定。

AD9883A在I2C控制信号的控制下,同时根据输入的行、场同步信号的频率及极性,以及第33脚输入的滤波值,将输入的行频信号分频成与输入信号格式变化频率相适应的采样时钟。另一方面, AD9883A根据I2C控制信号设定的相位、钳位电平及增益等,按照新分频得到采样时钟频率对输入的模拟分量视频信号进行数字化采样,转换成数字分量视频信号。

数字化后的数字分量视频信号分别从AD9883A中各自的通道中输出,分别经缓冲后,输出给后级的图像处理芯片。

在ADC内形成的时钟信号从其第67脚输出,G信号复合同步输出SOGOUT、经过相位调整的行同步输出HSOUT和场同步输出VSOUT分别经AD9883A的65、66和64脚输出。这些信号分别输出到后级的图像处理芯片。

ADC 总线 电路 电子 CMOS 连接器 PCB 电阻 比较器 模拟电路 电容 电压 电流 滤波器 电路图 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)