基于ADSP-BF533处理器的滤波器的实现及优化

时间:08-02

来源:互联网

点击:

4 优化实现的结果

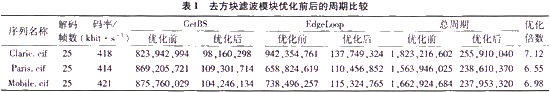

测试优化效果的方法是将参考代码JM8.6中的去方块滤波C程序模块加到原有的解码器中进行测试,并与经过系统、算法、汇编3个级别优化的去方块滤波汇编程序模块的测试周期进行对比。选择的测试图像序列为Clarie.cif、Paris.cif、Mobile.cif,测试数据见表1。

由表1可以看出,与未优化前的JM8.6中的C程序代码相比,经过优化后的去方块滤波汇编模块效率提高了7倍左右。

5 结束语

本文通过系统、算法及汇编3个级别优化实现了H.264中的去方块滤波功能,特别是通过改进去方块滤波的实现算法,对待滤波的宏块进行分类以及充分地利用并行指令、向量指令等汇编级别的优化手段,取得了较好的优化效果。优化实现的去方块滤波模块,基于原有的H.264解码器上对一个25帧约400 kbit/s的图像序列进行滤波,大概需要250 MHz的时钟周期,而解码器的总周期约为700 MHz的时钟周期,从而使得解码器的解码速度达到约20帧/s,基本达到准实时解码的要求。

该实现方法相对于参考模块进行了较好的优化,但通过对程序进行耗时分析,在读取待滤波数据和重新写入已滤波的数据,获取BS值的GetBs函数和进行滤波的EdgeLoop函数方面都还有进一步提升的空间。对于片外片内数据的交互可以采用DMA技术,在滤波的同时进行数据读写,从而抵消数据搬移消耗的时钟周期;对于GetBs和EdgeLoop中的汇编代码实现效率还有进一步改进的空间;这两方面也是下一步的改进方向。

解码器 滤波器 ADI DSP 电源管理 电压 C语言 总线 相关文章:

- 视频解码器SAA7111在图像采集中的应用(06-21)

- 基于CPLD和VS1011E解码器的电梯语音系统设计(11-26)

- 基于ARM核的音频解码器单芯片系统(01-05)

- H.264解码器中一种新颖的去块效应滤波器设计(10-21)

- 在高清显示器上优化标清视频(08-15)

- 应用于汽车电子的音频插孔开关(06-27)