H.264解码器中一种新颖的去块效应滤波器设计

时间:10-21

来源:EDN

点击:

引 言

图像的编解码技术是多媒体技术的关键,H.264/AVC是国际上最先进的视频压缩技术,其主要特点是采用小尺寸整数余弦变换、1/4像素的运动估计精度、多参考帧预测,基于上下文可变长度编码和环路内去块效应滤波器等技术。由于去块效应滤波器大约占整个解码器1/3的运算量,因此该部分的设计成为整个解码器设计的瓶颈,在此研究了一种新颖的环路内去块效应滤波器设计。设计中采用5阶流水线的去块效应模块,利用混合滤波顺序与打乱的存储更新机制的方法提高了流水线畅顺性,滤波一个16×16大小的宏块仅需要198个时钟周期。

1 H.264/AVC的去块效应

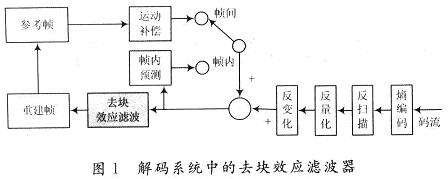

在基于块的视频编码方法中,各个块的编解码是互相独立的,由于预测、补偿、变化、量化等引起块与块之间的边界处会产生不连续,因此新版H.264/AVC标准采用了环路内去块滤波器来解决每个16×16宏块重建后的边界扭曲问题。去块效应滤波有两种方法:后处理去块效应滤波;环路内去块效应滤波。H.264/AVC采用环路内去块效应滤波(见图1),即滤波后的帧作为后面预测的参考帧。与之前的H.263或MPEG的滤波器相比较,新版H.264标准采用的滤波器基于更小的4×4的基本宏块,基本宏块的边界根据片级/宏块级的特性与根据像素穿过滤波边界的渐变度,对需要滤波的宏块边界进行有条件的滤波。重建帧的每个像素都需要从外部存储器中重调出来以进行滤波处理或作为相邻像素来判断当前像素是否需要进行滤波。显然,这些操作需要消耗巨大的存储器带宽,对像素值进行修改。

本文设计的去块效应滤波模块采用流水线技术来提高系统吞吐量。理想流水线的高效率实现基于相邻的滤波操作没有数据性。文献[3,4]采用了非流水线的架构,因此无法提高系统的吞吐量。而对于流水线架构,如若不优化滤波顺序与存储器访问次序,则所产生的数据与结构冒险也将大大降低流水线的效率。有人使用双端口的片上SRAM来减少片外存储器的带宽,增加了系统的吞吐量,但是双端口存储器面积较大且增加功耗。与流水线的滤波器相比,非流水线滤波器的操作(包括条件判断、查表、像素计算等)是顺序化的,即每个时钟仅处理一个操作类型,因此它所能达到的最大系统频率要低很多。

采用不同的边界滤波顺序,会大大的影响去块效应滤波器的性能。在H.264/AVC标准中,每个宏块的滤波顺序得到了描述,只要保持滤波数据依赖性,H.264/AVC标准所描述的滤波顺序可以被改进。其滤波顺序包括两类:顺序滤波和混合滤波。但是其滤波顺序以及相应的存储更新机制都是针对非流水线结构的,因此如果直接将之应用于本文的流水线设计,就有可能引发严重的竞争与冒险从而降低流水线的性能。

2 去块效应滤波器的存储管理与滤波算法

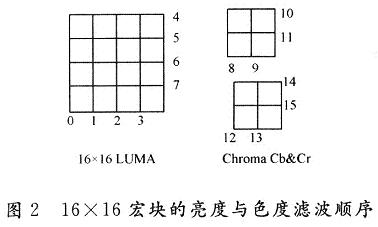

H.264/AvC标准基于4×4宏块作为滤波的基本宏块,它有5种滤波强度,分别是Bs=0,1,2,3,4。滤波方式分为强滤波、标准滤波和直通3种方式,其中强滤波影响边界两边的共6个像素,标准滤波影响边界两边的共4个像素,直通方式不修改边界两侧的像素。H.264/AVC标准规定先对垂直边界进行滤波,然后再对水平边界进行滤波,只有对垂直与水平边界全部滤波完成后,才可以对下一个宏块进行滤波。同一个宏块中,先对亮度部分进行滤波,再对色度部分进行滤波;色度部分滤波时,先对C6部分进行滤波,再对Cr部分进行滤波,对整个16×16宏块的滤波顺序如图2所示。

(1)边界滤波强度与像素滤波的存储器

按照H.264/AVC的标准,需要对被滤波的边界两侧的像素进行有条件的滤波。该条件决定于边界强度BS与像素穿越边界的倾斜度。边界强度BS:0,1,2,3或4,在进行滤波之前被赋给相应的边界。BS=4表示强滤波,BS=0表示不需要进行滤波,即直通方式;否则,BS=1,2,3表示中等强度的滤波,色度部分边界的滤波强度与对应亮度部分是相同的。滤波每条水平或垂直边界需要被提供边界两边的8个像素,p0~p3&q0~q3;需要更新的像素共6个或4个:p0~p2&q0~q2或声p0,p1&q0,q1。

对一个16×16宏块进行滤波需要提供左边相邻像素、右边相邻像素和本宏块的像素。对于宏块边界,比如最左边界与最右边界而言,p0~p3与q0~q3来自不同的模块(即分别来自相邻宏块的像素与本宏块的像素);对于非16×16宏块的边界滤波,像素p0~p3与q0~q3均来自16×16宏块本身,因此至少需要4个存储单元:左相邻像素存储单元、上相邻像素存储单元、本身模块的像素存储单元和转换缓冲单元,每个存储单元的带宽是32位。

当滤波从垂直边界向水平边界变换时,为了方便滤波过程中的存储器访问,这里利用额外的转换缓冲器BUF0~BUF3来缓存中间滤波数据,采用转换缓冲器后获取一行或一列像素的值(即p0~p3&q0~q3)只需要1个时钟周期,否则需要4个时钟周期。

图像的编解码技术是多媒体技术的关键,H.264/AVC是国际上最先进的视频压缩技术,其主要特点是采用小尺寸整数余弦变换、1/4像素的运动估计精度、多参考帧预测,基于上下文可变长度编码和环路内去块效应滤波器等技术。由于去块效应滤波器大约占整个解码器1/3的运算量,因此该部分的设计成为整个解码器设计的瓶颈,在此研究了一种新颖的环路内去块效应滤波器设计。设计中采用5阶流水线的去块效应模块,利用混合滤波顺序与打乱的存储更新机制的方法提高了流水线畅顺性,滤波一个16×16大小的宏块仅需要198个时钟周期。

1 H.264/AVC的去块效应

在基于块的视频编码方法中,各个块的编解码是互相独立的,由于预测、补偿、变化、量化等引起块与块之间的边界处会产生不连续,因此新版H.264/AVC标准采用了环路内去块滤波器来解决每个16×16宏块重建后的边界扭曲问题。去块效应滤波有两种方法:后处理去块效应滤波;环路内去块效应滤波。H.264/AVC采用环路内去块效应滤波(见图1),即滤波后的帧作为后面预测的参考帧。与之前的H.263或MPEG的滤波器相比较,新版H.264标准采用的滤波器基于更小的4×4的基本宏块,基本宏块的边界根据片级/宏块级的特性与根据像素穿过滤波边界的渐变度,对需要滤波的宏块边界进行有条件的滤波。重建帧的每个像素都需要从外部存储器中重调出来以进行滤波处理或作为相邻像素来判断当前像素是否需要进行滤波。显然,这些操作需要消耗巨大的存储器带宽,对像素值进行修改。

|

本文设计的去块效应滤波模块采用流水线技术来提高系统吞吐量。理想流水线的高效率实现基于相邻的滤波操作没有数据性。文献[3,4]采用了非流水线的架构,因此无法提高系统的吞吐量。而对于流水线架构,如若不优化滤波顺序与存储器访问次序,则所产生的数据与结构冒险也将大大降低流水线的效率。有人使用双端口的片上SRAM来减少片外存储器的带宽,增加了系统的吞吐量,但是双端口存储器面积较大且增加功耗。与流水线的滤波器相比,非流水线滤波器的操作(包括条件判断、查表、像素计算等)是顺序化的,即每个时钟仅处理一个操作类型,因此它所能达到的最大系统频率要低很多。

采用不同的边界滤波顺序,会大大的影响去块效应滤波器的性能。在H.264/AVC标准中,每个宏块的滤波顺序得到了描述,只要保持滤波数据依赖性,H.264/AVC标准所描述的滤波顺序可以被改进。其滤波顺序包括两类:顺序滤波和混合滤波。但是其滤波顺序以及相应的存储更新机制都是针对非流水线结构的,因此如果直接将之应用于本文的流水线设计,就有可能引发严重的竞争与冒险从而降低流水线的性能。

2 去块效应滤波器的存储管理与滤波算法

H.264/AvC标准基于4×4宏块作为滤波的基本宏块,它有5种滤波强度,分别是Bs=0,1,2,3,4。滤波方式分为强滤波、标准滤波和直通3种方式,其中强滤波影响边界两边的共6个像素,标准滤波影响边界两边的共4个像素,直通方式不修改边界两侧的像素。H.264/AVC标准规定先对垂直边界进行滤波,然后再对水平边界进行滤波,只有对垂直与水平边界全部滤波完成后,才可以对下一个宏块进行滤波。同一个宏块中,先对亮度部分进行滤波,再对色度部分进行滤波;色度部分滤波时,先对C6部分进行滤波,再对Cr部分进行滤波,对整个16×16宏块的滤波顺序如图2所示。

|

(1)边界滤波强度与像素滤波的存储器

按照H.264/AVC的标准,需要对被滤波的边界两侧的像素进行有条件的滤波。该条件决定于边界强度BS与像素穿越边界的倾斜度。边界强度BS:0,1,2,3或4,在进行滤波之前被赋给相应的边界。BS=4表示强滤波,BS=0表示不需要进行滤波,即直通方式;否则,BS=1,2,3表示中等强度的滤波,色度部分边界的滤波强度与对应亮度部分是相同的。滤波每条水平或垂直边界需要被提供边界两边的8个像素,p0~p3&q0~q3;需要更新的像素共6个或4个:p0~p2&q0~q2或声p0,p1&q0,q1。

对一个16×16宏块进行滤波需要提供左边相邻像素、右边相邻像素和本宏块的像素。对于宏块边界,比如最左边界与最右边界而言,p0~p3与q0~q3来自不同的模块(即分别来自相邻宏块的像素与本宏块的像素);对于非16×16宏块的边界滤波,像素p0~p3与q0~q3均来自16×16宏块本身,因此至少需要4个存储单元:左相邻像素存储单元、上相邻像素存储单元、本身模块的像素存储单元和转换缓冲单元,每个存储单元的带宽是32位。

当滤波从垂直边界向水平边界变换时,为了方便滤波过程中的存储器访问,这里利用额外的转换缓冲器BUF0~BUF3来缓存中间滤波数据,采用转换缓冲器后获取一行或一列像素的值(即p0~p3&q0~q3)只需要1个时钟周期,否则需要4个时钟周期。

- 新一代视频编码标准H.264/AVC的关键技术研究(09-04)

- Cortex-A8和H.264的无线视频监控系统设计(10-16)

- 解析H.264视频编解码DSP实现与优化(10-26)

- 视频解码器SAA7111在图像采集中的应用(06-21)

- 基于CPLD和VS1011E解码器的电梯语音系统设计(11-26)

- 基于ARM核的音频解码器单芯片系统(01-05)