电容性负载稳定性:噪声增益及 CF

时间:07-21

来源:互联网

点击:

| |

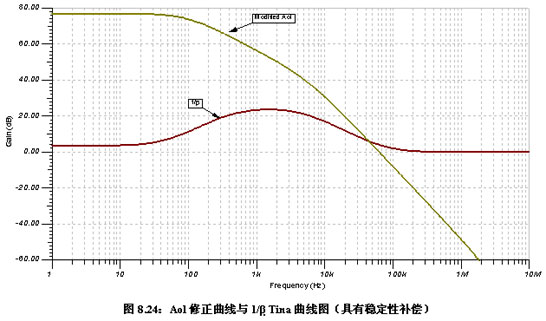

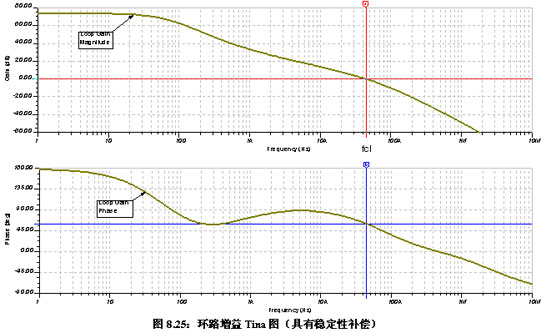

| 图8.25中的环路增益幅度与相位图表明预测环路相位裕度大于45度,对于低于fcl的频率,环路相位永远不会低于45度,这不但能够保证稳定的电路,而且可以确保出色的瞬态响应。 | |

| |

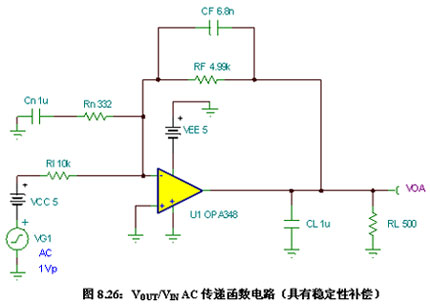

| 为了确认我们的整个闭环带宽、VOUT/VIN、特别是VOA/VG1,我们将采用图8.26所示的电路。 | |

| |

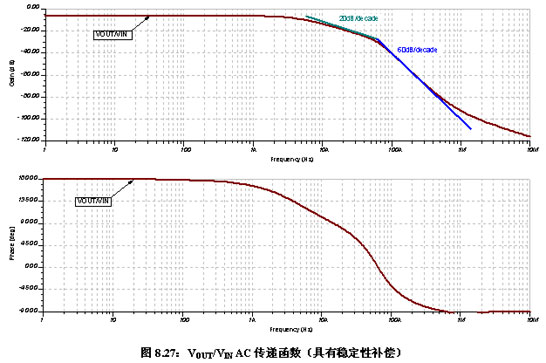

| 图8.27所示的Tina仿真结果表明,我们的闭环AC响应符合一阶预测(参见图8.20)。达到fcl之前在fp处保持-20dB/10倍频程的斜率,达到fcl后fp的下降速率则转变为-60dB/10倍频程,此后将跟随Aol修正曲线一直下降。 | |

| |

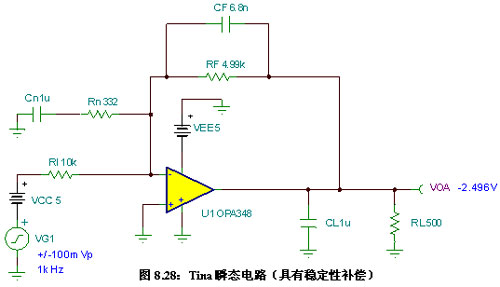

| 另外,采用图8.28所示的TinaSPICE电路,我们看一下补偿电路的瞬态响应。我们期望出现临界阻尼响应。 | |

| |

| 事实上,如图8.29所示,进行了稳定性与相位裕度检查的AC图及瞬态响应之间存在直接关联。我们可以看到可预测且表现良好的瞬态响应,显示出约为60度的相位裕度。 | |

| |

| 非反相噪声增益及CF | |

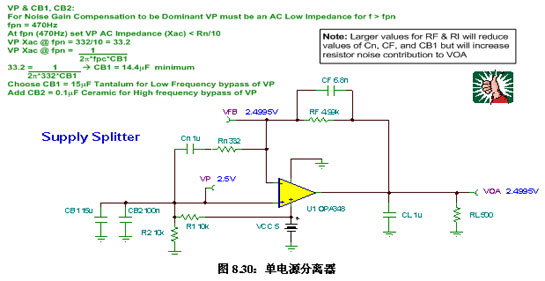

| 对于非反相噪声增益及CF电路而言,我们选择通用的“电源分离器”。这种拓扑常用于单电源系统中,以产生图8.30所示的中值参考电压。由于采用与反相噪声增益及CF电路中相同的运算放大器(OPA348)、RL(500欧姆)以及CL(1uF),因此,我们可以采用与之相同的补偿方法。我们通过研究发现,非反相噪声增益及CF电路中的DC1/β为1或0dB,而不是3.5dB。不过,为了使噪声增益达到预期效果,我们需要确保VP在XCn匹配Rn的频率时或fpn所处位置处于较低阻抗。同样,我们根据10年多来的经验设定VpXac | |

| |

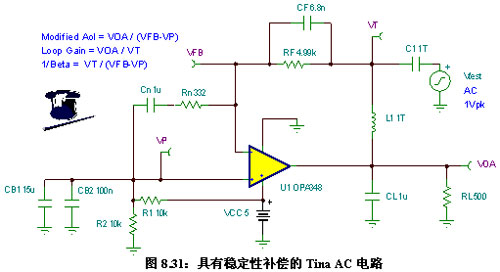

| 图8.31说明了具有稳定性补偿的完整电路。通过此拓扑,我们可以采用Tina SPICEAC分析法检查其稳定性。 | |

| |

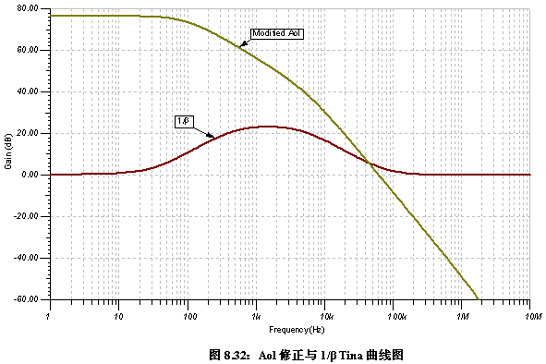

| 图8.32显示了Aol修正与1/β曲线,可以看出该图形与反相噪声增益及CF图大同小异(参见图8.24),这不足为奇。 | |

| |

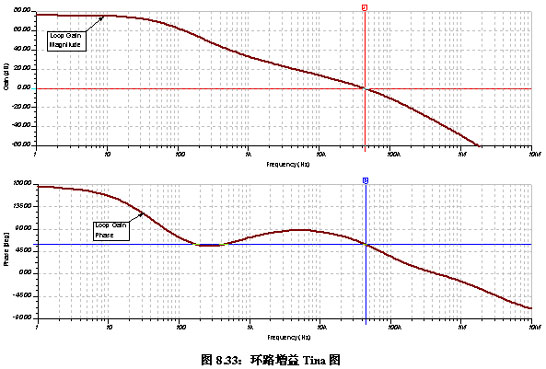

| 图8.33为环路增益幅度与相位图,其同样与反相噪声增益及CF相似(参见图8.25)。 | |

| |

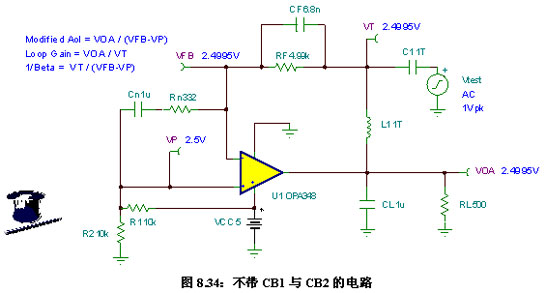

| 我们可以利用图8.34所示电路研究在Cn为短路且噪声增益开始起主导作用的情况下,是哪些因素使VP处于高阻抗。 | |

| |

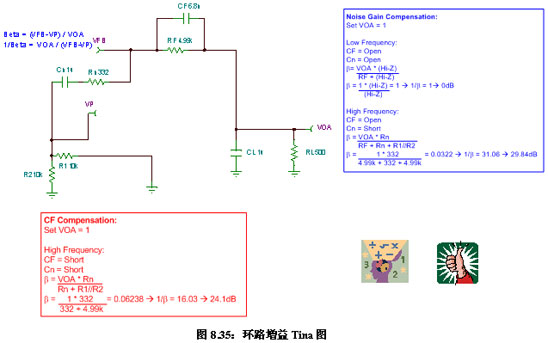

| 如图8.35所示,带与不带CB1与CB2的电路,其1/β计算有所不同。请注意,β是运算放大器输出电压与输入端反馈电压之比。许多情况下运算放大器电路中的反馈电压仅为负输入,而且其比率显而易见。此情况下,我们只要算出运算放大器正/负输入间的差分电压。因此,此时β=(VFB–VP)/VOA,而VOA=1时的1/β为1/(VFB-VP)或者是运算放大器的差分输入电压。由于Cn与Cf都为开路,因此DC1/β=1。在Cn短路,Cf开路情况下,我们可以得到由RF、Rn以及R2//R1组成的电阻分压器。在CF与Cn同时短路情况下,我们仍然可以得到电阻分压器,只不过此时只有Rn与R2//R1组成。 | |

| |

| [table] |

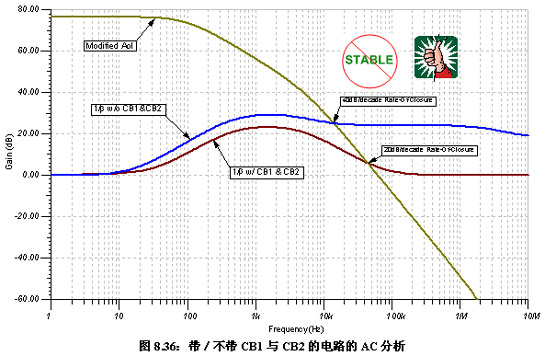

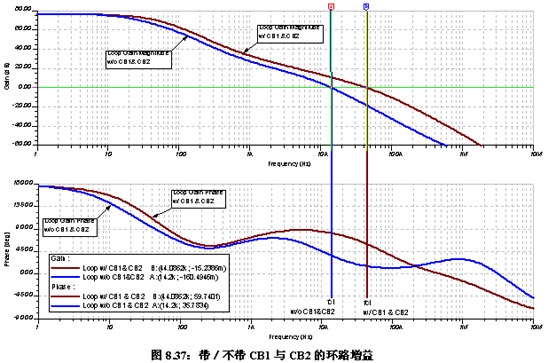

图8.36显示了不带CB1与CB2的电路的分析结果。根据不带CB1与CB2的一阶标准,我们可以得到40dB/10倍频程的闭合速度。而带CB1与CB2我们可以达到预期稳定性。

图8.37说明了带与不带CB1和CB2的环路增益图。带CB1和CB2时的环路增益相位裕度约为60度。而不带CB1和CB2时的环路增益相位裕度则降低到约36度,如图8.37所示。

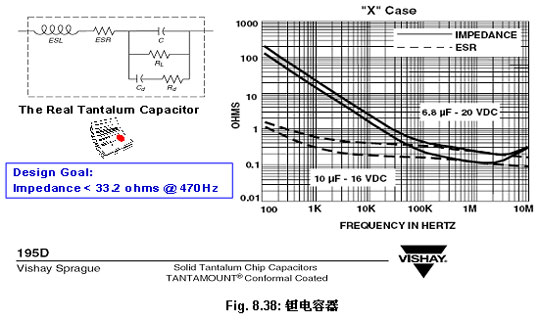

在电容超过1uF时,我们通常采用钽电容,这是因为钽电容器的电容值较大且尺寸相对较小。钽电容并非纯电容,其含有ESR或电阻分量以及较低的寄生电感与电阻。钽电容仅次于电容的最重要分量是ESR。如图8.38所示,我们的非反相噪声增益及CF电路目标是在频率为470Hz时电阻小于33.2欧姆。当10uF曲线在470Hz左右时我们可以看到约30欧姆的阻抗。因此,10uF电容器可以替代15uF电容器,并在我们的电路中运行良好。ESR随所采用的钽电容不同而不同。因此,我们在应用时应当慎重地选择钽电容器。

CMOS 放大器 电容 PIC 仿真 电路 运算放大器 电流 电压 电容器 电感 电阻 MOSFET 滤波器 振荡器 电路图 相关文章:

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)