CPRI协议分析仪的硬件开发与实现

时间:07-20

来源:互联网

点击:

前言

随着通信技术的发展,标准化的基带-射频接口越来越受到各厂家的关注,在近几年内相继出现了CPRI、OBSAI、TDRI接口标准。CPRI作为通用开放接口标准,由于其实现上的经济简便性受到了多方厂家的支持,设备供应商相继推出了基于CRPI协议标准的拉远产品,另一方面基于CRPI协议的交换机和路由器也在逐渐的成熟和推广。开放的通用接口为3G基站产品节约成本、提高通用性和灵活性提供了方便。

CPRI协议由爱立信、华为、NEC、北电和西门子五个厂家联合发起制定,用于无线通讯基站中基带到射频之间的通用接口协议,对其它组织和厂家开放。CPRI大部分内容主要针对WCDMA标准,为其可实现良好服务。经分析,CPRI协议同样适用于TD-SCDMA第三代移动通讯标准。CPRI协议横向分为物理层和数据链路层;纵向分为用户平面、控制管理平面和同步平面,具有图1所示的结构。

硬件构架与实现

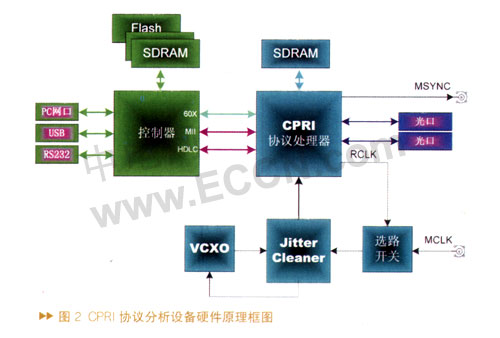

CPRI协议分析仪主要实现射频单元、基带单元的功能模拟。一方面采集数据进行协议分析,另一方面则产生模拟数据进行协议发送。基于图1的协议结构,分析仪由控制器、CPRI协议处理器、时钟处理以及对外接口四个主要功能单元构成,支持614.4Mbps、1.2288Gbps和

2.4576Gbps三种数据速率,原理框图如图2示。

差分信号的端接和匹配

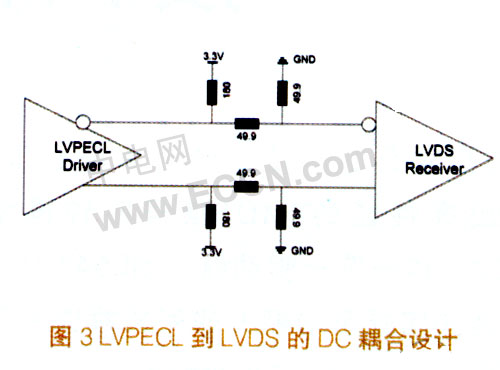

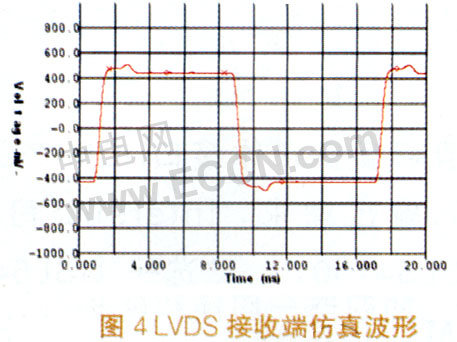

CPRI分析仪板卡上存在LVDS、CML和LVPECL等多种差分电平,不同电平之间的互连需要精心地设计他们之间的匹配和端接,以实现稳定可靠的工作。LVPECL到LVDS之间采用DC耦合,图3和图4显示了61.44MHz时钟在这种设计下的参数和仿真结果。

时序计算分析

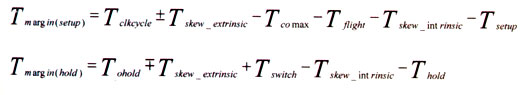

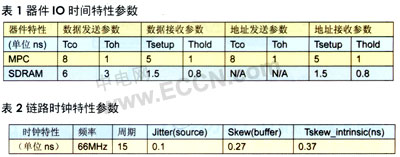

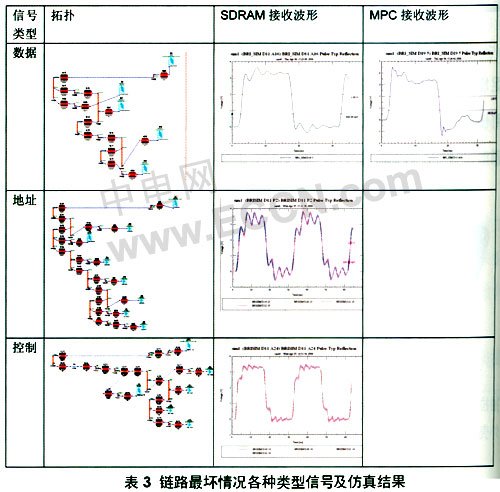

所有的同步时序单沿采样分析建立在如下两个时序闭环公式的基础上:

公式:

公式中各参数的含义及其来源可参考下表:

仿真计算结果显示,SDRAM采样保持时间不足,在实际操作中,将MCP的时钟相位相对 SDRAM时钟的相位滞后0.6ns解决问题。

实际信号测试

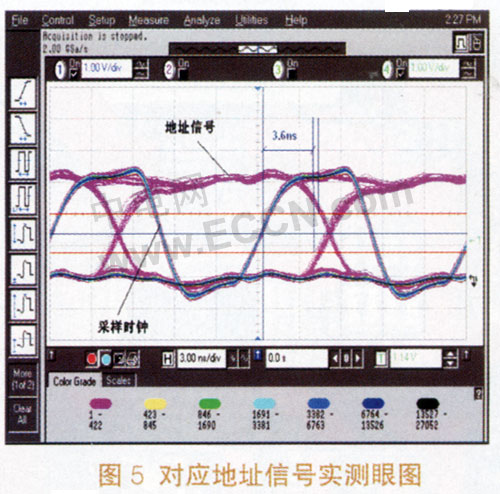

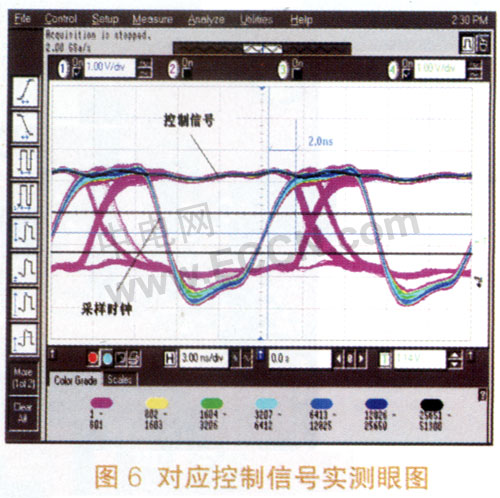

控制信号的实测眼图及其与采样时钟的相位关系见图5、图6。

根据实测数据推算,地址信号和数据信号在SDRAM处的采样时间裕度分别为2.8ns和1.2ns,与仿真计算结果一致。

结论

通过严格的信号仿真和时序裕度计算,实时的调整设计和对板卡的布局布线优化后,板卡性能表现良好,同时也减少了PCB的改版设计次数,节约了研发成本。在GHz级的设计中,PCB的设计非常重要,传输线的特性阻抗控制,过孔的特性阻抗控制,端接匹配的设计对信号的影响不容忽略。对于过孔,由于成本和性能上需要均衡,多层板卡的 无用焊盘引入的电容负载增大,在后续的EDA制图工具中,支持中间层多余焊盘删除的功能是必需的。随着板卡集成度的提高,仿真计算等工作越来越显得必要,凭经验设计的年代逐渐久远,可预知的、可控制性设计需要渗透到每一个细节。

随着通信技术的发展,标准化的基带-射频接口越来越受到各厂家的关注,在近几年内相继出现了CPRI、OBSAI、TDRI接口标准。CPRI作为通用开放接口标准,由于其实现上的经济简便性受到了多方厂家的支持,设备供应商相继推出了基于CRPI协议标准的拉远产品,另一方面基于CRPI协议的交换机和路由器也在逐渐的成熟和推广。开放的通用接口为3G基站产品节约成本、提高通用性和灵活性提供了方便。

CPRI协议由爱立信、华为、NEC、北电和西门子五个厂家联合发起制定,用于无线通讯基站中基带到射频之间的通用接口协议,对其它组织和厂家开放。CPRI大部分内容主要针对WCDMA标准,为其可实现良好服务。经分析,CPRI协议同样适用于TD-SCDMA第三代移动通讯标准。CPRI协议横向分为物理层和数据链路层;纵向分为用户平面、控制管理平面和同步平面,具有图1所示的结构。

硬件构架与实现

CPRI协议分析仪主要实现射频单元、基带单元的功能模拟。一方面采集数据进行协议分析,另一方面则产生模拟数据进行协议发送。基于图1的协议结构,分析仪由控制器、CPRI协议处理器、时钟处理以及对外接口四个主要功能单元构成,支持614.4Mbps、1.2288Gbps和

2.4576Gbps三种数据速率,原理框图如图2示。

差分信号的端接和匹配

CPRI分析仪板卡上存在LVDS、CML和LVPECL等多种差分电平,不同电平之间的互连需要精心地设计他们之间的匹配和端接,以实现稳定可靠的工作。LVPECL到LVDS之间采用DC耦合,图3和图4显示了61.44MHz时钟在这种设计下的参数和仿真结果。

时序计算分析

所有的同步时序单沿采样分析建立在如下两个时序闭环公式的基础上:

公式:

公式中各参数的含义及其来源可参考下表:

仿真计算结果显示,SDRAM采样保持时间不足,在实际操作中,将MCP的时钟相位相对 SDRAM时钟的相位滞后0.6ns解决问题。

实际信号测试

控制信号的实测眼图及其与采样时钟的相位关系见图5、图6。

根据实测数据推算,地址信号和数据信号在SDRAM处的采样时间裕度分别为2.8ns和1.2ns,与仿真计算结果一致。

结论

通过严格的信号仿真和时序裕度计算,实时的调整设计和对板卡的布局布线优化后,板卡性能表现良好,同时也减少了PCB的改版设计次数,节约了研发成本。在GHz级的设计中,PCB的设计非常重要,传输线的特性阻抗控制,过孔的特性阻抗控制,端接匹配的设计对信号的影响不容忽略。对于过孔,由于成本和性能上需要均衡,多层板卡的 无用焊盘引入的电容负载增大,在后续的EDA制图工具中,支持中间层多余焊盘删除的功能是必需的。随着板卡集成度的提高,仿真计算等工作越来越显得必要,凭经验设计的年代逐渐久远,可预知的、可控制性设计需要渗透到每一个细节。

射频 总线 Cadence 仿真 PCB 电容 EDA 相关文章:

- D类MOSFT在发射机射频功放中的应用(11-18)

- 单片射频收发芯片A7105的原理与应用(10-12)

- LDO电源管理模块的分析及其在数字模拟射频系统中的应用(01-26)

- 如何完善您的射频采样解决方案?(11-26)

- 核磁共振系统中射频开关设计(01-04)

- 基于MATLAB仪器控制工具箱的SAW标签阅读器系统设计(06-24)