AD7674与TMS320F2812 McBSP之间的串口通信

时间:07-19

来源:互联网

点击:

1 引言

随着数字信号处理技术的发展,人们对嵌入式数据采集系统的采样精度和传输速度要求越来越高,本文介绍的嵌入式数据采集系统设计方案采用了ADI公司的高精度18位SAR型ADC AD7674与TI公司32位定点主频高达150 MHz的DSPTMS320F2812构成一个数据采集系统,并利用McBSP的时钟停止模式实现与AD7674之间的高速数据传输。

2 AD7674简介

AD7674是一款高精度18位逐次逼近(SAR)型ADC,它具有采样速率高、精度高、功耗低、无管道延迟的特点,其采样速率最高可以达到800 kS/s(每秒千次采样),积分非线性误差(INL)最大为±2.5 LSB,在整个工作温度范围内,保证无丢码。该器件是全差分输入,5 V单电源供电,可接5 V或3.3 V数字电源。AD7674还具有许多其它特点,包括一个内部变换时钟、一个内部基准缓冲器、误差修正电路以及串行(SPI)与并口(18、16或8位总线)接口。

AD7674能提供3种不同转换速率工作方式以便对不同的具体应用优化性能,这三种工作模式如下:

WARP:允许采样率高达800 kS/s。然而在这种模式下只有转化之间的时间不超过1ms时,才能保证其转化的精度,如果连续两次转换之间的时间大于1 m8,第一次转换的结果就会被忽略,这种模式适合于要求快速采样率的应用。

NORMAL:这种模式的采样率为666 kS/s,在这种模式下对采样转化之间的时间没有限制,这样既可保证高的转换精度又可确保快速的采样速率。

IMPULSE:这是一种低功耗模式,其采样率为570 kS/s,例如:当器件工作在1 kS/s时,仅消耗功率为136 μW,该器件适合于电池供电的应用。

3 多通道缓冲串行接口(McBSP)

TMS320F2812是一款高性能、多功能、高性价比32位定点DSP。该器件兼容于TMS320F2407指令系统,最高可在150 MHz主频下工作,片上集成有丰富的外设,其中包括一个多通道缓冲串行接口(McBSP)。

TMS320F2812的McBSP在时钟停止模式下工作时与串行外围接口(SPI)相兼容,这便于与SPI器件连接。

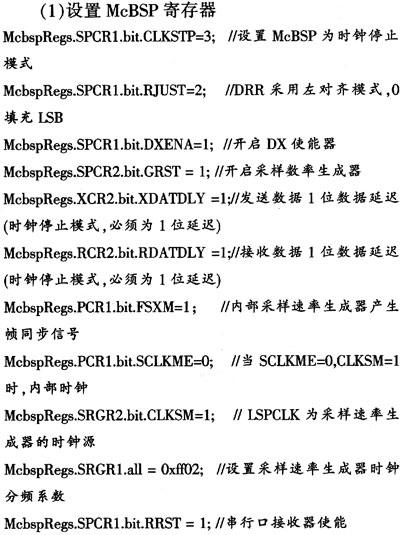

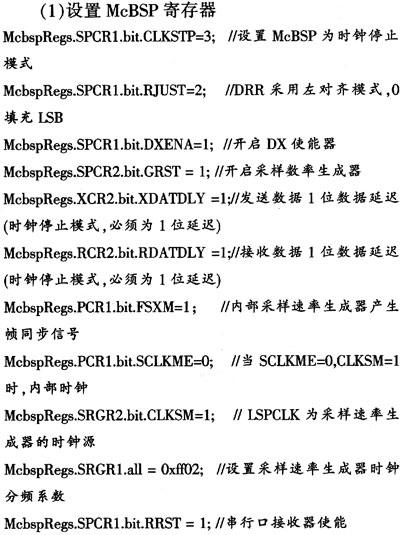

当McBSP配置为时钟停止模式时,发送器和接收器内部同步,这样McBSP可以作为一个SPI主设备或从设备。在此模式下,McBSP的发送时钟信号CLKX相当于SPI总线的SCLK信号,输出信号DX作为SPI主设备的MOSI信号,接收输入信号DR作为SPI主设备的MISO信号。将McBSP配置为SPI主设备时,需要配置相应的寄存器,在时钟停止模式中,由于采用内部同步模式,因此不使用时钟信号CLKR和接收帧同步信号FSK。为使DSP按照一定的方式通信,需要对McBSP的各个控制寄存器进行相应配置,其中,SPCR1/SPCR2用于设置工作模式、接收符号扩展和对齐模式、对收发器和采样速率生成器进行复位,以及判断收发器是否准备好等。RCR1/RCR2用于控制接收数据的字长、数据延迟。XCR1/XCR2用于控制发送数据的字长、数据延迟。SRGR1/SRGR2用于设置采样速率生成器的工作模式和采样速率生成器的分频系数。PCR用于控制相应引脚的工作模式。

4 McBSP接口电路设计

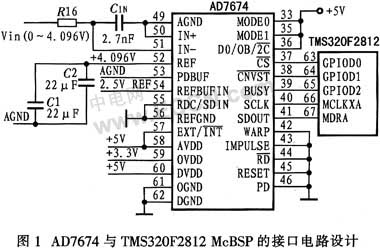

AD7674与TMS320F2812的接口电路如图1所示。在本系统设计中,为了保证较高的转换精度和快速的采样速率,需采取以下措施:(1)AD7674设置成NORMAL工作方式,即WARP和IMPULSE引脚接地;(2)采用串口通信方式,将MODE0和MODE1固定为高电平;(3)将EXT/INT引脚接高电平,配置为从设备;(4)AD7674的CS、CNVST、BUSY引脚分别与TMS320F2812的GPIOD0、GPIOD1、GPIOD2引脚相连,通过TMS320F2812的GPIO端口控制AD7674的片选、转换及工作状态;(5)AD7674符合SPI的数据通信协议,将其SCLK引脚与TMS320F2812的MCLKXA引脚相连,这样TMS320F2812可向AD7674提供接收数据的时钟;(6)AD7674的SDOUT引脚与TMS320F2812的MDRA引脚相连。接收数据时,使SDOUT输出的采样结果在时钟脉冲的控制下通过MDRA逐位移至McBSP的接收移位寄存器。

5 软件设计

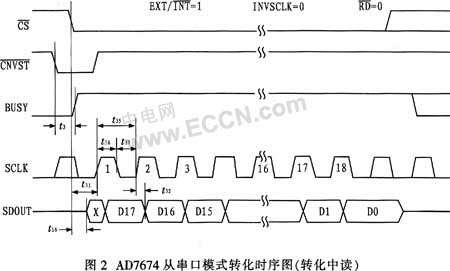

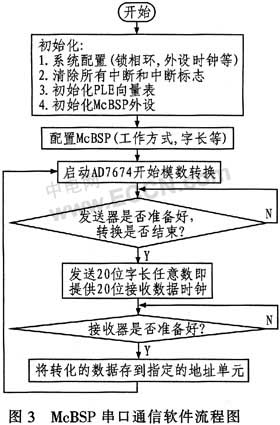

AD7674与TMS320F2812McBSP进行高速串行通信时,首先通过TMS320F2812 McBSP的相关寄存器设置,配置McBSP为时钟停止模式,该模式兼容于SPI协议,再配置McBSP的字长、对齐模式、数据延迟、采样速率生成器的分频系数,然后通过TMS320F2812的GPIOD0端口片选AD7674,并启动ADC的转换。当转换控制输入CNVST的下降沿到来时,片内采样保持器由采样模式转化为保持模式,保持模拟输入信号,并启动转换过程,转换启动后,BUSY信号一直保持高电平,直到转换完成,BUSY信号才变为低电平。最后在TMS320F2812输出脉冲的控制下,将18位的采集结果送至指定的存储单元。AD7674从串口模式转换时序图如图2所示。McB-SP串口通信软件流程图如图3所示。部分程序如下:

AD7674的输入模拟量Vin=3.07 V时,串口通信记录如图4所示。图中通道Chl为MeBSP的输出时钟MCLKXA(20位时钟脉冲),通道Ch2为AD7674的SDOUT引脚输出的18位结果。

为了满足AD7674的A/D转换的所有时序要求,提供给A7674 SPI接口的时钟不大于17 Mbit/s,因而在试验中,通过设置McBSP采样速率生成器时钟的分频系数,从而使得McBSP的输出时钟频率为12.52 MHz,以达到满足A/D转换的时序要求。

随着数字信号处理技术的发展,人们对嵌入式数据采集系统的采样精度和传输速度要求越来越高,本文介绍的嵌入式数据采集系统设计方案采用了ADI公司的高精度18位SAR型ADC AD7674与TI公司32位定点主频高达150 MHz的DSPTMS320F2812构成一个数据采集系统,并利用McBSP的时钟停止模式实现与AD7674之间的高速数据传输。

2 AD7674简介

AD7674是一款高精度18位逐次逼近(SAR)型ADC,它具有采样速率高、精度高、功耗低、无管道延迟的特点,其采样速率最高可以达到800 kS/s(每秒千次采样),积分非线性误差(INL)最大为±2.5 LSB,在整个工作温度范围内,保证无丢码。该器件是全差分输入,5 V单电源供电,可接5 V或3.3 V数字电源。AD7674还具有许多其它特点,包括一个内部变换时钟、一个内部基准缓冲器、误差修正电路以及串行(SPI)与并口(18、16或8位总线)接口。

AD7674能提供3种不同转换速率工作方式以便对不同的具体应用优化性能,这三种工作模式如下:

WARP:允许采样率高达800 kS/s。然而在这种模式下只有转化之间的时间不超过1ms时,才能保证其转化的精度,如果连续两次转换之间的时间大于1 m8,第一次转换的结果就会被忽略,这种模式适合于要求快速采样率的应用。

NORMAL:这种模式的采样率为666 kS/s,在这种模式下对采样转化之间的时间没有限制,这样既可保证高的转换精度又可确保快速的采样速率。

IMPULSE:这是一种低功耗模式,其采样率为570 kS/s,例如:当器件工作在1 kS/s时,仅消耗功率为136 μW,该器件适合于电池供电的应用。

3 多通道缓冲串行接口(McBSP)

TMS320F2812是一款高性能、多功能、高性价比32位定点DSP。该器件兼容于TMS320F2407指令系统,最高可在150 MHz主频下工作,片上集成有丰富的外设,其中包括一个多通道缓冲串行接口(McBSP)。

TMS320F2812的McBSP在时钟停止模式下工作时与串行外围接口(SPI)相兼容,这便于与SPI器件连接。

当McBSP配置为时钟停止模式时,发送器和接收器内部同步,这样McBSP可以作为一个SPI主设备或从设备。在此模式下,McBSP的发送时钟信号CLKX相当于SPI总线的SCLK信号,输出信号DX作为SPI主设备的MOSI信号,接收输入信号DR作为SPI主设备的MISO信号。将McBSP配置为SPI主设备时,需要配置相应的寄存器,在时钟停止模式中,由于采用内部同步模式,因此不使用时钟信号CLKR和接收帧同步信号FSK。为使DSP按照一定的方式通信,需要对McBSP的各个控制寄存器进行相应配置,其中,SPCR1/SPCR2用于设置工作模式、接收符号扩展和对齐模式、对收发器和采样速率生成器进行复位,以及判断收发器是否准备好等。RCR1/RCR2用于控制接收数据的字长、数据延迟。XCR1/XCR2用于控制发送数据的字长、数据延迟。SRGR1/SRGR2用于设置采样速率生成器的工作模式和采样速率生成器的分频系数。PCR用于控制相应引脚的工作模式。

4 McBSP接口电路设计

AD7674与TMS320F2812的接口电路如图1所示。在本系统设计中,为了保证较高的转换精度和快速的采样速率,需采取以下措施:(1)AD7674设置成NORMAL工作方式,即WARP和IMPULSE引脚接地;(2)采用串口通信方式,将MODE0和MODE1固定为高电平;(3)将EXT/INT引脚接高电平,配置为从设备;(4)AD7674的CS、CNVST、BUSY引脚分别与TMS320F2812的GPIOD0、GPIOD1、GPIOD2引脚相连,通过TMS320F2812的GPIO端口控制AD7674的片选、转换及工作状态;(5)AD7674符合SPI的数据通信协议,将其SCLK引脚与TMS320F2812的MCLKXA引脚相连,这样TMS320F2812可向AD7674提供接收数据的时钟;(6)AD7674的SDOUT引脚与TMS320F2812的MDRA引脚相连。接收数据时,使SDOUT输出的采样结果在时钟脉冲的控制下通过MDRA逐位移至McBSP的接收移位寄存器。

5 软件设计

AD7674与TMS320F2812McBSP进行高速串行通信时,首先通过TMS320F2812 McBSP的相关寄存器设置,配置McBSP为时钟停止模式,该模式兼容于SPI协议,再配置McBSP的字长、对齐模式、数据延迟、采样速率生成器的分频系数,然后通过TMS320F2812的GPIOD0端口片选AD7674,并启动ADC的转换。当转换控制输入CNVST的下降沿到来时,片内采样保持器由采样模式转化为保持模式,保持模拟输入信号,并启动转换过程,转换启动后,BUSY信号一直保持高电平,直到转换完成,BUSY信号才变为低电平。最后在TMS320F2812输出脉冲的控制下,将18位的采集结果送至指定的存储单元。AD7674从串口模式转换时序图如图2所示。McB-SP串口通信软件流程图如图3所示。部分程序如下:

AD7674的输入模拟量Vin=3.07 V时,串口通信记录如图4所示。图中通道Chl为MeBSP的输出时钟MCLKXA(20位时钟脉冲),通道Ch2为AD7674的SDOUT引脚输出的18位结果。

为了满足AD7674的A/D转换的所有时序要求,提供给A7674 SPI接口的时钟不大于17 Mbit/s,因而在试验中,通过设置McBSP采样速率生成器时钟的分频系数,从而使得McBSP的输出时钟频率为12.52 MHz,以达到满足A/D转换的时序要求。

嵌入式 ADI ADC DSP 电路 总线 收发器 C语言 相关文章:

- 单片机嵌入式系统在运程电网监测系统中的应用(05-13)

- 嵌入式测试为串行I/O提供真正的价值(05-26)

- 今天的绿色 POL DC/DC 转换器设计需要高效率和低 IQ(07-11)

- flash接口电路的实现(07-18)

- RS485串行总线可靠性的研究(03-24)

- 一种支持ISP的Flash在嵌入式设计中的应用(08-19)