基于Virtuoso平台的单片射频收发系统电路仿真与版图设计

时间:07-18

来源:互联网

点击:

温度分析

要保证最终系统设计的可靠性和成品率,很关键的一步是在各个单元块的设计中进行温度、极端情况等分析。这些功能可以在cadenceVirtuoso中通过设置不同的仿真温度、通过仿真模型的Corner设置,以及直接使用其提供的MonteCarlo仿真工具来进行。

射频收发系统的整体电路仿真

各个模块电路分别设计验证完成以后,就可以把所有模块连成系统,并加上PAD、ESD等构成一个完整的芯片系统,如图4所示。对这个系统加上激励进行仿真测试,如图5所示,可以对整个系统电路进行仿真。如果仿真计算所用的硬件资源足够大,可以直接对系统进行tran、SP、PSS,以及PSP、Pnoise、PAC等分析,获得整个芯片的性能。如果资源不足,则可以考虑对系统按功能进行分组、分块仿真。由于分出的块之间相对独立,因此整体系统的特性与分块仿真差别不大。

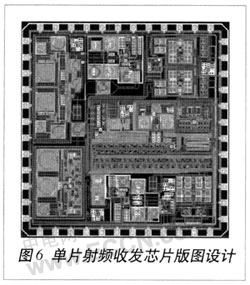

版图设计与后仿真

在各模块的设计指标满足自身及系统要求的基础上可以开始各个模块的版图设计,如图6所示。首先利用Layout-XL的元件调入功能可以直接由原理图调入版图元件,进行各个模块的粗略布局,主要是安排与其它模块的连接端口以及一些重要元件的预布局。然后从系统上将所有模块的预布局调入进行整体布局考虑。利用Virtuoso Layout工具所具有的层次化管理和操作的特性,可以对每个模块的安放及其与其它模块的衔接进行系统考虑。

系统布局以后,将边界条件分配给每个模块。在模块单独的布局过程中要遵守其边界约定。版图进行到一定阶段后,即可以调入到系统版图中来检查,随时作必要的调整以满足每个模块的具体情况。

具体版图绘制过程中可以充分利用Virtuoso版图工具的强大功能,比如充分发挥快捷键功能可以使版图设计流畅高效;利用Layout-XL的交叉参考可以随时发现错误的连线或因疏忽造成的短路;利用DRD的实时规则检查可以避免绝大多数违反设计规则的布图。

版图的规则检查可以采用Virtuoso的Diva工具,DRC、LVS、Extract等工作都可以在其友好的界面下完成。对于射频电路版图元件数规模不大的特点,利用Diva完成绝大部分工作是很合适的。如果想进一步提高版图提取和后仿真的精确度,可以考虑采用Assura工具来进行。

结语

本文详细讨论了基于cadenceVirtuoso设计平台的单片射频收发集成电路的设计过程。讨论了利用VirtUOSO工具完成的自顶向下、从系统到模块、从前端都后端的整个设计步骤,直到实现一个完整的射频芯片。可以看出,Virtuoso平台工具在IC设计的各个阶段所发挥的重要作用。

文中所述的单片射频芯片设计中所采用的Virtuoso工具只是VirtUOS()家族中最常用的几个工具,依靠他们的强大功能足以完成复杂的射频系统设计,是性价比较高的一种解决方案。如果再结合Virtuoso的AMS、Ultrasim、VoltageStorm、ElectronStorm等工具,将会使设计效率更高,设计更精确

要保证最终系统设计的可靠性和成品率,很关键的一步是在各个单元块的设计中进行温度、极端情况等分析。这些功能可以在cadenceVirtuoso中通过设置不同的仿真温度、通过仿真模型的Corner设置,以及直接使用其提供的MonteCarlo仿真工具来进行。

射频收发系统的整体电路仿真

各个模块电路分别设计验证完成以后,就可以把所有模块连成系统,并加上PAD、ESD等构成一个完整的芯片系统,如图4所示。对这个系统加上激励进行仿真测试,如图5所示,可以对整个系统电路进行仿真。如果仿真计算所用的硬件资源足够大,可以直接对系统进行tran、SP、PSS,以及PSP、Pnoise、PAC等分析,获得整个芯片的性能。如果资源不足,则可以考虑对系统按功能进行分组、分块仿真。由于分出的块之间相对独立,因此整体系统的特性与分块仿真差别不大。

版图设计与后仿真

在各模块的设计指标满足自身及系统要求的基础上可以开始各个模块的版图设计,如图6所示。首先利用Layout-XL的元件调入功能可以直接由原理图调入版图元件,进行各个模块的粗略布局,主要是安排与其它模块的连接端口以及一些重要元件的预布局。然后从系统上将所有模块的预布局调入进行整体布局考虑。利用Virtuoso Layout工具所具有的层次化管理和操作的特性,可以对每个模块的安放及其与其它模块的衔接进行系统考虑。

系统布局以后,将边界条件分配给每个模块。在模块单独的布局过程中要遵守其边界约定。版图进行到一定阶段后,即可以调入到系统版图中来检查,随时作必要的调整以满足每个模块的具体情况。

具体版图绘制过程中可以充分利用Virtuoso版图工具的强大功能,比如充分发挥快捷键功能可以使版图设计流畅高效;利用Layout-XL的交叉参考可以随时发现错误的连线或因疏忽造成的短路;利用DRD的实时规则检查可以避免绝大多数违反设计规则的布图。

版图的规则检查可以采用Virtuoso的Diva工具,DRC、LVS、Extract等工作都可以在其友好的界面下完成。对于射频电路版图元件数规模不大的特点,利用Diva完成绝大部分工作是很合适的。如果想进一步提高版图提取和后仿真的精确度,可以考虑采用Assura工具来进行。

结语

本文详细讨论了基于cadenceVirtuoso设计平台的单片射频收发集成电路的设计过程。讨论了利用VirtUOSO工具完成的自顶向下、从系统到模块、从前端都后端的整个设计步骤,直到实现一个完整的射频芯片。可以看出,Virtuoso平台工具在IC设计的各个阶段所发挥的重要作用。

文中所述的单片射频芯片设计中所采用的Virtuoso工具只是VirtUOS()家族中最常用的几个工具,依靠他们的强大功能足以完成复杂的射频系统设计,是性价比较高的一种解决方案。如果再结合Virtuoso的AMS、Ultrasim、VoltageStorm、ElectronStorm等工具,将会使设计效率更高,设计更精确

射频 放大器 滤波器 电路 电流 Cadence 仿真 安捷伦 Mathworks Verilog VHDL 集成电路 相关文章:

- D类MOSFT在发射机射频功放中的应用(11-18)

- 单片射频收发芯片A7105的原理与应用(10-12)

- LDO电源管理模块的分析及其在数字模拟射频系统中的应用(01-26)

- 如何完善您的射频采样解决方案?(11-26)

- 核磁共振系统中射频开关设计(01-04)

- 基于MATLAB仪器控制工具箱的SAW标签阅读器系统设计(06-24)