如何调试锁相环频率合成器

时间:06-25

来源:互联网

点击:

引言

无线电系统会因为各种各样的原因而采用基于锁相环(PLL)技术的频率合成器。PLL的好处包括:

(1)易于集成到IC中。

(2)无线信道间隔中的灵活性。

(3)可获得高性能。

(4)频率合成器外形尺寸较小。

本文向读者介绍PLL应用中颇具价值的注意事项和使用技巧。

PLL概述

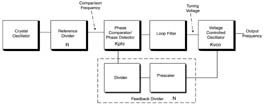

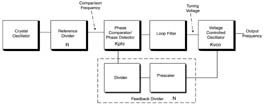

简单的PLL由频率基准、相位检波器、电荷泵、环路滤波器和压控振荡器(VCO)组成。基于PLL技术的频率合成器将增加两个分频器:一个用于降低基准频率,另一个则用于对VCO进行分频。而且,将相位检波器和电荷泵组合在一个功能块中也很容易,以便进行分析(见图1)。简单的PLL上所增设的这些数字分频器电路实现了工作频率的轻松调节。处理器将简单地把一个新的分频值“写入”到位于PLL中的寄存器中,更新VCO的工作频率,并由此改变无线设备的工作信道。

PLL工作原理

PLL是作为闭环控制系统工作,用于比较基准信号与VCO的相位。增设基准和反馈分频器的频率合成器负责比较两个由分频器的设定值调节相位。该相位比较在相位检波器中完成,在大多数系统中,这种相位检波器是一个相位和频率检波器。该相位-频率检波器生成一个误差电压,此误差电压在±2π的相位误差范围内近似为线性,并在误差大于±2π的情况下保持恒定。相位-频率比较器所采用的这种双模式操作可生成针对大频率误差(比如,当PLL在上电期间起动时)的较快的PLL锁定时间,并避免被锁定于谐波之上。

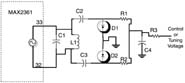

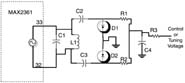

VCO利用调谐电压生成一个频率。VCO可以是模块、IC,也可由分立元件来制成。图2示出了一个位于MAX2361发送器IC内部的、采用有源元件制作的VCO。谐振回路和变容二极管是外置的,使得设计工程师能够对IF(中频)LO(本机振荡器)进行独特的规定,以便对特定的无线电频率方案提供支持。

环路滤波器对由相位-频率检波器的电荷泵所产生的电流脉冲进行积分,以生成施加于VCO的调谐电压。传统的做法是使来自环路滤波器的调谐电压升高(变为更大的正值),以使VCO的相位超前并提高VCO的频率。环路滤波器可以采用诸如电阻器和电容器等无源元件来实现,也可采用一个运算放大器。环路滤波器的时间常数以及VCO、相位检波器和分频器的增益将设定PLL带宽。PLL带宽决定了瞬态响应、基准寄生电平和噪声滤波特性。在PLL带宽之内,频率合成器输出端上的相位噪声主要是相位检波器相位噪声;而在PLL带宽之外,输出相位噪声则主要源自VCO相位噪声。

频率合成器PLL基准输入是一个稳定、无干扰的恒定频率信号。在大多数无线电设备中都采用了某种形式的晶体振荡器,原因是其相位噪声非常低,而且其频率稳定并进行了精确的规定。PLL将对该基准进行分频,以提供一个用于相位-频率检波器的较低频率。这一较低的频率将设定用于检波器的比较率,并通过使反馈分频器设定值以“1”的幅度递增的方法来设立可行的最小频率步进。这变成了合成器的频率分辨率(即频率步长),它应该等于或小于正在设计之中的无线电系统的信道间隔。利用由反馈分频器按比例缩小的VCO的输出,相位检波器和环路滤波器生成了一个调谐电压。基于上述说明,VCO的工作频率为:

例如,若基准频率为20MHz,且基准分频器值为2000,则一个88103的反馈分频器设定值将产生一个如下的VCO频率:

20MHz/2000)×88103=881.03 MHz

由于比较频率为10kHz,因此,使反馈分频器设定值增加1(即变为88104)将产生一个数值为881.04MHz的VCO频率。

该频率合成器将基准频率倍频至UHF波段。采用这种PLL倍频法会引发一个不良的后果,即环路带宽内的相位噪声有所增加。在环路带宽内,PLL噪声层的增幅为20log(N)。在上文所述的场合中,相位噪声将增加20log(88103) = 98.89dB!这就是基准振荡器必须非常干净的原因。环路的动作将使噪声层增加100dB左右,所以,如果想获得满足当今无线电通信需要的足够输出质量,就必须采用高Q值晶体振荡器。

使PLL正常运作

VCO部分

因为VCO由PLL频率合成器来生成信号输出,所以PLL的绝大部分性能都是由它决定的。如果VCO未能正确地运作,则许多性能参数都将受到影响。在调试阶段的初期应对VCO进行测试,以确保其提供预定的频率范围、增益和输出电平。如果只是想测试VCO,则需对PLL进行修正,以取消闭环控制。“断开”环路的一种常用方法是使R3开路(见图2),并在C4的两端施加一个实验室电源,这样就使得VCO调谐电压能够在期望的范围内改变。当调谐电压改变时,应在一个频率计数器(或频谱分析仪)上监视VCO的工作频率。记录若干调谐电压设定值条件下的VCO工作频率。

VCO是否位于正确的频率上?

利用由上述的简单测试所获得的数据,您将可以对VCO能否工作于期望的频率之上做出快速评估。如果VCO产生一个位于183MHz频率之上IF LO(中频本机振荡器),而测试中所记录的最低频率为187MHz,则PLL将无法进行正确的相位锁定。为了对该条件进行校正,应核实VCO振荡回路中的所有谐振元件均具有所需的参数值。例如,若谐振电路电感器L1(见图2)过小,则谐振频率将被提升。

---应始终牢记用于描述一个简单的LC谐振电路的谐振频率的方程式:

Fres为谐振频率(单位:Hz)。

---L为电感值(单位:H)。

--- C为电容值(单位:F)。

---● 是否安装了正确的元器件?

---电抗元件的尺寸非常之小,以致于无法印上可见标签。这就意味着VCO当中的元件的最为容易的测试方法是采用已知数值的元件来进行替换。由于第一块电路板的组装可能是手工完成的,因此很有可能在PCB上焊接了参数值不正确的元件。可根据需要来替换振荡回路中的元件,以使VCO频率接近期望的工作点。

---您可以按照表1所述对VCO进行校正,但PLL仍然有可能出现问题。如果VCO的调谐增益与计算环路滤波元件参数值时所采用的数值相差较大,则环路有可能发生振荡。在图3中,应注意的是由原型设计所获得的实验室数据绘制的曲线的斜率。反馈环路稳定性的获得要求环路增益位于特定的范围内。如果VCO处于正确的频率之上但增益误差较大,则环路本身将发生振荡并导致VCO在众多的频率上被调制。在开环条件下使用您的VCO数据,以验证环路增益接近您的设计目标值。如果VCO的调谐增益过高,则变容二极管将被过于紧密地耦合至谐振电路。应确认安装了正确的变容二极管。将变容二极管耦合至振荡回路的电容器(图2中的C2和C3)可能数值过大。反过来,如果VCO调谐增益较低,则或许需要增大C2和C3的数值。

无线电系统会因为各种各样的原因而采用基于锁相环(PLL)技术的频率合成器。PLL的好处包括:

(1)易于集成到IC中。

(2)无线信道间隔中的灵活性。

(3)可获得高性能。

(4)频率合成器外形尺寸较小。

本文向读者介绍PLL应用中颇具价值的注意事项和使用技巧。

PLL概述

简单的PLL由频率基准、相位检波器、电荷泵、环路滤波器和压控振荡器(VCO)组成。基于PLL技术的频率合成器将增加两个分频器:一个用于降低基准频率,另一个则用于对VCO进行分频。而且,将相位检波器和电荷泵组合在一个功能块中也很容易,以便进行分析(见图1)。简单的PLL上所增设的这些数字分频器电路实现了工作频率的轻松调节。处理器将简单地把一个新的分频值“写入”到位于PLL中的寄存器中,更新VCO的工作频率,并由此改变无线设备的工作信道。

PLL工作原理

PLL是作为闭环控制系统工作,用于比较基准信号与VCO的相位。增设基准和反馈分频器的频率合成器负责比较两个由分频器的设定值调节相位。该相位比较在相位检波器中完成,在大多数系统中,这种相位检波器是一个相位和频率检波器。该相位-频率检波器生成一个误差电压,此误差电压在±2π的相位误差范围内近似为线性,并在误差大于±2π的情况下保持恒定。相位-频率比较器所采用的这种双模式操作可生成针对大频率误差(比如,当PLL在上电期间起动时)的较快的PLL锁定时间,并避免被锁定于谐波之上。

VCO利用调谐电压生成一个频率。VCO可以是模块、IC,也可由分立元件来制成。图2示出了一个位于MAX2361发送器IC内部的、采用有源元件制作的VCO。谐振回路和变容二极管是外置的,使得设计工程师能够对IF(中频)LO(本机振荡器)进行独特的规定,以便对特定的无线电频率方案提供支持。

环路滤波器对由相位-频率检波器的电荷泵所产生的电流脉冲进行积分,以生成施加于VCO的调谐电压。传统的做法是使来自环路滤波器的调谐电压升高(变为更大的正值),以使VCO的相位超前并提高VCO的频率。环路滤波器可以采用诸如电阻器和电容器等无源元件来实现,也可采用一个运算放大器。环路滤波器的时间常数以及VCO、相位检波器和分频器的增益将设定PLL带宽。PLL带宽决定了瞬态响应、基准寄生电平和噪声滤波特性。在PLL带宽之内,频率合成器输出端上的相位噪声主要是相位检波器相位噪声;而在PLL带宽之外,输出相位噪声则主要源自VCO相位噪声。

频率合成器PLL基准输入是一个稳定、无干扰的恒定频率信号。在大多数无线电设备中都采用了某种形式的晶体振荡器,原因是其相位噪声非常低,而且其频率稳定并进行了精确的规定。PLL将对该基准进行分频,以提供一个用于相位-频率检波器的较低频率。这一较低的频率将设定用于检波器的比较率,并通过使反馈分频器设定值以“1”的幅度递增的方法来设立可行的最小频率步进。这变成了合成器的频率分辨率(即频率步长),它应该等于或小于正在设计之中的无线电系统的信道间隔。利用由反馈分频器按比例缩小的VCO的输出,相位检波器和环路滤波器生成了一个调谐电压。基于上述说明,VCO的工作频率为:

例如,若基准频率为20MHz,且基准分频器值为2000,则一个88103的反馈分频器设定值将产生一个如下的VCO频率:

20MHz/2000)×88103=881.03 MHz

由于比较频率为10kHz,因此,使反馈分频器设定值增加1(即变为88104)将产生一个数值为881.04MHz的VCO频率。

该频率合成器将基准频率倍频至UHF波段。采用这种PLL倍频法会引发一个不良的后果,即环路带宽内的相位噪声有所增加。在环路带宽内,PLL噪声层的增幅为20log(N)。在上文所述的场合中,相位噪声将增加20log(88103) = 98.89dB!这就是基准振荡器必须非常干净的原因。环路的动作将使噪声层增加100dB左右,所以,如果想获得满足当今无线电通信需要的足够输出质量,就必须采用高Q值晶体振荡器。

使PLL正常运作

VCO部分

因为VCO由PLL频率合成器来生成信号输出,所以PLL的绝大部分性能都是由它决定的。如果VCO未能正确地运作,则许多性能参数都将受到影响。在调试阶段的初期应对VCO进行测试,以确保其提供预定的频率范围、增益和输出电平。如果只是想测试VCO,则需对PLL进行修正,以取消闭环控制。“断开”环路的一种常用方法是使R3开路(见图2),并在C4的两端施加一个实验室电源,这样就使得VCO调谐电压能够在期望的范围内改变。当调谐电压改变时,应在一个频率计数器(或频谱分析仪)上监视VCO的工作频率。记录若干调谐电压设定值条件下的VCO工作频率。

VCO是否位于正确的频率上?

利用由上述的简单测试所获得的数据,您将可以对VCO能否工作于期望的频率之上做出快速评估。如果VCO产生一个位于183MHz频率之上IF LO(中频本机振荡器),而测试中所记录的最低频率为187MHz,则PLL将无法进行正确的相位锁定。为了对该条件进行校正,应核实VCO振荡回路中的所有谐振元件均具有所需的参数值。例如,若谐振电路电感器L1(见图2)过小,则谐振频率将被提升。

---应始终牢记用于描述一个简单的LC谐振电路的谐振频率的方程式:

Fres为谐振频率(单位:Hz)。

---L为电感值(单位:H)。

--- C为电容值(单位:F)。

---● 是否安装了正确的元器件?

---电抗元件的尺寸非常之小,以致于无法印上可见标签。这就意味着VCO当中的元件的最为容易的测试方法是采用已知数值的元件来进行替换。由于第一块电路板的组装可能是手工完成的,因此很有可能在PCB上焊接了参数值不正确的元件。可根据需要来替换振荡回路中的元件,以使VCO频率接近期望的工作点。

---您可以按照表1所述对VCO进行校正,但PLL仍然有可能出现问题。如果VCO的调谐增益与计算环路滤波元件参数值时所采用的数值相差较大,则环路有可能发生振荡。在图3中,应注意的是由原型设计所获得的实验室数据绘制的曲线的斜率。反馈环路稳定性的获得要求环路增益位于特定的范围内。如果VCO处于正确的频率之上但增益误差较大,则环路本身将发生振荡并导致VCO在众多的频率上被调制。在开环条件下使用您的VCO数据,以验证环路增益接近您的设计目标值。如果VCO的调谐增益过高,则变容二极管将被过于紧密地耦合至谐振电路。应确认安装了正确的变容二极管。将变容二极管耦合至振荡回路的电容器(图2中的C2和C3)可能数值过大。反过来,如果VCO调谐增益较低,则或许需要增大C2和C3的数值。

无线电 滤波器 振荡器 电路 电压 比较器 二极管 电流 电阻 电容 放大器 频谱分析仪 电感 PCB 电容器 总线 示波器 运算放大器 相关文章:

- 可编程无线电遥控多路开关系统设计(11-02)

- 基于ARM9和GPRS的实时电力负控管理系统的设计(04-24)

- 认知无线电技术,三张图即可揭秘?(07-16)

- Molex PowerLife 无线电源线圈采用NuCurrent技术(10-10)

- 单片全桥式 AutoResonant 发送器 IC 简化无线电池充电器设计(01-11)

- 利用环境产生电能 创造无电池无线传感器(04-11)