使用DS1863/DS1865的内部校准和右移位增强ADC性能

时间:06-24

来源:互联网

点击:

|

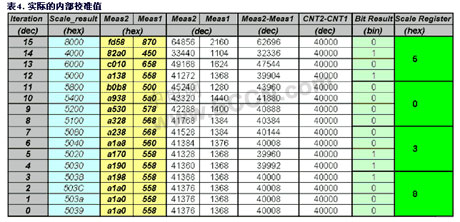

从表3我们可看到最小的差值在第三重复出现(Meas2 - Meas1和CNT2 - CNT1同时为40000)。用户可以在算法中加一个变量来检查最小差值出现的位置,然后用这个重复产生的“增益结果”作为增益校准寄存器的值,替代最终的值。

对于已被编程成新增益校准值的器件,可通过施加10mV (即我们希望其输出读数为0000h的电压)并读取其数字输出结果来确定其偏移校准。此例中所使用的器件在输入为10mV时输出为0558h。利用偏移公式,可将偏移校准计算如下:

MON3失调 = -(-0558h/4) = 0156h

最后,再按下式来计算新钳位值:

新钳位值(预右移) = FFF8h - 0558h = FAA0h

完成内部校准后,即可通过将20h写入表01h中的8Fh来执行2次右移位。

结论

DS1863/DS1865的内部校准及右移位特性,可为用户提供最大的灵活性并使其适用于各种应用。本应用笔记提供了DS1863/DS1865数据资料中未给出的附加信息,例如为什么内部校准及右移位具有优势以及如何来实现等。同时还给出了一个与理论相联系的运用传递方法的实例,并提供了DS1863/DS1865内部校准过程中实际得到的读数。

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)