流水线ADC

时间:06-25

来源:互联网

点击:

低采样速率ADC仍然采用逐次逼近(SAR)、积分型结构以及最近推出的过采样ΣΔADC,而高采样速率(几百MSPS以上)大多用闪速ADC及其各种变型电路。然而,最近几年各种各样的流水线ADC已经在速度、分辨率、动态性能和功耗方面有了很大的提高。对于几Msps到100Msps的8位高速和16位低速模数转换器(ADC),流水线已经成为最流行的模数转换器结构,它可以涵盖很广的应用范围,包括CCD成像、超声成像、数字接收、基站、数字视频(如HDTV)、xDSL、线缆调制解调器以及快速以太网。本文介绍了流水线ADC的内部结构和工作原理。

一、流水线ADC结构

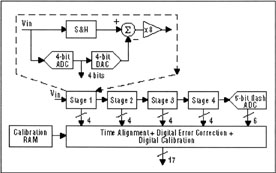

图1为12位流水线ADC的结构图。输入Vin首先被采样/保持(S&H)电路所采样,同时第一级的闪速ADC把它量化为3位,此3位输出送给一3位的DAC(具有12位精度),输入信号减去此DAC的输出,放大4倍送给下一级(第二级),继续重复上述过程,每级提供3位,直到最后一级4位闪速ADC。对应某一次采样,由于每级在不同的时间得到变换结果,因此在进行数字误差校正前用移位寄存器对各级的结果先按时间对准。注意只要某一级完成了某一采样的变换,得到结果并把差值送给下一级,它就可以处理下一个采样。因此流水线操作提高了处理能力。

1. 延迟时间

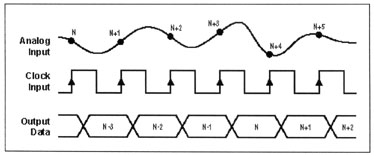

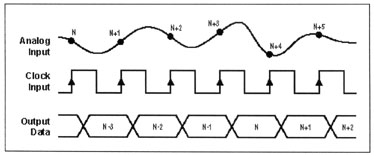

由于每个采样必须通过整个流水线才能得到数字误差校正所需的各个位,因此流水线ADC有数据延迟。在图1的例子中,大约要延时3个周期(见图2)。

2. 数字误差校正

大多数现代流水线ADC采用“数字误差校正”技术来大大降低对闪速ADC(即内部的每个比较器)的精度要求。图1中,3位的差值输出其动态范围是输入信号Vin的1/8,然而随后的增益只有4,因此给第二级的输入只有第二级ADC 3位范围的一半(在第一级的3位变换没有误差的情况下)。

如果第一级的3位闪速ADC的某一个比较器有很大的失调,同时输入电压又正处于此比较点上,那么就会产生不正确3位码和不正确的3位DAC输出,此时产生了不同的差值。可以证明,只要放大后的差值没有超出后续的3位ADC的范围,以后产生的LSB码加上前面不正确的3位MSB码同样能产生正确的ADC结果。实际上,四级流水线中的第一级3位闪速ADC只需4位的精度。数字误差校正不能修正最后4位闪速转换器产生的误差。但是,这里产生的任何误差要除以前面的累积增益(44),因此只要求最后一级的精度大于4位。

在图1的例子中,虽然每级产生3位,但由于级间的增益是4,每级(第一级至第四级)的有效分辨率为2位。额外的位只是用于使尾数减半,使下一级3位ADC有额外的范围进行数字校正。这种方法被称之为级间“1位重叠”。因此整个ADC的有效位数是2+2+2+2+4=12位。

3. 元件精度

数字校正不能修正每个DAC和增益放大器的增益和线性特性。特别是前端的采样保持电路,DAC需要12位的精度。但是随后各级的元件只需较低的精度(如,第二级10位精度,第三级8位,等等),因为他们的误差要除以前面的级间增益。通常利用这一事实把流水线逐级做小来进一步降低功耗。

在大多数采用CMOS和BiCMOS技术的流水线ADC中,采样/保持、DAC、加法器和增益放大器通常用乘法DAC(MDAC)的单开关电容电路来实现。限制MDAC精度的主要因素是内在的电容不匹配。纯双极型实现方法更加复杂,主要受电流源DAC和级间增益放大器中电阻不匹配影响。通常12位或更高精度都需要阻容修正和数字校正,特别是第一级。

4. 数字标定

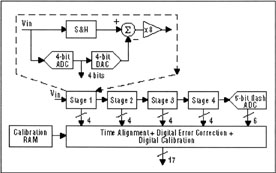

MAX1200/MAX1201/MAX1205系列(16位1Msps、14位1Msps和2Msps ADC)采用数字标定来保证其优越的精度和动态性能。MAX1200系列是CMOS流水线ADC,它由四级4位(其中一位重叠)和最后的5位闪速ADC构成,总位数是3+3+3+3+5=17位(参见图3)。额外的1到3位是数字标定用来量化误差项来达到更高的精度,舍掉它们后,最后得到14位或16位的精度。

标定从第三级的MDAC开始。第三级以上的MDAC误差已经足够小,不必标定。第三级的输出经剩余的流水线ADC数字化后,误差项存入片内的RAM中,第三级标定后,就可以用同样的方式由第三级来标定第二级,同样,第二级标定后,再标定第一级。为了使标定免受噪声的影响,采用取平均的方法(特别是第一和第二级的MDAC)。在正常转换期间,从RAM中取出标定的误差项来调整数字误差校正后的输出结果。

二、各种变型电路

从图1可以看出:根据每级的分辨率多少、最后闪速ADC的位数、是否采用数字标定和修正来提高最初几级的精度可以衍生出各种各样的流水线ADC。采样速率和分辨率部分地决定了每级采用的位数。通常,高速CMOS流水线ADC每级一般用于低位数(甚至每级只有一位,级间增益只有2),原因是CMOS比较难实现很高增益的宽带放大器。低采样速率的CMOS流水线ADC和双极型流水线ADC(即使采样速率很高)每级常采用多位数,这同时也带来了更小的数据延迟。

CMOS MAX1425/MAX1426 (10位10Msps和20Msps)系列使用流行的每级1.5位结构,每级只有1位分辨率和“0.5位重叠”,每级有一个1.5位的闪速ADC(只有2个比较器)。可以证明,利用数字误差校准,可以达到2位闪速ADC和DAC的标准MDAC同样的效果,这些转换器以20Msps速率采样10MHz输入信号时可以达到高达59dB的SNR。

MAX1444/MAX1446/MAX1448/MAX1449系列(10位40/60/80/105Msps)是最新的采用每级1.5位结构的高速甚低功耗10位ADC。它们组合了宽带低失真采样保持放大器,在整个奈奎斯特频率内以及高于奈奎斯特频率内保证了卓越的动态性能。该系列产品可用于数字接收机中的欠采样设计。

一、流水线ADC结构

图1为12位流水线ADC的结构图。输入Vin首先被采样/保持(S&H)电路所采样,同时第一级的闪速ADC把它量化为3位,此3位输出送给一3位的DAC(具有12位精度),输入信号减去此DAC的输出,放大4倍送给下一级(第二级),继续重复上述过程,每级提供3位,直到最后一级4位闪速ADC。对应某一次采样,由于每级在不同的时间得到变换结果,因此在进行数字误差校正前用移位寄存器对各级的结果先按时间对准。注意只要某一级完成了某一采样的变换,得到结果并把差值送给下一级,它就可以处理下一个采样。因此流水线操作提高了处理能力。

1. 延迟时间

由于每个采样必须通过整个流水线才能得到数字误差校正所需的各个位,因此流水线ADC有数据延迟。在图1的例子中,大约要延时3个周期(见图2)。

2. 数字误差校正

大多数现代流水线ADC采用“数字误差校正”技术来大大降低对闪速ADC(即内部的每个比较器)的精度要求。图1中,3位的差值输出其动态范围是输入信号Vin的1/8,然而随后的增益只有4,因此给第二级的输入只有第二级ADC 3位范围的一半(在第一级的3位变换没有误差的情况下)。

如果第一级的3位闪速ADC的某一个比较器有很大的失调,同时输入电压又正处于此比较点上,那么就会产生不正确3位码和不正确的3位DAC输出,此时产生了不同的差值。可以证明,只要放大后的差值没有超出后续的3位ADC的范围,以后产生的LSB码加上前面不正确的3位MSB码同样能产生正确的ADC结果。实际上,四级流水线中的第一级3位闪速ADC只需4位的精度。数字误差校正不能修正最后4位闪速转换器产生的误差。但是,这里产生的任何误差要除以前面的累积增益(44),因此只要求最后一级的精度大于4位。

在图1的例子中,虽然每级产生3位,但由于级间的增益是4,每级(第一级至第四级)的有效分辨率为2位。额外的位只是用于使尾数减半,使下一级3位ADC有额外的范围进行数字校正。这种方法被称之为级间“1位重叠”。因此整个ADC的有效位数是2+2+2+2+4=12位。

3. 元件精度

数字校正不能修正每个DAC和增益放大器的增益和线性特性。特别是前端的采样保持电路,DAC需要12位的精度。但是随后各级的元件只需较低的精度(如,第二级10位精度,第三级8位,等等),因为他们的误差要除以前面的级间增益。通常利用这一事实把流水线逐级做小来进一步降低功耗。

在大多数采用CMOS和BiCMOS技术的流水线ADC中,采样/保持、DAC、加法器和增益放大器通常用乘法DAC(MDAC)的单开关电容电路来实现。限制MDAC精度的主要因素是内在的电容不匹配。纯双极型实现方法更加复杂,主要受电流源DAC和级间增益放大器中电阻不匹配影响。通常12位或更高精度都需要阻容修正和数字校正,特别是第一级。

4. 数字标定

MAX1200/MAX1201/MAX1205系列(16位1Msps、14位1Msps和2Msps ADC)采用数字标定来保证其优越的精度和动态性能。MAX1200系列是CMOS流水线ADC,它由四级4位(其中一位重叠)和最后的5位闪速ADC构成,总位数是3+3+3+3+5=17位(参见图3)。额外的1到3位是数字标定用来量化误差项来达到更高的精度,舍掉它们后,最后得到14位或16位的精度。

标定从第三级的MDAC开始。第三级以上的MDAC误差已经足够小,不必标定。第三级的输出经剩余的流水线ADC数字化后,误差项存入片内的RAM中,第三级标定后,就可以用同样的方式由第三级来标定第二级,同样,第二级标定后,再标定第一级。为了使标定免受噪声的影响,采用取平均的方法(特别是第一和第二级的MDAC)。在正常转换期间,从RAM中取出标定的误差项来调整数字误差校正后的输出结果。

二、各种变型电路

从图1可以看出:根据每级的分辨率多少、最后闪速ADC的位数、是否采用数字标定和修正来提高最初几级的精度可以衍生出各种各样的流水线ADC。采样速率和分辨率部分地决定了每级采用的位数。通常,高速CMOS流水线ADC每级一般用于低位数(甚至每级只有一位,级间增益只有2),原因是CMOS比较难实现很高增益的宽带放大器。低采样速率的CMOS流水线ADC和双极型流水线ADC(即使采样速率很高)每级常采用多位数,这同时也带来了更小的数据延迟。

CMOS MAX1425/MAX1426 (10位10Msps和20Msps)系列使用流行的每级1.5位结构,每级只有1位分辨率和“0.5位重叠”,每级有一个1.5位的闪速ADC(只有2个比较器)。可以证明,利用数字误差校准,可以达到2位闪速ADC和DAC的标准MDAC同样的效果,这些转换器以20Msps速率采样10MHz输入信号时可以达到高达59dB的SNR。

MAX1444/MAX1446/MAX1448/MAX1449系列(10位40/60/80/105Msps)是最新的采用每级1.5位结构的高速甚低功耗10位ADC。它们组合了宽带低失真采样保持放大器,在整个奈奎斯特频率内以及高于奈奎斯特频率内保证了卓越的动态性能。该系列产品可用于数字接收机中的欠采样设计。

ADC 电路 DAC 比较器 电压 放大器 CMOS 电容 电流 电阻 滤波器 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)