无线设备射频功放设计的革命性演进趋势(上)

时间:03-29

来源:互联网

点击:

数字自适应预失真(DAPD)技术的开发

按照摩尔定律,随着数字硬件的价格不断下降,数字自适应预失真(DAPD)校正技术的成本也会逐年降低,变得越来越具吸引力。

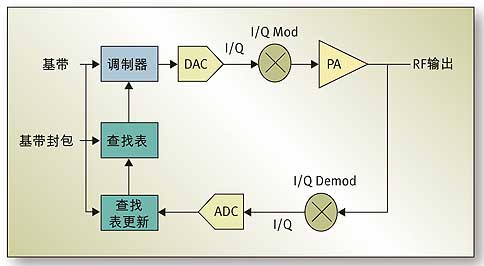

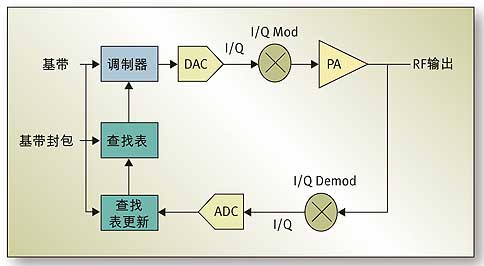

在一个DAPD系统中(如图2所示),PA的输出被采样,下行转换到基带,然后与输入信号进行比较。系统会对由功放所造成的相位和振幅失真进行检测,然后调节基带信号,以准确抵消这些失真。这种技术可以提高PA的总体效率。

预失真的代价不仅仅是成本方面的。RF输出信号的下行转换以及信号处理的执行都会产生额外的功耗。设计工程师必须一直确保效率提高的优势,能够弥补实现这些额外功能性所需的成本代价。查找表往往极少更新,而DAPD模块大多数时间都是关断的,这意味着DAPD的使用一般对材料清单的影响可忽略不计。

图2:数字自适应预失真系统的模块示意图。(基带、调制器、查找表、查找表更新、基带波包、RF 输出)

业界公认,当DAPD与高度非线性技术开发的PA配合使用时,可发挥最大的作用。预失真器所需的功率远远小于放大器的功率,故较大的放大器也同样受到影响。例如,集成式CMOS PA现已开始整合在低功率WiFi 手机中,这些 CMOS PA的fT 非常低,需要在极高的电流密度下工作才能获得所需的线性度,来满足WiFi EVM规范要求。若这些器件在较低电流下工作,它们会变得高度非线性,这时,采用了集成式CMOS PA的WiFi设备必须使用DAPD。但即使是使用了预失真技术,集成式CMOS PA的效率也相当低,一般小于10%。不过,由于这些器件都在较低的输出功率下(通常小于40mW)工作,因此效率不是那么重要,DAPD已能确保足够的线性度。

GaAs和SiGe晶体管的固有线性特征减少了对预失真的需求,可以用作CMOS的替代方案。不过,要注意的是,预失真还可改善误差向量幅度(EVM)和频谱模板(spectral mask),因此能够提高性能。

要优化带DAPD的PA 的性能,最好是按最大效率而非最大线性度来设计。此外,通过优化反馈,设计工程师能够调节预失真以进一步校正EVM或频谱模板。在某些情况下,比如当输出功率增加导致WiFi PA模板特性大幅受限时,因为带外发射(out-of-band emission)的限制规定了最大绝对发射级别,所以这是十分重要的。这方面还有其它一些系统,比如日本新推出的xgPHS,采用了256QAM调制,需要工程师针对EVM校正来优化DAPD。

对DAPD来说,不存在什么优选技术。至于GaAs或BiCMOS PA,预失真不是必须的,但它有助于提高效率,尤其是在输出功率较高时。

对于CMOS PA,因为这种技术的效率相当低,所以预失真却是一项必备要求。

耗电量最小化

PA 一般是根据额定输出功率下的耗电量来标注的,而功率附加效率(PAE)则通常在全功率下定义。当输出功率降低时,从PA流出的电流也随之而降低。但流出的电流与输出功率并不成线性关系,例如,如果输出功率降低50%(3dB),电流一般只减小20%左右。

此外,当输出功率回退近零时,因PA的偏置电流之故,电流不会降为零,而是在PA静态电流(Icq)处达到饱和。

在许多应用中,静态电流无关紧要。譬如,若PA在最大功率附近工作时,只要它发射功率,就会产生功耗,这时回退不重要,且静态电流(Icq)也变得不相关。

802.11 WiFi PA就是这样的典型例子。当数据被发射时,PA启动,并一直在最大功率下工作,但在发射脉冲之间,它则被禁用,并同样只消耗泄漏电流。

如果一个PA是针对广大范围的发射功率而设计的,则回退功率级下的功耗和Icq变得十分重要。这一点在CDMA和WiMAX PA中显然可见。WiMAX需要45dB的最小发射动态范围,因为功率控制是整个网络固有的。(图3显示了CDMA和WiMAX网络中移动设备可能的发射功率分布)。对于CDMA,由图可看出,手机主要在-4dBm下发射,极少在最大功率下发射。

对于WiMAX,手机主要在 10dBm左右下发射,正如CDMA设备很少在最大功率下发射。此图还标示了一个典型PA的耗电量与输出功率的关系。由于PA最常在低功率下发射,因此可看出尽量减小较低输出功率下的耗电量以尽可能延长电池寿命的重要性。

图3:CDMA和WiMAX网络设备的发射功率分布。(输出功率分布、发生概率、电流、输出功率、电流消耗)

至于在回退功率下能否获得高效率,不同技术之间没有什么优势差异──它们全都相当差。例如,典型WiMAX PA的Icq为100mA。如果我们假设PA在0dBm功率时电流为Icq,则功耗为330mW,且在0dBm输出功率下效率只有0.3%;另一方面,在满额定功率下它的效率约为20%。

低输出功率下的功耗降低技术

一项可减小低输出功率下功耗的有效技术,是在低输出功率下使输出级旁路,把RF能量发送到末级周围。输出级是最大的级,吸取电流最多。因为输出级被旁路时无耗电,故这项技术能够降低增益,显着减少PA的电流。

开关是实现输出级旁路最受欢迎的方法。其中最常用的是带有FET开关的技术,因为这些器件的损耗低得多,并且线性度更好。因此,pHEMT或GaAs BiFET工艺都是很好的选择。SiGe BiCMOS工艺也十分适合于开发低静态电流器件。目前的绝缘体上硅(SOI)技术可以创建出媲美GaAs开关的SOI开关。

利用GaAs HBT或CMOS技术来制造高效开关就要困难得多,因此这些技术通常不适合作为超低静态电流的输出级旁路方案。

按照摩尔定律,随着数字硬件的价格不断下降,数字自适应预失真(DAPD)校正技术的成本也会逐年降低,变得越来越具吸引力。

在一个DAPD系统中(如图2所示),PA的输出被采样,下行转换到基带,然后与输入信号进行比较。系统会对由功放所造成的相位和振幅失真进行检测,然后调节基带信号,以准确抵消这些失真。这种技术可以提高PA的总体效率。

预失真的代价不仅仅是成本方面的。RF输出信号的下行转换以及信号处理的执行都会产生额外的功耗。设计工程师必须一直确保效率提高的优势,能够弥补实现这些额外功能性所需的成本代价。查找表往往极少更新,而DAPD模块大多数时间都是关断的,这意味着DAPD的使用一般对材料清单的影响可忽略不计。

图2:数字自适应预失真系统的模块示意图。(基带、调制器、查找表、查找表更新、基带波包、RF 输出)

业界公认,当DAPD与高度非线性技术开发的PA配合使用时,可发挥最大的作用。预失真器所需的功率远远小于放大器的功率,故较大的放大器也同样受到影响。例如,集成式CMOS PA现已开始整合在低功率WiFi 手机中,这些 CMOS PA的fT 非常低,需要在极高的电流密度下工作才能获得所需的线性度,来满足WiFi EVM规范要求。若这些器件在较低电流下工作,它们会变得高度非线性,这时,采用了集成式CMOS PA的WiFi设备必须使用DAPD。但即使是使用了预失真技术,集成式CMOS PA的效率也相当低,一般小于10%。不过,由于这些器件都在较低的输出功率下(通常小于40mW)工作,因此效率不是那么重要,DAPD已能确保足够的线性度。

GaAs和SiGe晶体管的固有线性特征减少了对预失真的需求,可以用作CMOS的替代方案。不过,要注意的是,预失真还可改善误差向量幅度(EVM)和频谱模板(spectral mask),因此能够提高性能。

要优化带DAPD的PA 的性能,最好是按最大效率而非最大线性度来设计。此外,通过优化反馈,设计工程师能够调节预失真以进一步校正EVM或频谱模板。在某些情况下,比如当输出功率增加导致WiFi PA模板特性大幅受限时,因为带外发射(out-of-band emission)的限制规定了最大绝对发射级别,所以这是十分重要的。这方面还有其它一些系统,比如日本新推出的xgPHS,采用了256QAM调制,需要工程师针对EVM校正来优化DAPD。

对DAPD来说,不存在什么优选技术。至于GaAs或BiCMOS PA,预失真不是必须的,但它有助于提高效率,尤其是在输出功率较高时。

对于CMOS PA,因为这种技术的效率相当低,所以预失真却是一项必备要求。

耗电量最小化

PA 一般是根据额定输出功率下的耗电量来标注的,而功率附加效率(PAE)则通常在全功率下定义。当输出功率降低时,从PA流出的电流也随之而降低。但流出的电流与输出功率并不成线性关系,例如,如果输出功率降低50%(3dB),电流一般只减小20%左右。

此外,当输出功率回退近零时,因PA的偏置电流之故,电流不会降为零,而是在PA静态电流(Icq)处达到饱和。

在许多应用中,静态电流无关紧要。譬如,若PA在最大功率附近工作时,只要它发射功率,就会产生功耗,这时回退不重要,且静态电流(Icq)也变得不相关。

802.11 WiFi PA就是这样的典型例子。当数据被发射时,PA启动,并一直在最大功率下工作,但在发射脉冲之间,它则被禁用,并同样只消耗泄漏电流。

如果一个PA是针对广大范围的发射功率而设计的,则回退功率级下的功耗和Icq变得十分重要。这一点在CDMA和WiMAX PA中显然可见。WiMAX需要45dB的最小发射动态范围,因为功率控制是整个网络固有的。(图3显示了CDMA和WiMAX网络中移动设备可能的发射功率分布)。对于CDMA,由图可看出,手机主要在-4dBm下发射,极少在最大功率下发射。

对于WiMAX,手机主要在 10dBm左右下发射,正如CDMA设备很少在最大功率下发射。此图还标示了一个典型PA的耗电量与输出功率的关系。由于PA最常在低功率下发射,因此可看出尽量减小较低输出功率下的耗电量以尽可能延长电池寿命的重要性。

图3:CDMA和WiMAX网络设备的发射功率分布。(输出功率分布、发生概率、电流、输出功率、电流消耗)

至于在回退功率下能否获得高效率,不同技术之间没有什么优势差异──它们全都相当差。例如,典型WiMAX PA的Icq为100mA。如果我们假设PA在0dBm功率时电流为Icq,则功耗为330mW,且在0dBm输出功率下效率只有0.3%;另一方面,在满额定功率下它的效率约为20%。

低输出功率下的功耗降低技术

一项可减小低输出功率下功耗的有效技术,是在低输出功率下使输出级旁路,把RF能量发送到末级周围。输出级是最大的级,吸取电流最多。因为输出级被旁路时无耗电,故这项技术能够降低增益,显着减少PA的电流。

开关是实现输出级旁路最受欢迎的方法。其中最常用的是带有FET开关的技术,因为这些器件的损耗低得多,并且线性度更好。因此,pHEMT或GaAs BiFET工艺都是很好的选择。SiGe BiCMOS工艺也十分适合于开发低静态电流器件。目前的绝缘体上硅(SOI)技术可以创建出媲美GaAs开关的SOI开关。

利用GaAs HBT或CMOS技术来制造高效开关就要困难得多,因此这些技术通常不适合作为超低静态电流的输出级旁路方案。