基于FPGA的3G/HD/SD-SDI信号光纤传输系统的设计

时间:12-04

来源:互联网

点击:

摘要:介绍了基于FPGA和高速串行复接/解复接技术,将3G/HD/SD-SDI信号通过光纤实现无损长距离传输的方法。与传统的传输方案相比,此方案可以完成传输高清视频的平滑升级,并向下兼容现有的视频传输网络,降低了网络的改造升级成本。

引言

SDI(Serial Digital Interface)是一种“数字分量串行接口”,通过75Ω同轴线缆传输无压缩的数字视频信号。由于串行数字信号的数据率很高,在传送前必须经过处理。用扰码的不归零倒置(NRZI)来代替早期的分组编码,其标准为SMPTE 259M和EBU-Tech-3267,标准包括了含数字音频在内的数字复合和数字分量信号,支持4种速率:143Mbit/s的NTSC制复合编码信号;177.3Mbit/s的PAL制复合编码信号;270Mbit/s的NTSC制和PAL制分量编码信号;360Mbit/s 16:9长宽比的NTSC制和PAL制分量编码信号,其中最常见的是270Mbit/s。在传送前,对原始数据流进行扰频并变换为NRZI码,确保在接收端可靠地恢复原始数据。

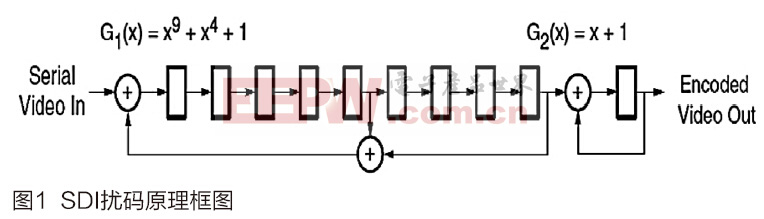

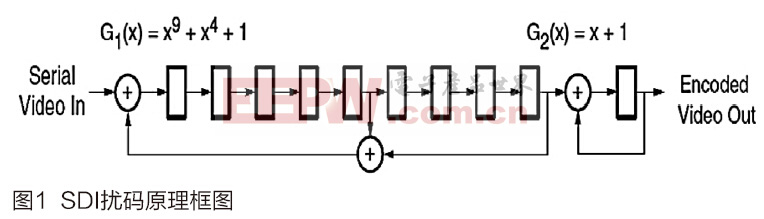

在概念上可以将数字串行接口理解为一种基带信号调制。SDI接口能通过270Mbit/s的串行数字分量信号,对于16:9格式的图像,应能传送360Mbit/s的信号。NRZI码是极性敏感码。用“1”和“0”表示电平的高和低,如果出现长时间的连续“1”或连续“0”,会影响接收端从数字信号中提取时钟。因为串行数字信号接口不单独传送时钟信号,接收端需从数字信号流中提取时钟信号,所以要采用以“1”和“0”来表示有无电平变换的NRZI码。在接收NRZI码流时,只要检出电平变换,就可恢复数据,再经过加扰,连“1”的机会减少,也就使高频分量进一步减少,使解码和提取时钟信息更加容易。实现加扰/解扰的生成多项式为G1(x)=x9+x4+1,该步主要是将数字化的视频信号变成NRZ扰码信号。编码/译码的生成多项式为G2(x)=x+1,该步主要是将上一步生成的NRZ扰码变成对电平极性不敏感、只对电平极性变换敏感的NRZI码。其扰码的原理框图如图1所示。具体实现利用Verilog HDL编程。在接收端,由SDI解码模块从NRZI码流恢复出原数据流。

按照移动图像和电视工程师协会(SMPTE)制定的清晰度标准要求,SDI可分为:SD-SDI、HD-SDI和3G-SDI。其中:

SD-SDI:SD-SDI(Standard Definition Seria Digital Interface) 视频信号的通常速率为270Mbit/s。其信号格式从19.4Mbit/s到360Mbit/s,支持符合SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准,以及DVB-ASI(EN50083-9)等数字电视格式的信号。SD-SDI是无延时、无失真的标清视频信号。

HD-SDI:HD-SDI(High Definition Seria Digital Interface)视频信号的速率达到1.485Gbit/s,刷新率支持60Hz。其信号格式从19.4Mbit/s到1.485Gbit/s,支持符合SMPTE 292M、SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准,以及DVB-ASI(EN50083-9)等数字电视格式的信号。HD-SDI是无延时、无失真的高请视频信号。

3G-SDI:3G-SDI中的3G是指SDI信号的数据传输率约为3Gbit/s。其信号格式从19.4Mbit/s到2.97Gbit/s,支持符合SMPTE 424M、SMPTE 292M、SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准,以及DVB-ASI(EN50083-9)等数字电视格式的信号。由于HDTV可以支持每秒30帧的逐行扫描1920×1080的分辨率格式,而3G能够支持比HD视频信号最高帧扫描频率高一倍的频率,即3G可以支持每秒60帧的HD信号,这在观看动态视频时的差别是很大的。

本文设计的3G/HD/SD-SDI信号的光纤传输方案,支持标清SD-SDI(270Mbit/s)、高清HD-SDI(1.485Gbit/s)及全高清3G-SDI(2.97Gbit/s)视频格式,可传送符合数字视频广播/异步串行接口(DVB-ASI)、标准清晰度(SMPTE 259M)、高清晰度(SMPTE 292M)以及全新的3G-SDI(SMPTE 424M)等标准的视频数据,通过光纤实现3G/HD/SD-SDI信号的高可靠、高性能和长距离传输。采用单模光纤,无中继传输距离可达100km以上。

1 系统设计

由于传输的3G/HD/SD-SDI 信号主要用于广播电视行业,其专业级的指标要求,必须确保输出信号有高稳定性与可靠性。在对信号进行均衡以及时钟恢复,解扰及串并转换,以及后端的输出驱动的处理过程中,均选择GENNUM公司的集成电路实现高清视频信号接口的转换,这样做可以最大限度的保证各相关模块的兼容性,并且具有信号恢复和抖动抑制功能,系统输出接近完美的眼图指标,有利于提高系统的稳定性,降低信号的抖动。

本系统的主控模块是FPGA,综合考虑成本、占用面积以及以后的升级,就需要FPGA的内部资源尽量丰富,因此选用Xilinx公司Spartan-3A系列FPGA,该系列FPGA集成了DSP功能,拥有极强的并行处理能力,满足图像和视频处理所需的性能要求,包括压缩(MPEG-2和MPEG-4),色空间转换,图像增强、处理、缩放和识别等;采用SPI PROM模式完成配置,为便于调试,也预留了JTAG接口; 完成图像采集、存储和整个系统的逻辑控制。

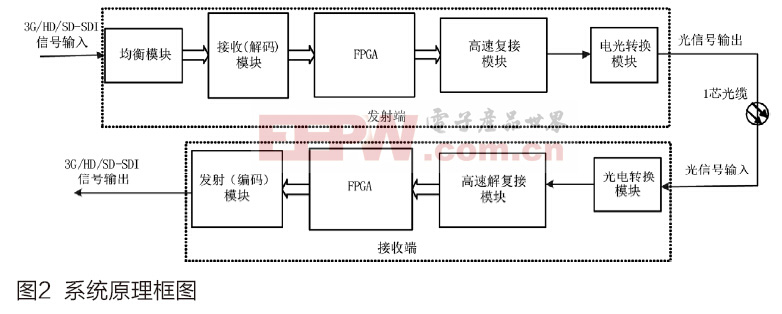

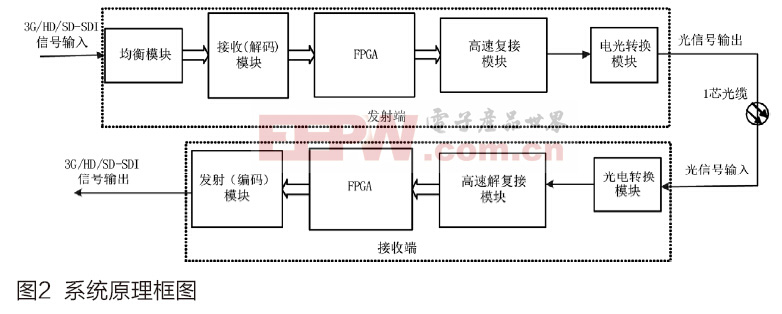

系统分为发射端和接收端。在发射端,信号先经过均衡、串并转换处理,输入到FPGA完成一次复用后,进入高速复接芯片完成二次复用,最后经电光转换模块将其转换为光信号,这样就将3G/HD/SD-SDI信号转变成光信号。在接收端,将接收到的的光信号经光电转换模块转换为电信号,进入高速解复接模块和FPGA中,完成信号解复用和缓存处理后,输入到多速率SDI编码模块,输出原3G/HD/SD-SDI信号。系统原理框图如图2所示。

1.1 发射端

将从同轴电缆输入的3G/HD/SD-SDI信号通过SDI均衡模块完成信号自动均衡,信号经过长距离的传输后在线缆中会产生损耗,经过均衡后,信号质量得到明显的改善。在模块输入引脚处连接75Ω对地电阻进行阻抗匹配。均衡模块对输入信号处理后产生一对差分输出信号,再在两条差分线之间串接100Ω电阻平衡线间阻抗,将此差分信号输入到多速率SDI接收模块进行时钟恢复和8B/10B解码处理,经串/并转换后产生符合SMPTE 424M/292M/259M标准的20/10bit的并行数据,将此数据送入到FPGA中。数据先缓存在FPGA内部FIFO中,在完成对数据的第一次复用后,复用为10bit的并行数据,输出给高速复接模块,将FPGA输出的低速并行信号复接为高速串行信号,再通过电光转换模块(选用速率为3.125Gbit/s,支持热插拔的SFP光器件)转换为光信号传输到接收端。

1.2 接收端

首先将从光缆得到的光信号通过光电转换模块转换成电信号,将此电信号送给高速解复接模块,将高速串行信号进行串并转换处理,将转换后的并行数据输入到FPGA,由FPGA先缓存在内部FIFO中, 再解复用出符合SMPTE 424M/292M/259M标准的20/10bit的并行数据,然后将此并行数据发送给多速率SDI编码模块,从并行数据中提取出时钟,作为采样时钟,对并行数据进行同步处理,同时提取出图像数据和图像格式信息,完成3G/HD/SD-SDI信号的8B/10B编码,最后输出到接收设备,实现了3G/HD/SD-SDI信号的光纤传输。

1.3 硬件电路实现

本系统传输的信号速率从143Mbit/s到2.97Gbit/s,支持符合SMPTE 424M、SMPTE 292M、SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准以及DVB-ASI(EN50083-9)等数字电视格式的信号,满足工业级和广电产品相关标准要求。

系统硬件需要的主要器件包括多速率SDI接收芯片GS2970、多速率SDI发射芯片GS2972、多速率SDI均衡芯片GS2974B 、FPGA+DSP芯片XC3SD1800A、高速复接/解复接芯片TLK3101。芯片GS2974B将输入的3G/HD/SD-SDI信号进行均衡处理。

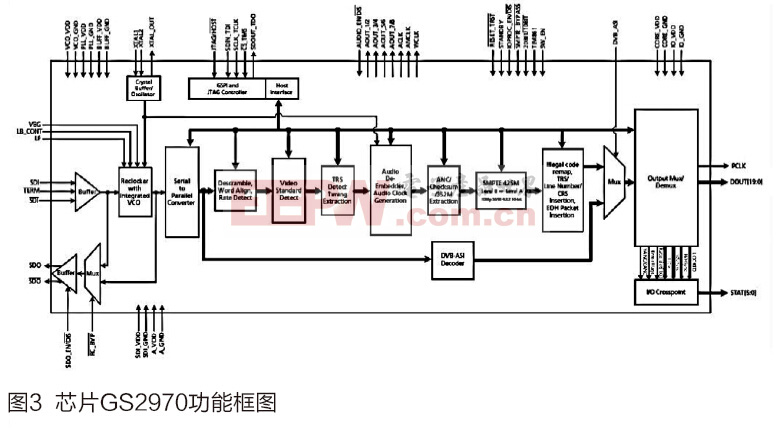

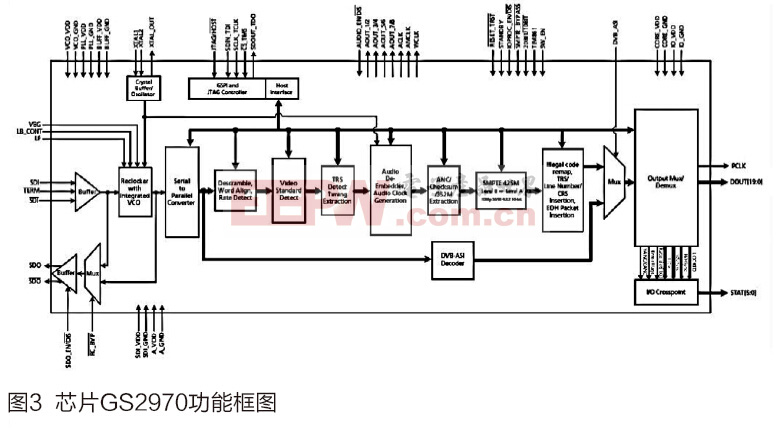

芯片GS2970将输入的SDI串行信号解码,恢复出采样时钟,并将输入的串行数据流转换为并行数据。芯片内部集成带压控振荡器的时钟恢复电路(Reclocker)和时钟恢复串行环路穿越电缆驱动器,可以自动调节输出压摆率,以适应数据的输入速度。芯片的输入抖动容限则高达0.7UI (单位信号时间),因此即使信号的眼图已关闭60%以上,这款芯片仍可接收信号以及将信号解串。芯片具有信号环出功能,本端环出的3G/HD/SD-SDI信号,可直接连至高清显示大屏幕或SDI监控器,可供系统实时检测SDI 信号输入是否正常。其功能框图如图3所示。

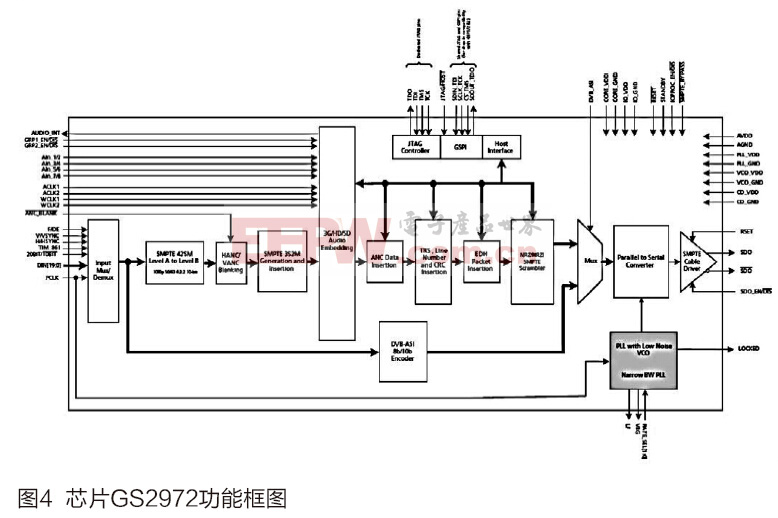

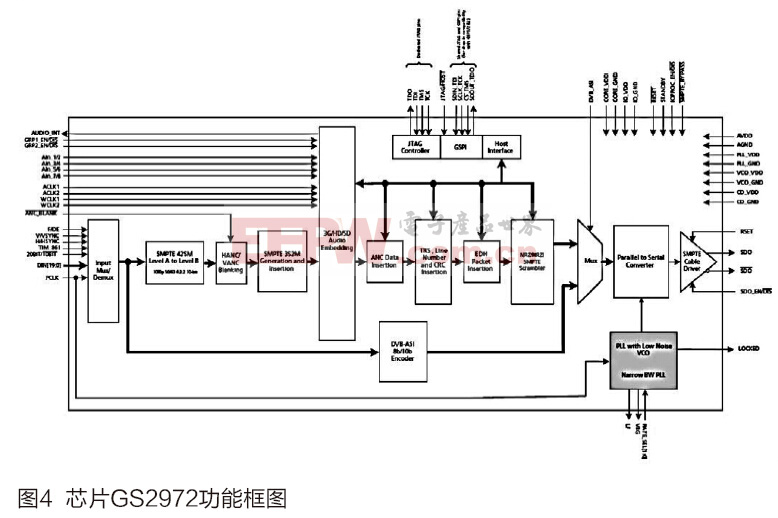

芯片GS2972将接收到的并行数据转换为无压缩的3G/HD/SD-SDI信号。芯片内部集成电缆驱动器、带压控振荡器的时钟恢复模块和高性能PLL锁相环模块,不再需要外置本地时钟及抖动消除电路,有效节约了电路板的面积;芯片只需模拟3.3V、1.2V及数字1.2V供电,且功耗低,只有400mW(包括电缆驱动),大大降低了系统成本。其功能框图如图4所示。

FPGA芯片XC3SD1800A 支持600Mbit/s到3.125Gbit/s的信号速率,从芯片GS2970解码输出的150MHz的20路并行数据, 经FPGA芯片一级复用转换为10 路300MHz的并行数据,同时FPGA芯片对150MHz的时钟频率信号进行倍频产生与原有时钟信号同相的300MHz时钟信号,以提供给行、场同步信号,进而使行、场同步信号与10 路并行数据信号同时复用。 FPGA芯片与编码器或解码器之间采用了LVDS技术,不再使用TTL电平连接。LVDS电平具有非常低的EMI辐射和功率损耗,并提供更高的收发速率;另外,并行数据总线也从20位减少到10位,使得PCB板图设计变得更容易,也降低了对FPGA的等级要求。

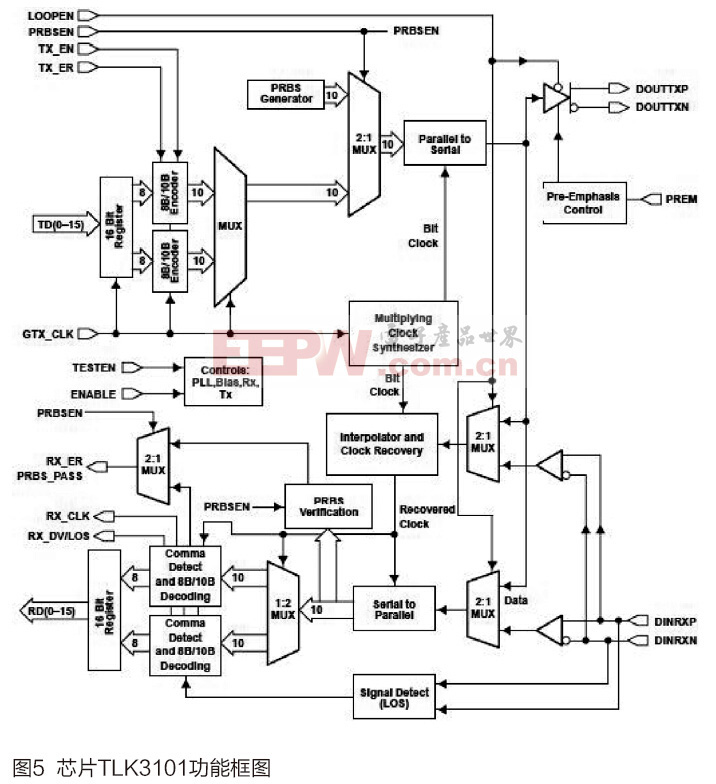

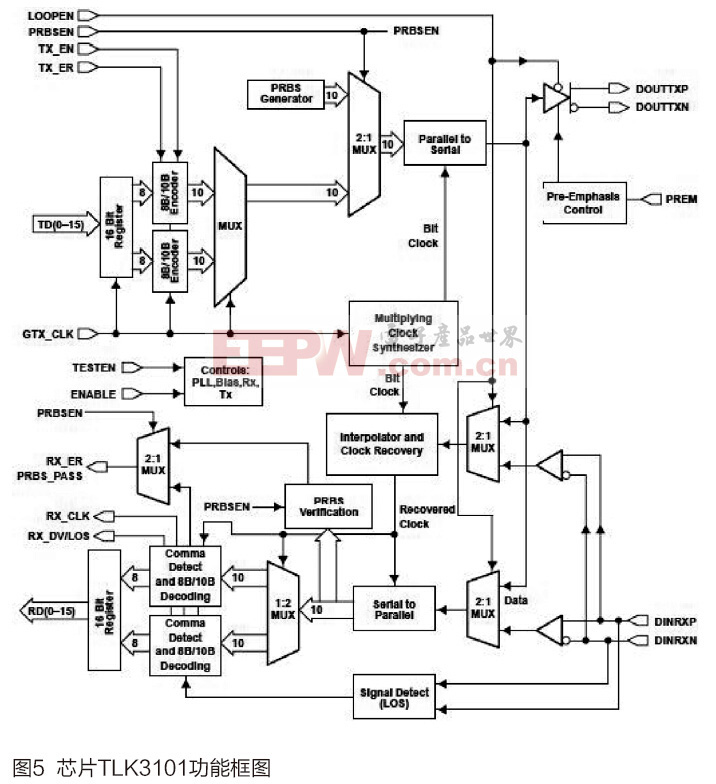

芯片TLK3101将从FPGA芯片接收到的10位并行数据进行8B/10B编码,复接为高速串行信号后输出;同时将输入的高速串行信号先进行8B/10B解码和通道对齐,转换成10位并行数据输出给FPGA芯片。具有信号丢失(LOS)检测功能。可接收的差分输入门限低至200mV。仅需2.5V单电源供电,且功耗低,约450mW(Typical)。其功能框图如图5所示。

引言

SDI(Serial Digital Interface)是一种“数字分量串行接口”,通过75Ω同轴线缆传输无压缩的数字视频信号。由于串行数字信号的数据率很高,在传送前必须经过处理。用扰码的不归零倒置(NRZI)来代替早期的分组编码,其标准为SMPTE 259M和EBU-Tech-3267,标准包括了含数字音频在内的数字复合和数字分量信号,支持4种速率:143Mbit/s的NTSC制复合编码信号;177.3Mbit/s的PAL制复合编码信号;270Mbit/s的NTSC制和PAL制分量编码信号;360Mbit/s 16:9长宽比的NTSC制和PAL制分量编码信号,其中最常见的是270Mbit/s。在传送前,对原始数据流进行扰频并变换为NRZI码,确保在接收端可靠地恢复原始数据。

在概念上可以将数字串行接口理解为一种基带信号调制。SDI接口能通过270Mbit/s的串行数字分量信号,对于16:9格式的图像,应能传送360Mbit/s的信号。NRZI码是极性敏感码。用“1”和“0”表示电平的高和低,如果出现长时间的连续“1”或连续“0”,会影响接收端从数字信号中提取时钟。因为串行数字信号接口不单独传送时钟信号,接收端需从数字信号流中提取时钟信号,所以要采用以“1”和“0”来表示有无电平变换的NRZI码。在接收NRZI码流时,只要检出电平变换,就可恢复数据,再经过加扰,连“1”的机会减少,也就使高频分量进一步减少,使解码和提取时钟信息更加容易。实现加扰/解扰的生成多项式为G1(x)=x9+x4+1,该步主要是将数字化的视频信号变成NRZ扰码信号。编码/译码的生成多项式为G2(x)=x+1,该步主要是将上一步生成的NRZ扰码变成对电平极性不敏感、只对电平极性变换敏感的NRZI码。其扰码的原理框图如图1所示。具体实现利用Verilog HDL编程。在接收端,由SDI解码模块从NRZI码流恢复出原数据流。

按照移动图像和电视工程师协会(SMPTE)制定的清晰度标准要求,SDI可分为:SD-SDI、HD-SDI和3G-SDI。其中:

SD-SDI:SD-SDI(Standard Definition Seria Digital Interface) 视频信号的通常速率为270Mbit/s。其信号格式从19.4Mbit/s到360Mbit/s,支持符合SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准,以及DVB-ASI(EN50083-9)等数字电视格式的信号。SD-SDI是无延时、无失真的标清视频信号。

HD-SDI:HD-SDI(High Definition Seria Digital Interface)视频信号的速率达到1.485Gbit/s,刷新率支持60Hz。其信号格式从19.4Mbit/s到1.485Gbit/s,支持符合SMPTE 292M、SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准,以及DVB-ASI(EN50083-9)等数字电视格式的信号。HD-SDI是无延时、无失真的高请视频信号。

3G-SDI:3G-SDI中的3G是指SDI信号的数据传输率约为3Gbit/s。其信号格式从19.4Mbit/s到2.97Gbit/s,支持符合SMPTE 424M、SMPTE 292M、SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准,以及DVB-ASI(EN50083-9)等数字电视格式的信号。由于HDTV可以支持每秒30帧的逐行扫描1920×1080的分辨率格式,而3G能够支持比HD视频信号最高帧扫描频率高一倍的频率,即3G可以支持每秒60帧的HD信号,这在观看动态视频时的差别是很大的。

本文设计的3G/HD/SD-SDI信号的光纤传输方案,支持标清SD-SDI(270Mbit/s)、高清HD-SDI(1.485Gbit/s)及全高清3G-SDI(2.97Gbit/s)视频格式,可传送符合数字视频广播/异步串行接口(DVB-ASI)、标准清晰度(SMPTE 259M)、高清晰度(SMPTE 292M)以及全新的3G-SDI(SMPTE 424M)等标准的视频数据,通过光纤实现3G/HD/SD-SDI信号的高可靠、高性能和长距离传输。采用单模光纤,无中继传输距离可达100km以上。

1 系统设计

由于传输的3G/HD/SD-SDI 信号主要用于广播电视行业,其专业级的指标要求,必须确保输出信号有高稳定性与可靠性。在对信号进行均衡以及时钟恢复,解扰及串并转换,以及后端的输出驱动的处理过程中,均选择GENNUM公司的集成电路实现高清视频信号接口的转换,这样做可以最大限度的保证各相关模块的兼容性,并且具有信号恢复和抖动抑制功能,系统输出接近完美的眼图指标,有利于提高系统的稳定性,降低信号的抖动。

本系统的主控模块是FPGA,综合考虑成本、占用面积以及以后的升级,就需要FPGA的内部资源尽量丰富,因此选用Xilinx公司Spartan-3A系列FPGA,该系列FPGA集成了DSP功能,拥有极强的并行处理能力,满足图像和视频处理所需的性能要求,包括压缩(MPEG-2和MPEG-4),色空间转换,图像增强、处理、缩放和识别等;采用SPI PROM模式完成配置,为便于调试,也预留了JTAG接口; 完成图像采集、存储和整个系统的逻辑控制。

系统分为发射端和接收端。在发射端,信号先经过均衡、串并转换处理,输入到FPGA完成一次复用后,进入高速复接芯片完成二次复用,最后经电光转换模块将其转换为光信号,这样就将3G/HD/SD-SDI信号转变成光信号。在接收端,将接收到的的光信号经光电转换模块转换为电信号,进入高速解复接模块和FPGA中,完成信号解复用和缓存处理后,输入到多速率SDI编码模块,输出原3G/HD/SD-SDI信号。系统原理框图如图2所示。

1.1 发射端

将从同轴电缆输入的3G/HD/SD-SDI信号通过SDI均衡模块完成信号自动均衡,信号经过长距离的传输后在线缆中会产生损耗,经过均衡后,信号质量得到明显的改善。在模块输入引脚处连接75Ω对地电阻进行阻抗匹配。均衡模块对输入信号处理后产生一对差分输出信号,再在两条差分线之间串接100Ω电阻平衡线间阻抗,将此差分信号输入到多速率SDI接收模块进行时钟恢复和8B/10B解码处理,经串/并转换后产生符合SMPTE 424M/292M/259M标准的20/10bit的并行数据,将此数据送入到FPGA中。数据先缓存在FPGA内部FIFO中,在完成对数据的第一次复用后,复用为10bit的并行数据,输出给高速复接模块,将FPGA输出的低速并行信号复接为高速串行信号,再通过电光转换模块(选用速率为3.125Gbit/s,支持热插拔的SFP光器件)转换为光信号传输到接收端。

1.2 接收端

首先将从光缆得到的光信号通过光电转换模块转换成电信号,将此电信号送给高速解复接模块,将高速串行信号进行串并转换处理,将转换后的并行数据输入到FPGA,由FPGA先缓存在内部FIFO中, 再解复用出符合SMPTE 424M/292M/259M标准的20/10bit的并行数据,然后将此并行数据发送给多速率SDI编码模块,从并行数据中提取出时钟,作为采样时钟,对并行数据进行同步处理,同时提取出图像数据和图像格式信息,完成3G/HD/SD-SDI信号的8B/10B编码,最后输出到接收设备,实现了3G/HD/SD-SDI信号的光纤传输。

1.3 硬件电路实现

本系统传输的信号速率从143Mbit/s到2.97Gbit/s,支持符合SMPTE 424M、SMPTE 292M、SMPTE 259M、SMPTE 297M、SMPTE 305M、SMPTE 310M标准以及DVB-ASI(EN50083-9)等数字电视格式的信号,满足工业级和广电产品相关标准要求。

系统硬件需要的主要器件包括多速率SDI接收芯片GS2970、多速率SDI发射芯片GS2972、多速率SDI均衡芯片GS2974B 、FPGA+DSP芯片XC3SD1800A、高速复接/解复接芯片TLK3101。芯片GS2974B将输入的3G/HD/SD-SDI信号进行均衡处理。

芯片GS2970将输入的SDI串行信号解码,恢复出采样时钟,并将输入的串行数据流转换为并行数据。芯片内部集成带压控振荡器的时钟恢复电路(Reclocker)和时钟恢复串行环路穿越电缆驱动器,可以自动调节输出压摆率,以适应数据的输入速度。芯片的输入抖动容限则高达0.7UI (单位信号时间),因此即使信号的眼图已关闭60%以上,这款芯片仍可接收信号以及将信号解串。芯片具有信号环出功能,本端环出的3G/HD/SD-SDI信号,可直接连至高清显示大屏幕或SDI监控器,可供系统实时检测SDI 信号输入是否正常。其功能框图如图3所示。

芯片GS2972将接收到的并行数据转换为无压缩的3G/HD/SD-SDI信号。芯片内部集成电缆驱动器、带压控振荡器的时钟恢复模块和高性能PLL锁相环模块,不再需要外置本地时钟及抖动消除电路,有效节约了电路板的面积;芯片只需模拟3.3V、1.2V及数字1.2V供电,且功耗低,只有400mW(包括电缆驱动),大大降低了系统成本。其功能框图如图4所示。

FPGA芯片XC3SD1800A 支持600Mbit/s到3.125Gbit/s的信号速率,从芯片GS2970解码输出的150MHz的20路并行数据, 经FPGA芯片一级复用转换为10 路300MHz的并行数据,同时FPGA芯片对150MHz的时钟频率信号进行倍频产生与原有时钟信号同相的300MHz时钟信号,以提供给行、场同步信号,进而使行、场同步信号与10 路并行数据信号同时复用。 FPGA芯片与编码器或解码器之间采用了LVDS技术,不再使用TTL电平连接。LVDS电平具有非常低的EMI辐射和功率损耗,并提供更高的收发速率;另外,并行数据总线也从20位减少到10位,使得PCB板图设计变得更容易,也降低了对FPGA的等级要求。

芯片TLK3101将从FPGA芯片接收到的10位并行数据进行8B/10B编码,复接为高速串行信号后输出;同时将输入的高速串行信号先进行8B/10B解码和通道对齐,转换成10位并行数据输出给FPGA芯片。具有信号丢失(LOS)检测功能。可接收的差分输入门限低至200mV。仅需2.5V单电源供电,且功耗低,约450mW(Typical)。其功能框图如图5所示。

FPGA Verilog 数字电视 集成电路 Xilinx DSP 电阻 电路 振荡器 编码器 解码器 总线 PCB 电子 相关文章:

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)