物联网和可穿戴设备:重新思考存储设备的设计

时间:08-12

来源:互联网

点击:

作者: Howard Sian

几十年来,我们对漫画书和科幻小说中常常出现的腕式对讲机非常熟悉,而工程师们实现这一技术要比作家凭空想出这一场景困难得多。直到今天,它们才逐渐走进我们的生活。如果当下无处不在的智能手机是《星际迷航》所幻想出来的沟通工具,那么可穿戴设备(例如智能手表、健身腕带或是将我们的手指变成手势控制器的指环),则最终能将最新的高科技带给大众。但可穿戴设备并不仅仅是现有移动设备的演变,它的物理尺寸和电路要求与智能手机有着极大的不同,这让它们属于完全不同的硬件类别。物理尺寸、电池容量和使用环境(防水防震等特性对可穿戴设备来说要重要得多)的差异意味着可穿戴设备在设计上具有不同的要求和局限性。设计师不能寄希望于仅仅改变现有智能手机的尺寸就能得到可供使用的智能手表。

想要了解这种不同,只需对比两种在各自领域领先的不同产品,以Pebble智能手表和iPhone 5S为例:在封装密度方面,前者的外壳仅为43×34毫米,约是4英寸屏幕iPhone手机表面积的1/5。在10毫米厚的外壳内,Pebble的设计师必须让其容纳下一个2.3英寸的LED显示屏和包含存储器、系统芯片控制器、各种传感器、蓝牙芯片和电池的电路板。所有组件都被设计在一个双面电路板上,相关组件和连接的空间极其有限,但对于消费者来说,手表自然是越薄越好。

对于可穿戴设备的设计要求并不止步于封装。由于容纳电池的空间有限,产品在运行和待机模式下均需极为省电,但又需支持蓝牙通信,可立刻启动,还要能无缝运行用户设定的应用程序。没有人会仅仅为了看时间而购买智能手表,但与漫画书不同的是,很少有人希望用智能手表、互联眼镜或健身腕带来取代智能手机,这在某种程度上降低了设计的难度。而智能手机也正在发展成为多用途中心,可支持、连接越来越多的可穿戴设备。这也意味着大多数可穿戴设备都不需要大容量永久性存储或快速的多核处理器。因此,综合考虑容量、尺寸和用电量要求,可穿戴设备是使用NOR闪存的理想平台。

回到未来:NOR闪存最适用于可穿戴设备

在智能手机能够存储一季里值得收藏的电视秀或完整音乐库之前,当手机还只是部电话时, NOR闪存曾是手机首选的永久性存储介质。NAND成序列地存储多个比特(bit),通过牺牲随机存取的方式来获得密度和写入速度,而NOR则更像传统的DRAM——可以分别读写每一个存储单元,而不是一次读写整个块。这意味着NOR适用于可在本地执行而无需首先复制到另外的RAM缓存的应用程序代码。随机存取还意味着NOR闪存具备高速写入速度——对于串行设计(串行外设接口)可高达20MB/s,对于并行NOR设计可高达250MB/s。

在可穿戴设备中使用NOR闪存而不是NAND具有明显的益处。NOR闪存的直接代码执行能力可显著缩短启动时间,可以让设备立刻启动。同样,代码执行无需RAM就意味着待机时的用电量大大减少,因此在可穿戴设备必须使用微型电池的条件下,设备的使用时间可以得到延长。

由于可穿戴设备一般会连接到另一个设备上,通过该设备连接互联网服务和数据库,所以它们无需存储太多本地数据。相对音频和视频文件的大小而言,就算是一整天的健康和健身测量数据都是极小的。鉴于可穿戴设备中的空间十分有限,NOR闪存容量与芯片尺寸比NAND更适合于应用程序的需求。

第二点可能会让人感到意外,因为NAND闪存阵列的密度要大大高于NOR。实际上,由于NAND闪存针对最大密度设计,所以产品一般会使用最小工艺节点,目前为16nm 。但问题是,除了存储单元之外,所有存储器器件都有一定的电路开销,例如行地址解码器、感应放大器、位线控制电路、外围I/O电路、电压调节器和I/O针脚等子系统。芯片上的开销区并不与存储容量成线性增加。缩减存储阵列的尺寸后,芯片上用于外围逻辑的空间只会少量增加。这意味着即使使用上一代的25nm工艺尺寸,最小可行的NAND器件也是1Gbit。这对于大多数可穿戴应用都是无法接受的,因为市场主要需要的是512Mbit或更小的存储器件。

针对特定制程尺寸缩减NAND容量的局限性也让封装后的尺寸对于许多可穿戴应用来说过大。例如,用作某些应用的NOR替代品的1Gbit串行NAND采用了9×11毫米63球栅阵列封装方式。与之相反,最小的串行NOR 512Mbit和1Gbit NOR产品采用4或5×6毫米封装方式,不到NAND替代品的1/3,因此更适合于可穿戴设备和物联网生态系统中其他联网传感器的微型电路板。

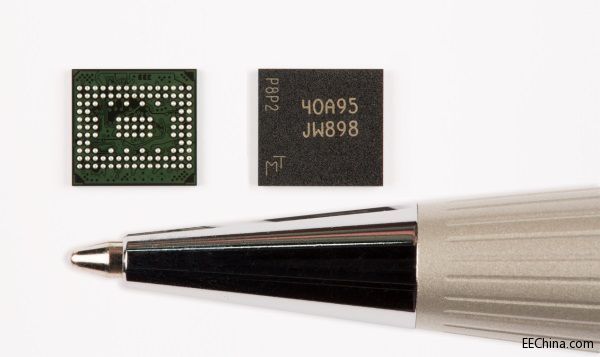

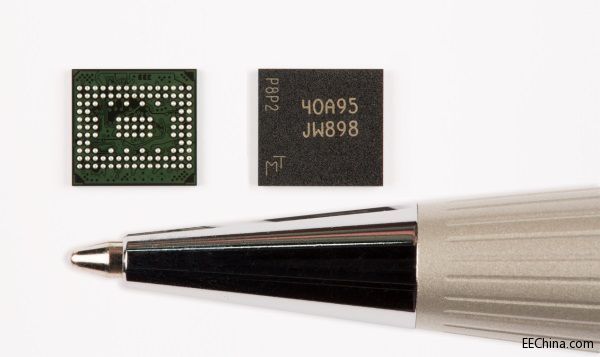

图1:美光NOR闪存MCP尺寸比较。

NOR闪存也可被堆叠在设计有伪静态PSRAM的多芯片封装(MCP)中,已让控制器芯片内嵌入SRAM的应用的容量大于那些系统芯片的常见的1Mbit。例如,含64Mbit NOR闪存和32Mbit PSRAM的52球MCP仅为4×6毫米,含高达512Mb NOR闪存和128Mb PSRAM的密度较高的MCP仅为8×8毫米。参见图1美光NOR闪存MCP尺寸比较。其容量和耗电量对于大多数可穿戴设备来说可能都过大,但它或许可以应用于录制视频,例如眼镜或移动传感设备中。

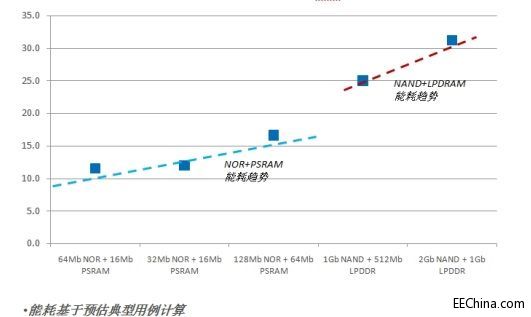

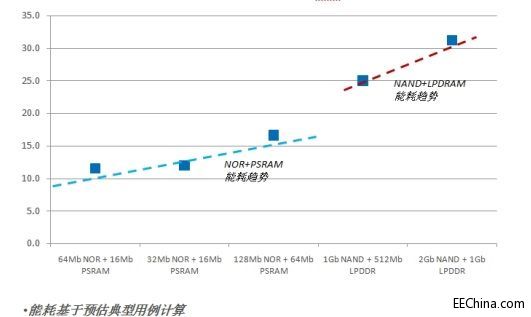

图2:多芯片封装能耗预估

几十年来,我们对漫画书和科幻小说中常常出现的腕式对讲机非常熟悉,而工程师们实现这一技术要比作家凭空想出这一场景困难得多。直到今天,它们才逐渐走进我们的生活。如果当下无处不在的智能手机是《星际迷航》所幻想出来的沟通工具,那么可穿戴设备(例如智能手表、健身腕带或是将我们的手指变成手势控制器的指环),则最终能将最新的高科技带给大众。但可穿戴设备并不仅仅是现有移动设备的演变,它的物理尺寸和电路要求与智能手机有着极大的不同,这让它们属于完全不同的硬件类别。物理尺寸、电池容量和使用环境(防水防震等特性对可穿戴设备来说要重要得多)的差异意味着可穿戴设备在设计上具有不同的要求和局限性。设计师不能寄希望于仅仅改变现有智能手机的尺寸就能得到可供使用的智能手表。

想要了解这种不同,只需对比两种在各自领域领先的不同产品,以Pebble智能手表和iPhone 5S为例:在封装密度方面,前者的外壳仅为43×34毫米,约是4英寸屏幕iPhone手机表面积的1/5。在10毫米厚的外壳内,Pebble的设计师必须让其容纳下一个2.3英寸的LED显示屏和包含存储器、系统芯片控制器、各种传感器、蓝牙芯片和电池的电路板。所有组件都被设计在一个双面电路板上,相关组件和连接的空间极其有限,但对于消费者来说,手表自然是越薄越好。

对于可穿戴设备的设计要求并不止步于封装。由于容纳电池的空间有限,产品在运行和待机模式下均需极为省电,但又需支持蓝牙通信,可立刻启动,还要能无缝运行用户设定的应用程序。没有人会仅仅为了看时间而购买智能手表,但与漫画书不同的是,很少有人希望用智能手表、互联眼镜或健身腕带来取代智能手机,这在某种程度上降低了设计的难度。而智能手机也正在发展成为多用途中心,可支持、连接越来越多的可穿戴设备。这也意味着大多数可穿戴设备都不需要大容量永久性存储或快速的多核处理器。因此,综合考虑容量、尺寸和用电量要求,可穿戴设备是使用NOR闪存的理想平台。

回到未来:NOR闪存最适用于可穿戴设备

在智能手机能够存储一季里值得收藏的电视秀或完整音乐库之前,当手机还只是部电话时, NOR闪存曾是手机首选的永久性存储介质。NAND成序列地存储多个比特(bit),通过牺牲随机存取的方式来获得密度和写入速度,而NOR则更像传统的DRAM——可以分别读写每一个存储单元,而不是一次读写整个块。这意味着NOR适用于可在本地执行而无需首先复制到另外的RAM缓存的应用程序代码。随机存取还意味着NOR闪存具备高速写入速度——对于串行设计(串行外设接口)可高达20MB/s,对于并行NOR设计可高达250MB/s。

在可穿戴设备中使用NOR闪存而不是NAND具有明显的益处。NOR闪存的直接代码执行能力可显著缩短启动时间,可以让设备立刻启动。同样,代码执行无需RAM就意味着待机时的用电量大大减少,因此在可穿戴设备必须使用微型电池的条件下,设备的使用时间可以得到延长。

由于可穿戴设备一般会连接到另一个设备上,通过该设备连接互联网服务和数据库,所以它们无需存储太多本地数据。相对音频和视频文件的大小而言,就算是一整天的健康和健身测量数据都是极小的。鉴于可穿戴设备中的空间十分有限,NOR闪存容量与芯片尺寸比NAND更适合于应用程序的需求。

第二点可能会让人感到意外,因为NAND闪存阵列的密度要大大高于NOR。实际上,由于NAND闪存针对最大密度设计,所以产品一般会使用最小工艺节点,目前为16nm 。但问题是,除了存储单元之外,所有存储器器件都有一定的电路开销,例如行地址解码器、感应放大器、位线控制电路、外围I/O电路、电压调节器和I/O针脚等子系统。芯片上的开销区并不与存储容量成线性增加。缩减存储阵列的尺寸后,芯片上用于外围逻辑的空间只会少量增加。这意味着即使使用上一代的25nm工艺尺寸,最小可行的NAND器件也是1Gbit。这对于大多数可穿戴应用都是无法接受的,因为市场主要需要的是512Mbit或更小的存储器件。

针对特定制程尺寸缩减NAND容量的局限性也让封装后的尺寸对于许多可穿戴应用来说过大。例如,用作某些应用的NOR替代品的1Gbit串行NAND采用了9×11毫米63球栅阵列封装方式。与之相反,最小的串行NOR 512Mbit和1Gbit NOR产品采用4或5×6毫米封装方式,不到NAND替代品的1/3,因此更适合于可穿戴设备和物联网生态系统中其他联网传感器的微型电路板。

图1:美光NOR闪存MCP尺寸比较。

NOR闪存也可被堆叠在设计有伪静态PSRAM的多芯片封装(MCP)中,已让控制器芯片内嵌入SRAM的应用的容量大于那些系统芯片的常见的1Mbit。例如,含64Mbit NOR闪存和32Mbit PSRAM的52球MCP仅为4×6毫米,含高达512Mb NOR闪存和128Mb PSRAM的密度较高的MCP仅为8×8毫米。参见图1美光NOR闪存MCP尺寸比较。其容量和耗电量对于大多数可穿戴设备来说可能都过大,但它或许可以应用于录制视频,例如眼镜或移动传感设备中。

图2:多芯片封装能耗预估

电路 LED 传感器 蓝牙 解码器 放大器 电压 物联网 平板电脑 相关文章:

- 浅谈E1线路维护技术与应用(01-12)

- R4网络接口和电路域容灾技术(01-05)

- 移动通信网引入IMS的相关探讨(02-21)

- 未来接入网的结构与演进(01-26)

- 电子熔丝在计算机应用中的优势(06-08)

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)