STM-1并行帧同步系统的设计与FPGA实现

时间:12-07

来源:互联网

点击:

2 综合与验证

首先使用Altera公司的QuartusII集成开发平台进行逻辑综合与静态时序分析(Static Timing Analysis)。选择器件型号为Cyclone系列的EP1C6T144C8。由于16比特移位寄存器工作在155.52MHz时钟频率下,为了使这部分电路能稳定可靠地工作,在综合器的设置中必须选择速度优先的优化技术,并对相关路径设计严格的时序约束条件,同时在布局布线器的设置中选择物理综合(Physical Synthesis)优化技术,否则移位寄存器将不能正确地缓存每比特码流数据。

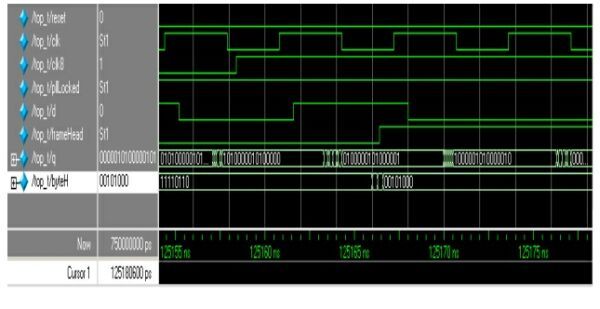

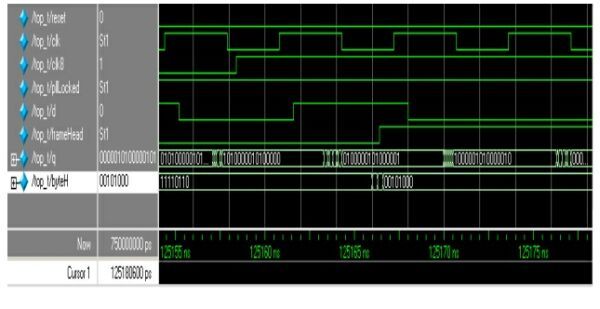

由于QuartusII工具通过NativeLink技术无缝地支持第三方仿真工具,这里采用Mentor Graphics公司的ModelSim工具提取QuartusII产生的Verilog输出网表文件和标准延时格式(Standard Delay Format)文件,进行RTL级功能仿真与门级时序仿真。由于QuartusII支持的仿真测试向量文件为图形格式的VWF(Vector Waveform File)文件,不支持Verilog文本测试向量,在测试大型设计项目时,图形格式测试向量的编写效率低、可读性差、不易于修改和维护。而ModelSim作为业界标准的硬件描述语言仿真平台,支持高效简洁的Verilog文本测试向量输入,大大提高了测试向量编写的有效性和准确性。同时ModelSim的仿真运算速度也远高于QuartusII集成的仿真工具,可大大缩短系统开发周期,加快设计进程。门级时序仿真得到的波形如图5所示。

图5:系统门级仿真波形

图5中clk8为晶振产生的19.44MHz时钟,clk为FPGA内置锁相环8倍频产生的155.52MHz时钟,d为输入的STM-1比特码流,frameHead信号为产生的帧头指示信号,byteH为串并转换后得到的STM-1字节码流。由图可知,在连续接收到两次正确的帧同步码组后,系统进入同步状态,输出帧头指示信号。

3 本文小结

本文提出了高速率STM-1码流并行帧同步系统的设计方案,并在实际FPGA器件中实现了物理验证,得到了稳定可靠的工作电路。这里采用的是将1个串行码流转换为8个并行码流的并行计算技术,对于STM-4、STM-16等更高速率的码流,可以将串行码流转换为更多的并行码流,系统设计方案无需作大的调整,就可以实现高速码流的帧同步系统。

首先使用Altera公司的QuartusII集成开发平台进行逻辑综合与静态时序分析(Static Timing Analysis)。选择器件型号为Cyclone系列的EP1C6T144C8。由于16比特移位寄存器工作在155.52MHz时钟频率下,为了使这部分电路能稳定可靠地工作,在综合器的设置中必须选择速度优先的优化技术,并对相关路径设计严格的时序约束条件,同时在布局布线器的设置中选择物理综合(Physical Synthesis)优化技术,否则移位寄存器将不能正确地缓存每比特码流数据。

由于QuartusII工具通过NativeLink技术无缝地支持第三方仿真工具,这里采用Mentor Graphics公司的ModelSim工具提取QuartusII产生的Verilog输出网表文件和标准延时格式(Standard Delay Format)文件,进行RTL级功能仿真与门级时序仿真。由于QuartusII支持的仿真测试向量文件为图形格式的VWF(Vector Waveform File)文件,不支持Verilog文本测试向量,在测试大型设计项目时,图形格式测试向量的编写效率低、可读性差、不易于修改和维护。而ModelSim作为业界标准的硬件描述语言仿真平台,支持高效简洁的Verilog文本测试向量输入,大大提高了测试向量编写的有效性和准确性。同时ModelSim的仿真运算速度也远高于QuartusII集成的仿真工具,可大大缩短系统开发周期,加快设计进程。门级时序仿真得到的波形如图5所示。

图5:系统门级仿真波形

图5中clk8为晶振产生的19.44MHz时钟,clk为FPGA内置锁相环8倍频产生的155.52MHz时钟,d为输入的STM-1比特码流,frameHead信号为产生的帧头指示信号,byteH为串并转换后得到的STM-1字节码流。由图可知,在连续接收到两次正确的帧同步码组后,系统进入同步状态,输出帧头指示信号。

3 本文小结

本文提出了高速率STM-1码流并行帧同步系统的设计方案,并在实际FPGA器件中实现了物理验证,得到了稳定可靠的工作电路。这里采用的是将1个串行码流转换为8个并行码流的并行计算技术,对于STM-4、STM-16等更高速率的码流,可以将串行码流转换为更多的并行码流,系统设计方案无需作大的调整,就可以实现高速码流的帧同步系统。

FPGA 电路 总线 比较器 Verilog Altera Quartus 仿真 Mentor ModelSim 相关文章:

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)