基于CPLD的计算机并口EPP模式通讯实现

时间:11-28

来源:互联网

点击:

3、并口EPP模式外围电路硬件设计实例

由上文可知,并口EPP模式下的数据传输速度可以达到μs级,所以使用一般的单片机来控制外设与EPP的通讯显然不能满足高速的要求。早期,工程师使用大量的逻辑分立元件来设计EPP的外围电路,但是当计算机的主频越来越高,EPP 模式在高速数据传输中可靠性明显下降, 因此本文采用大规模可编程逻辑器件, 充分利用其高速和大容量特性设计接口电路, 不仅可大大提高其可靠性, 且易于系统扩展和升级, 可广泛用于数据采集、D/A 转换以及数字控制。

笔者采用Xilinx公司的XC95144芯片作为EPP接口模块的控制单元,并且通过XC95144实现了计算机并口与外部存储器SRAM的数据交换。在某些外设需要数据存储和与PC机进行数据交换的应用场合得到了成功的应用。该EPP接口模块的总体框架如图4所示。

图4 EPP接口模块逻辑框图

如图4所示,CPLD内部由各个负责不同功能的子模块组成,其作用与早期的分立元件一样,所有子模块用Verilog设计实现,并且通过了仿真验证。采用ECS将所有的子模块组织起来,集成在一块CPLD内。这样做大大提高了整个系统运行的可靠性,同时也为系统扩展其他功能提供条件。

由于SRAM相对DRAM具有存储速度块,无需定时刷新,控制信号简单的优点,所以被广泛的用于需要高速数据处理的小型设备中。图4中的SRAM采用ISSI的IS61C6416,存储容量是64K×16位。地址线和数据线都是16条,但是EPP每次只能传送一个字节的数据,所以CPLD内部需要配置4个8位的数据寄存器,分别保存SRAM的地址和数据总线上的数据。

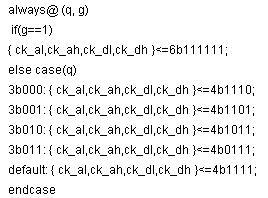

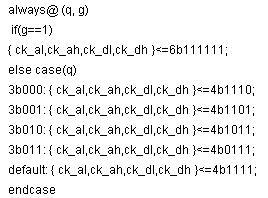

图4中的总线74LS245是一个总线收发器,由nWrite信号控制并口数据的传输方向。74LS138子模块是一个3-8译码器,通过EPP的地址线向138写入数据,使能不同的触发信号(CK)来锁存SRAM的地址或者数据总线上的高/低8位数据。该模块的Verilog核心源码如下:

由此可知,如果希望向SRAM的地址低8位写入数据,PC只需执行outp(0x378+3, 0x00),outp(0x378h+4,地址低8位值) 两条指令,在执行后一条指令的同时,ck_al选通信号将并口的数值锁存到SRAM地址低8位锁存器中。在ck_dh信号触发的同时将由nWE_cre模块使能一个nWE信号,将数据写入SRAM。

4、总结

采用增强型并口(EPP)模式,可以极大地扩展并口通讯的容量和速度。编写针对并口的WDM驱动程序,既可以保证系统运行的可靠性,也可以增加驱动程序的可移植性。使用CPLD设计并口EPP接口模块,可以最大限度的体现EPP高速传输的特性,而且由于将所有的功能模块集成在一块芯片中,提高了系统的可靠性,特别是XC95144具有的ISP(在线可编程)技术使复杂的接口电路可根据具体的应用加以修正,大大增强了接口电路的灵活性和可扩展性。本文设计的EPP接口模块已被成功的运用到某款单片机仿真器产品中,实验证明这种设计是可行的。

由上文可知,并口EPP模式下的数据传输速度可以达到μs级,所以使用一般的单片机来控制外设与EPP的通讯显然不能满足高速的要求。早期,工程师使用大量的逻辑分立元件来设计EPP的外围电路,但是当计算机的主频越来越高,EPP 模式在高速数据传输中可靠性明显下降, 因此本文采用大规模可编程逻辑器件, 充分利用其高速和大容量特性设计接口电路, 不仅可大大提高其可靠性, 且易于系统扩展和升级, 可广泛用于数据采集、D/A 转换以及数字控制。

笔者采用Xilinx公司的XC95144芯片作为EPP接口模块的控制单元,并且通过XC95144实现了计算机并口与外部存储器SRAM的数据交换。在某些外设需要数据存储和与PC机进行数据交换的应用场合得到了成功的应用。该EPP接口模块的总体框架如图4所示。

图4 EPP接口模块逻辑框图

如图4所示,CPLD内部由各个负责不同功能的子模块组成,其作用与早期的分立元件一样,所有子模块用Verilog设计实现,并且通过了仿真验证。采用ECS将所有的子模块组织起来,集成在一块CPLD内。这样做大大提高了整个系统运行的可靠性,同时也为系统扩展其他功能提供条件。

由于SRAM相对DRAM具有存储速度块,无需定时刷新,控制信号简单的优点,所以被广泛的用于需要高速数据处理的小型设备中。图4中的SRAM采用ISSI的IS61C6416,存储容量是64K×16位。地址线和数据线都是16条,但是EPP每次只能传送一个字节的数据,所以CPLD内部需要配置4个8位的数据寄存器,分别保存SRAM的地址和数据总线上的数据。

图4中的总线74LS245是一个总线收发器,由nWrite信号控制并口数据的传输方向。74LS138子模块是一个3-8译码器,通过EPP的地址线向138写入数据,使能不同的触发信号(CK)来锁存SRAM的地址或者数据总线上的高/低8位数据。该模块的Verilog核心源码如下:

由此可知,如果希望向SRAM的地址低8位写入数据,PC只需执行outp(0x378+3, 0x00),outp(0x378h+4,地址低8位值) 两条指令,在执行后一条指令的同时,ck_al选通信号将并口的数值锁存到SRAM地址低8位锁存器中。在ck_dh信号触发的同时将由nWE_cre模块使能一个nWE信号,将数据写入SRAM。

4、总结

采用增强型并口(EPP)模式,可以极大地扩展并口通讯的容量和速度。编写针对并口的WDM驱动程序,既可以保证系统运行的可靠性,也可以增加驱动程序的可移植性。使用CPLD设计并口EPP接口模块,可以最大限度的体现EPP高速传输的特性,而且由于将所有的功能模块集成在一块芯片中,提高了系统的可靠性,特别是XC95144具有的ISP(在线可编程)技术使复杂的接口电路可根据具体的应用加以修正,大大增强了接口电路的灵活性和可扩展性。本文设计的EPP接口模块已被成功的运用到某款单片机仿真器产品中,实验证明这种设计是可行的。

电路 C语言 单片机 Xilinx CPLD Verilog 仿真 总线 收发器 相关文章:

- 浅谈E1线路维护技术与应用(01-12)

- R4网络接口和电路域容灾技术(01-05)

- 移动通信网引入IMS的相关探讨(02-21)

- 未来接入网的结构与演进(01-26)

- 电子熔丝在计算机应用中的优势(06-08)

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)