如何避免ISM-RF产品中的PCB布局“缺陷”

工业、科学和医疗射频(ISM-RF)产品的无数应用案例表明,这些产品的印制板(PCB)布局很容易出现各种缺陷。人们时常发现相同IC安装到两块不同电路板上,所表现的性能指标会有显著差异。工作条件、谐波辐射、抗干扰能力,以及启动时间等等诸多因素的变化,都能说明电路板布局在一款成功设计中的重要性。

本文罗列了各种不同的设计疏忽,探讨了每种失误导致电路故障的原因,并给出了如何避免这些设计缺陷的建议。本文以FR-4电介质、厚度0.0625in的双层PCB为例,电路板底层接地。工作频率介于315MHz到915MHz之间的不同频段,Tx和Rx功率介于-120dBm至+13dBm之间。表1列出了一些可能出现的PCB布局问题、原因及其影响。

表1. 典型的PCB布局问题和影响

| Problem | Cause | Effect |

| LNA/tank circuit arrangement (receiver) | Inductor orientation | RF feedthrough |

| Degeneration/π-network arrangement (transmitter) | Inductor orientation | RF feedthrough |

| Shared ground vias between legs of πnetwork | Via parasitics | Feedthrough, RF leakage |

| Shared ground vias between receiver blocks | Via parasitics | Crosstalk, RF feedthrough, RF leakage |

| Long traces for decoupling capacitors | Higher-impedance connections | Reduced decoupling |

| Wide component placement | Increased parasitics, ground loops | Detuning, crosstalk, feedthrough |

| Colinear traces in the transmitter circuit | Filter bypassing, i.e., power amplifier (PA) directly to antenna | Harmonics radiation |

| Top-layer copper pours | Parasitic coupling | RF leakage, RF interference |

| Discontinuous ground plane | Return current concentration | Crosstalk, feedthrough |

| Crystal connection trace length | Excess capacitance | LO frequency pulling |

| Crystal connection trace separation | Excess capacitance | LO frequency pulling |

| Ground plane under crystal pads | Excess capacitance | LO frequency pulling |

| Planar PCB trace inductors | Poor inductance control | Large footprint, low Q, crosstalk, feedthrough |

其中大多数问题源于少数几个常见原因,我们将对此逐一讨论。

电感方向

当两个电感(甚至是两条PCB走线)彼此靠近时,将会产生互感。第一个电路中的电流所产生的磁场会对第二个电路中的电流产生激励(图1)。这一过程与变压器初级、次级线圈之间的相互影响类似。当两个电流通过磁场相互作用时,所产生的电压由互感LM决定:

式中,YB是向电路B注入的误差电压,IA是在电路A作用的电流1。LM对电路间距、电感环路面积(即磁通量)以及环路方向非常敏感。因此,紧凑的电路布局和降低耦合之间的最佳平衡是正确排列所有电感的方向。

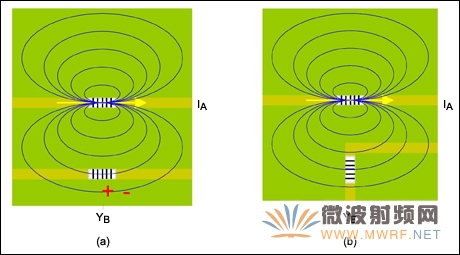

图1. 由磁力线可以看出互感与电感排列方向有关

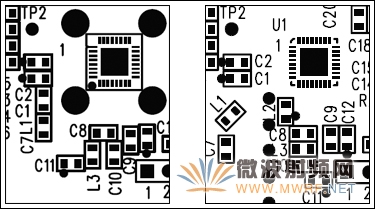

对电路B的方向进行调整,使其电流环路平行于电路A的磁力线。为达到这一目的,尽量使电感互相垂直,请参考低功率FSK超外差接收机评估(EV)板(MAX7042EVKIT)的电路布局(图2)。该电路板上的三个电感(L3、L1和L2)距离非常近,将其方向排列为0°、45°和90°,有助于降低彼此之间的互感。

图2. 图中所示为两种不同的PCB布局,其中一种布局的元件排列方向不合理(L1和L3),另一种的方向排列则更为合适。

综上所述,应遵循以下原则:

·电感间距应尽可能远。

·电感排列方向成直角,使电感之间的串扰降至最小。

引线耦合

如同电感排列方向会影响磁场耦合一样,如果引线彼此过于靠近,也会影响耦合。这种布局问题也会产生所谓的互感。RF电路最关心问题之一即为系统敏感部件的走线,例如输入匹配网络、接收器的谐振槽路、发送器的天线匹配网络等。

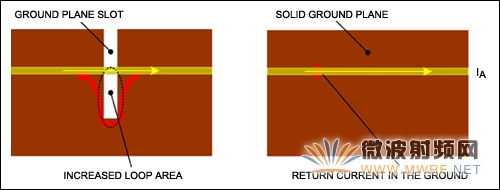

返回电流通路须尽可能靠近主电流通道,将辐射磁场降至最小。这种布局有助于减小电流环路面积。返回电流的理想低阻通路通常是引线下方的接地区域—将环路面积有效限制在电介质厚度乘以引线长度的区域。但是,如果接地区域被分割开,则会增大环路面积(图3)。对于穿过分割区域的引线,返回电流将被强制通过高阻通路,大大提高了电流环路面积。这种布局还使电路引线更容易受互感的影响。

图3. 完整的大面积接地有助于改善系统性能

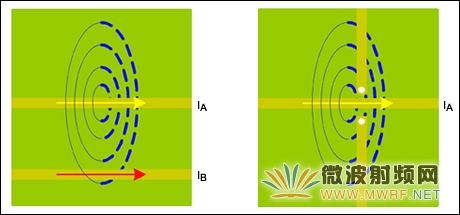

对于一个实际电感,引线方向对磁场耦合的影响也很大。如果敏感电路的引线必须彼此靠近,最好将引线方向垂直排列,以降低耦合(图4)。如果无法做到垂直排列,则可考虑使用保护线。关于保护线的设计,请参考以下接地与填充处理部分。

图4. 类似于图1,表示可能存在的磁力线耦合。

综上所述,布板时

- 直流偏移校正功能与ADS58H40 PCB布局优化(10-24)