如何避免ISM-RF产品中的PCB布局“缺陷”

.5pF。注意,LC乘积表现为集总电容。

综上所述,布板须遵循以下原则:

·保持引线长度尽可能短。

·关键电路尽量靠近器件放置。

·根据实际布局寄生效应对关键元件进行补偿。

接地与填充处理

接地或电源层定义了一个公共参考电压,通过低阻通路为系统的所有部件供电。按照这种方式均衡所有电场,产生良好的屏蔽机制。

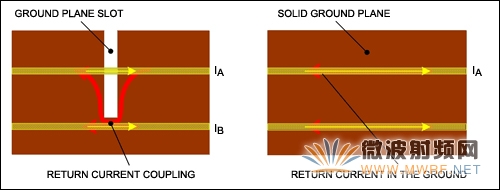

直流电流总是倾向于沿着低阻通路流通。同理,高频电流也是优先流过最低电阻的通路。所以,对于地层上方的标准PCB微带线,返回电流试图流入引线正下方的接地区域。按照上述引线耦合部分所述,割断的接地区域会引入各种噪声,进而通过磁场耦合或汇聚电流而增大串扰(图9)。

图9. 尽可能保持地层完整,否则返回电流会引起串扰。

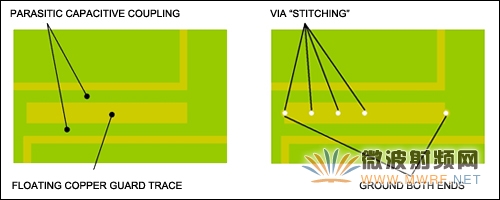

填充地也称为保护线,通常将其用于电路中很难铺设连续接地区域或需要屏蔽敏感电路的设计(图10)。通过在引线两端,或者是沿线放置接地过孔(即过孔阵列),增大屏蔽效应8。请不要将保护线与设计用来提供返回电流通路的引线相混合,这样的布局会引入串扰。

图10. RF系统设计中须避免覆铜线浮空,特别是需要铺设铜皮的情况下。

覆铜区域不接地(浮空)或仅在一端接地时,会制约其有效性。有些情况下,它会形成寄生电容,改变周围布线的阻抗或在电路之间产生"潜在"通路,从而造成不利影响。简而言之,如果在电路板上铺设了一块覆铜(非电路信号走线),来确保一致的电镀厚度。覆铜区域应避免浮空,因为它们会影响电路设计。

最后,确保考虑天线附近任何接地区域的影响。任何单极天线都将接地区域、走线和过孔作为系统均衡的一部分,非理想均衡布线会影响天线的辐射效率和方向(辐射模板)。因此,不应将接地区域直接放置在单极PCB引线天线的下方。

综上所述,应该遵循以下原则:

·尽量提供连续、低阻的接地区域。

·填充线的两端接地,并尽量采用过孔阵列。

·RF电路附近不要将覆铜线浮空,RF电路周围不要铺设铜皮。

·如果电路板包括多个地层,信号线从一侧过度另一侧时,最好铺设一个接地过孔。

晶体电容过大

寄生电容会使晶振的工作频率偏离目标值9。因此,须遵循一些常规准则,降低晶体引脚、焊盘、走线或与RF器件连接的杂散电容。

应遵循以下原则:

·晶体与RF器件之间的连线尽可能短。

·相互之间的走线尽可能保持隔离。

·如果并联寄生电容太大,则去除晶体下方的接地区域。

平面走线电感

不建议使用平面走线或PCB螺旋电感,典型PCB制造工艺具有一定的不精确性,例如宽度、空间容差,从而对元件值精度影响非常大。因此,大多数受控和高Q值电感均为绕线式。其次,可以选择多层陶瓷电感,多层片式电容厂商也提供这种产品。尽管如此,有些设计者还是在不得已的情况下选择了螺线电感。计算平面螺旋电感的标准公式通常采用惠勒公式10:

式中,a为线圈的平均半径,单位为英寸;n为匝数;c为线圈磁芯的宽度(rOUTER - rINNER),单位为英寸。当线圈的c > 0.2a时11,该计算方法的精度在5%之内。

可以使用方形、六角形或其它形状的单层螺旋电感。可以找到非常好的近似方法,对集成电路晶圆上的平面电感进行建模。为了达到这一目的,对标准惠勒公式进行修改,得到非常适合小尺寸及方形规格的平面电感估算方法12。

式中,ρ为充填比: ;n为匝数,dAVG为平均直径:

;n为匝数,dAVG为平均直径: 。对于方形螺旋,K1 = 2.36,K2 = 2.75。13

。对于方形螺旋,K1 = 2.36,K2 = 2.75。13

避免使用这种电感的原因有很多,它们通常受空间限制而导致电感值减小。避免使用平面电感的主要原因是受限制的几何尺寸,以及对临界尺寸的控制较差,从而无法预测电感值。此外,PCB生产过程中很难控制实际电感值,电感还会将噪声耦合到电路的其它部分的趋向(参见上文中的引线耦合部分)。

总而言之,应该:

·避免使用平面走线电感。

·尽量使用绕线片式电感。

总结

如上所述,几种常见的PCB布局陷阱会造成ISM-RF设计问题。然而,注意电路的非理想特性,您完全可避免这些缺陷。补偿这些不希望的影响需要适当处理表面上无关紧要的事项,例如元件方向、走线长度、过孔布置,以及接地区域的用法。遵守以上的指导原则,您可明显节省浪费在修正错误方面的时间和金钱。

参考文献

1、Johnson, Howard, and Graham, Martin, eds., High-Speed Digital Design: A Handbook of Black Magic, (Prentice Hall PTR, 1993), p. 29.

2、Ibid, p. 258.

3、Ibid, p. 247.

4、Institute for Interconnecting and Packaging Electronic Circuits or Institute for Printed Circuits.

5、IPC-2251 Design Guide for the Packaging of High Speed Electronic Circuits, High Speed/High Frequency Committee (D-20) of IPC, (November 2003).

6、Missouri University of Science and Technology's Electromagnetic Compatibility Laboratory, PCB Trace Impedance Calculator.

7、Johnson, Howard, and Graham, Martin, eds., Op Cit., p. 187.

8、Ibid, p. 201.

9、Maxim application note 1017, "How to Choose a Quartz Crystal Oscillator for the MAX1470 Superheterodyne Receiver," (March 2002), pp. 2–4.

10、Simple Inductance Formulas for Radio Coils, Harold A. Wheeler, Proceedings of the Institute of Radio Engineers, Volume 16, Number 10, (October 1928), pp. 1398–1400.

11、Missouri University of Science and Technology's Electromagnetic Compatibility Laboratory , PCB Trace Impedance Calculator.

12、IEEE® Journal of Solid-state Circuits, Volume 34, Number 10, Sunderarajan S. Mohan, Hershenson, Boyd, and Lee, (October 1999), pp. 1419–1424.

13、Ibid, p.1420.

- 直流偏移校正功能与ADS58H40 PCB布局优化(10-24)