通信集成电路芯片物理设计难点及解决方案

时间:10-11

来源:互联网

点击:

1 引言

随着半导体工艺的不断发展和通信技术的不断提高,以超大规模、高集成度和复杂性为特征的通信集成电路芯片物理设计,相比于普通的消费类产品芯片,在超深亚微米工艺下面临着更为严峻的挑战:一、工艺特征尺寸的不断缩小、电源电压的不断降低、电源噪声对芯片性能的影响日益凸显,已成为超大规模通信集成电路物理设计中一个不可忽视的问题;二、随着工艺技术的进步,高速通信集成电路芯片的时序对于芯片制造过程中产生的偏差越来越敏感,精确的电路模型及准确的时序分析方法成为制约通信集成电路芯片能否实现快速时序收敛的关键;三、通信集成电路芯片通常需要支持各种高速接口电路的应用,从而造就了独特的时钟树拓扑结构——网状时钟树,而通信芯片固有的超大规模的特性更加重了这种复杂高速时钟树优化的难度;四、随着通信技术的飞速发展、数据传输速度和容量的不断提高、信道噪声对信号质量的影响越来越大,高速串并/并串转换器(HighSpeedSerdes,HSS)的抗噪性、传输信道数量及其建模仿真的精确度成为影响通信系统设计的重要因素。本文针对这些通信芯片的物理设计难点,较为详细地介绍了IBM相应的解决方案。

2 物理设计难点分析及解决方案

针对超深亚微米工艺下超大规模通信集成电路所面临的物理设计难点,IBM提出了相应的解决方案,具体介绍如下。

2.1 电源噪声分析

目前通信集成电路的规模不断增大、工艺特征尺寸不断减小,芯片的功耗不断增加而电源电压则不断降低,电源噪声已成为超大规模集成电路设计中一个不可忽视的问题。由于大规模通信集成电路芯片通常带有各种复杂的高速接口,并在整个产品的工作过程中要求有很高的可靠性,因此芯片的电源设计起着至关重要的作用。为了保证芯片的电源完整性,在芯片的设计流程中必须对IO的同步开关噪声SSN(SimultaneousSwitchNoise)、芯片上的动态电源噪声、静态压降、ESD(Electro-StaticDischarge)静电保护以及电迁移EM(ElectroMigration)进行有效的检查和签收。

IBM在进行超大规模集成电路的设计过程中,有一套完整的流程对电源噪声进行分析(图1),能够在芯片的布局阶段尽早发现和解决芯片布局与电源设计上存在的问题,从而减少了设计反复的时间。电源噪声检查在芯片设计过程中是一个重要的签收环节,完整的设计和分析流程保证了IBM能够提供高质量的专用集成电路芯片。

图1 电源噪声分析流程

IBM的电源噪声分析流程贯穿了整个芯片设计过程,其中包含了两个噪声评审会议和一系列分析工具。在每个项目开始布局之前,噪声分析小组会和项目的物理设计工程师一起召开PINT(Post-IDRNoiseTeamReview)会议,对芯片的设计规格进行审查,找出设计中可能存在的风险,提出在芯片布局时需要注意的事项,让物理设计工程师在布局前对整个芯片的电源噪声情况有所了解,尽量避免由于电源噪声无法满足而反复修改布局。在芯片布局阶段,负责电源噪声分析的工程师会紧跟布局的变化,利用IBM的GPM(GenericPackageModel)和ALSIM(AustinLinearSimulator)系列工具及时评估芯片的电源噪声。

GPM是一个可以快速分析IO同步开关噪声的建模和分析工具。GPM针对芯片中包含IO的局部区域建立HSPICE模型,其中包含通用的封装RLC模型,芯片上的电源分配网络,IO驱动器模型和模拟一般逻辑电路翻转的等效模型。由于GPM分析不需要成熟的芯片布局,建模和仿真速度快,因此可以尽早分析IO对电源噪声的影响,为芯片的IO布局提供快速的参考,评估IO所需的电源滤波方案,避免在设计中形成电源噪声的热点。一旦芯片布局确定,GPM模型可以代表实际芯片的IO翻转情况,该模型可以交付客户,让客户联合系统的板级模型进行芯片、封装和PCB的信号完整性分析和时序分析。分析的结果可以帮助客户在芯片设计早期评估系统的性能,同步地进行PCB的设计,确定更加合理的芯片时序约束。

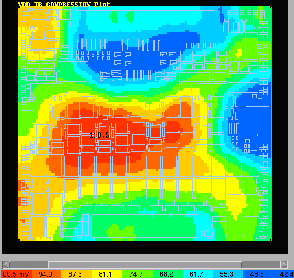

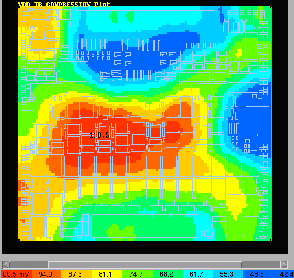

ALSIM_TA(TransientAnalysis)是一个高效的全芯片动态电源噪声仿真分析工具。仿真过程中使用了芯片的封装模型,片上电源网络模型和代表各种逻辑电路翻转的电流波形。通过ALSIM_TA仿真可以得到整个芯片电源噪声峰峰值,动态压降等信息在芯片上的分布情况,并以二维图形直观地显示,如图2所示。ALSIM_TA的结果可以直观地评估芯片的布局和电源滤波方案对电源噪声的影响。

图2 ALSIM_TA仿真结果

根据早期的ALSIM_TA和GPM分析结果,物理设计工程师可以尽早优化芯片布局,通过增加噪声源和噪声敏感的器件之间的距离,增加片上去耦电容等方式获得较好的噪声性能。

在芯片布局最终确定之前,噪声分析小组会和物理设计工程师召开NTFR(NoiseTeamFloorplanReview)会议,再次对芯片的布局和电源滤波方案进行评审,对高速接口的相关问题进行讨论,检查芯片是否可以满足电源噪声签收的标准并提出建议和进一步的分析、优化方案。

除了利用GPM和ALSIM_TA对电源动态噪声进行分析,IBM还使用ALSIM_ETIR对全芯片的静态电源压降进行分析。在每个设计阶段,ALSIM_ETIR会提取每个电路上的压降并反标到时序分析工具中从而得到更真实的静态时序分析结果。在每个设计的签收阶段,ALSIM_PGA和ALSIM_ESD是对EM和ESD进行检查和签收的工具,而GPM则是动态电源噪声的签收工具。通过在每个设计阶段对芯片的电源噪声进行完备的检查,IBM可以设计出具有高可靠性的大规模通信集成电路芯片,保证一次设计成功率。

随着半导体工艺的不断发展和通信技术的不断提高,以超大规模、高集成度和复杂性为特征的通信集成电路芯片物理设计,相比于普通的消费类产品芯片,在超深亚微米工艺下面临着更为严峻的挑战:一、工艺特征尺寸的不断缩小、电源电压的不断降低、电源噪声对芯片性能的影响日益凸显,已成为超大规模通信集成电路物理设计中一个不可忽视的问题;二、随着工艺技术的进步,高速通信集成电路芯片的时序对于芯片制造过程中产生的偏差越来越敏感,精确的电路模型及准确的时序分析方法成为制约通信集成电路芯片能否实现快速时序收敛的关键;三、通信集成电路芯片通常需要支持各种高速接口电路的应用,从而造就了独特的时钟树拓扑结构——网状时钟树,而通信芯片固有的超大规模的特性更加重了这种复杂高速时钟树优化的难度;四、随着通信技术的飞速发展、数据传输速度和容量的不断提高、信道噪声对信号质量的影响越来越大,高速串并/并串转换器(HighSpeedSerdes,HSS)的抗噪性、传输信道数量及其建模仿真的精确度成为影响通信系统设计的重要因素。本文针对这些通信芯片的物理设计难点,较为详细地介绍了IBM相应的解决方案。

2 物理设计难点分析及解决方案

针对超深亚微米工艺下超大规模通信集成电路所面临的物理设计难点,IBM提出了相应的解决方案,具体介绍如下。

2.1 电源噪声分析

目前通信集成电路的规模不断增大、工艺特征尺寸不断减小,芯片的功耗不断增加而电源电压则不断降低,电源噪声已成为超大规模集成电路设计中一个不可忽视的问题。由于大规模通信集成电路芯片通常带有各种复杂的高速接口,并在整个产品的工作过程中要求有很高的可靠性,因此芯片的电源设计起着至关重要的作用。为了保证芯片的电源完整性,在芯片的设计流程中必须对IO的同步开关噪声SSN(SimultaneousSwitchNoise)、芯片上的动态电源噪声、静态压降、ESD(Electro-StaticDischarge)静电保护以及电迁移EM(ElectroMigration)进行有效的检查和签收。

IBM在进行超大规模集成电路的设计过程中,有一套完整的流程对电源噪声进行分析(图1),能够在芯片的布局阶段尽早发现和解决芯片布局与电源设计上存在的问题,从而减少了设计反复的时间。电源噪声检查在芯片设计过程中是一个重要的签收环节,完整的设计和分析流程保证了IBM能够提供高质量的专用集成电路芯片。

图1 电源噪声分析流程

IBM的电源噪声分析流程贯穿了整个芯片设计过程,其中包含了两个噪声评审会议和一系列分析工具。在每个项目开始布局之前,噪声分析小组会和项目的物理设计工程师一起召开PINT(Post-IDRNoiseTeamReview)会议,对芯片的设计规格进行审查,找出设计中可能存在的风险,提出在芯片布局时需要注意的事项,让物理设计工程师在布局前对整个芯片的电源噪声情况有所了解,尽量避免由于电源噪声无法满足而反复修改布局。在芯片布局阶段,负责电源噪声分析的工程师会紧跟布局的变化,利用IBM的GPM(GenericPackageModel)和ALSIM(AustinLinearSimulator)系列工具及时评估芯片的电源噪声。

GPM是一个可以快速分析IO同步开关噪声的建模和分析工具。GPM针对芯片中包含IO的局部区域建立HSPICE模型,其中包含通用的封装RLC模型,芯片上的电源分配网络,IO驱动器模型和模拟一般逻辑电路翻转的等效模型。由于GPM分析不需要成熟的芯片布局,建模和仿真速度快,因此可以尽早分析IO对电源噪声的影响,为芯片的IO布局提供快速的参考,评估IO所需的电源滤波方案,避免在设计中形成电源噪声的热点。一旦芯片布局确定,GPM模型可以代表实际芯片的IO翻转情况,该模型可以交付客户,让客户联合系统的板级模型进行芯片、封装和PCB的信号完整性分析和时序分析。分析的结果可以帮助客户在芯片设计早期评估系统的性能,同步地进行PCB的设计,确定更加合理的芯片时序约束。

ALSIM_TA(TransientAnalysis)是一个高效的全芯片动态电源噪声仿真分析工具。仿真过程中使用了芯片的封装模型,片上电源网络模型和代表各种逻辑电路翻转的电流波形。通过ALSIM_TA仿真可以得到整个芯片电源噪声峰峰值,动态压降等信息在芯片上的分布情况,并以二维图形直观地显示,如图2所示。ALSIM_TA的结果可以直观地评估芯片的布局和电源滤波方案对电源噪声的影响。

图2 ALSIM_TA仿真结果

根据早期的ALSIM_TA和GPM分析结果,物理设计工程师可以尽早优化芯片布局,通过增加噪声源和噪声敏感的器件之间的距离,增加片上去耦电容等方式获得较好的噪声性能。

在芯片布局最终确定之前,噪声分析小组会和物理设计工程师召开NTFR(NoiseTeamFloorplanReview)会议,再次对芯片的布局和电源滤波方案进行评审,对高速接口的相关问题进行讨论,检查芯片是否可以满足电源噪声签收的标准并提出建议和进一步的分析、优化方案。

除了利用GPM和ALSIM_TA对电源动态噪声进行分析,IBM还使用ALSIM_ETIR对全芯片的静态电源压降进行分析。在每个设计阶段,ALSIM_ETIR会提取每个电路上的压降并反标到时序分析工具中从而得到更真实的静态时序分析结果。在每个设计的签收阶段,ALSIM_PGA和ALSIM_ESD是对EM和ESD进行检查和签收的工具,而GPM则是动态电源噪声的签收工具。通过在每个设计阶段对芯片的电源噪声进行完备的检查,IBM可以设计出具有高可靠性的大规模通信集成电路芯片,保证一次设计成功率。

半导体 集成电路 电压 电路 仿真 Linear PIC PCB 电流 电容 滤波器 相关文章:

- 铁电存储器工作原理和器件结构(05-22)

- 电子熔丝在计算机应用中的优势(06-08)

- 卓联 Marvell?联手展示网络同步Ethernet解决方案(01-07)

- 恩智浦半导体发布USB收发器(02-23)

- 安森美扩充电源计算产品系列 推出新双缘多相控制器(03-13)

- ST推出测试65nm多标准硬盘驱动器物理层IP模块(04-08)