通信集成电路芯片物理设计难点及解决方案

时间:10-11

来源:互联网

点击:

2.2 统计静态时序分析(SSTA)

随着工艺技术的进步,芯片制造过程中产生的偏差成为影响芯片性能的重要因素,必须在芯片设计的阶段就考虑这个问题。传统的静态时序分析(StaticTimingAnalysis,STA)方法,建立在以工艺角为基础的器件时序模型上。然而随着工艺技术的进步,反映偏差的参数迅速增加,不仅包括晶片内或晶片间的偏差,还包括各种片上偏差(On-ChipVariation,OCV),例如芯片不同位置上沟道长度、阈值电压、金属层厚度等,这导致工艺角的数目和时序分析的时间呈指数增长。除此之外,STA的另一大缺陷是预测的时序过于悲观,因为器件工作在每个参数的最坏情况下的机率是很低的,这导致设计的时序过于保守,从而增加了设计难度和时间。因此,我们需要建立一个更完备的模型以反映各种工艺偏差对时序的影响,并在有限的时间内,更准确地进行时序分析。

IBM很早就开始对统计静态时序分析方法(StatisticalStaticTimingAnalysis,SSTA)进行研究,并已取代STA应用于65nm、45nm工艺中。SSTA是利用统计的方式去描述制造工艺中的偏差,采用的模型描述的是各个偏差的概率分布曲线。

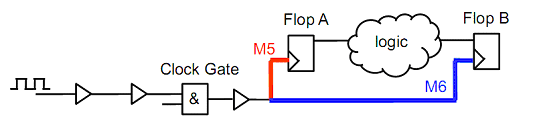

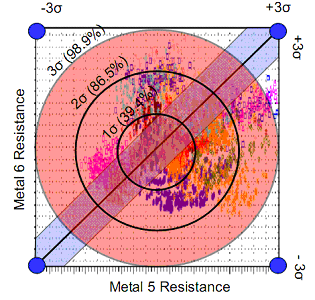

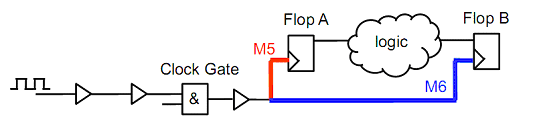

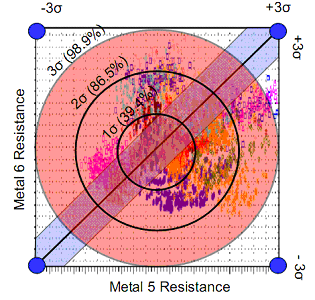

下面我们举例说明SSTA与STA的不同。如图3所示,寄存器A和寄存器B的时钟端接在同一个门控时钟源,但分别在M5和M6金属层上布线。传统的STA没有考虑不同金属层之间由于CMP工艺造成的偏差,因此假设两条路径工作在相同的工艺角下,导致实际的时钟偏移(Skew)大于估计的结果,电路可能无法正常工作。图4描述了M5和M6金属层阻抗偏差的分布,实际电路可能工作在整个坐标平面内的任意一个点。PrimeTime中通过引入比例因子(DeratingFactor)来解决类似的工艺偏差,两个参数的偏差遵循线性关系,所覆盖的范围为图4中条状区域,比例因子的值决定了所覆盖区域的大小。SSTA是基于各个偏差的概率分布曲线,得到联合概率分布曲线,采用3σ分析方法,覆盖区域所占比例高达98.9%。

图3 金属层制造偏差引起的时钟偏移

图4 不同时序分析方法对工艺偏差的覆盖率

SSTA不以slack作为时序检查的依据,而是预测电路性能对工艺偏差的敏感程度,作为评价设计可靠性的指标。SSTA可以分析出芯片上每个部分能工作在多高的时钟频率下,并为测试方案的设计提供依据。SSTA的基础是建立可靠的模型来反映工艺偏差的概率分布,IBM已经将SSTA应用于自主研发的时序分析工具Einstimer中,并从65nm工艺开始,作为Sign-off的必要条件。同时,IBM还将SSTA的理念应用于布局布线,信号完整性分析等工具中,从统计学的角度对电路进行优化,使设计更符合DFM的要求。

2.3 时钟树优化

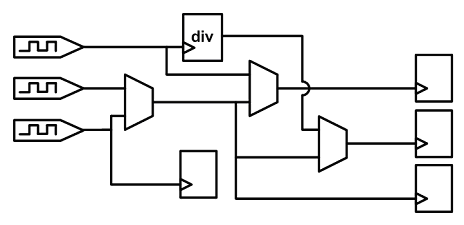

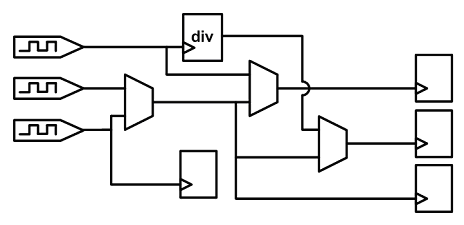

通信集成电路通常需要支持各种应用,如HSS、SRAM、DDR、TCAM等;而这些接口电路一般都工作在不同的时钟域下。为了实现各接口电路之间高速的数据传输,往往需要一些计算/控制逻辑电路能够可配置地工作在不同的时钟域。这样就形成了通信领域集成电路芯片独特的时钟树拓扑结构——网状时钟树。如图5所示,多个异步时钟源从PLL、HSS或者IO引入芯片内部,经过几级选通器或分频器,最终到达每个时序器件的时钟端。时钟结构相同的一组逻辑电路,可以在不同的时段采用不同的时钟频率;而时钟结构不同的逻辑电路,经过配置,可以工作在同一时钟域下,进行同步信号传输,满足特殊的通信需求。因此,在建立和优化时钟树时,需要对芯片上各个时钟的到达时间进行一个整体的约束,使可能工作在同一时钟域下的逻辑电路的时钟信号到达时间尽量保持一致,从而保证时序电路正常工作。

图5 网状时钟树结构

IBM常用的时钟树优化机制主要由描述时钟树结构的CDOC(ClockDesignerOptimizationControlFile)文件和时钟树优化工具BCO两部分组成。基本工作原理为:首先通过CDOC文件确定需要优化的时钟树——CDOC文件描述了各条时钟树的起始点和一个停止点,从起始点开始向后追溯,直到所有分支都遇到停止点为止;其间穿过的结构,就是需要优化的时钟树;然后BCO根据CDOC文件所描述的时钟树结构,按前后顺序依次优化——在优化每一条时钟树段落时,BCO会按照由叶至根的顺序,插入一系列缓冲器或者反向器,使得各个叶节点的时钟到达时间偏差和整个时钟树延迟都尽量小,BCO还会对时钟树穿过的组合逻辑结构进行复制,放在各个叶节点附近,从而满足优化前后逻辑功能的一致性。

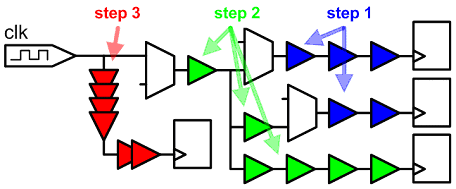

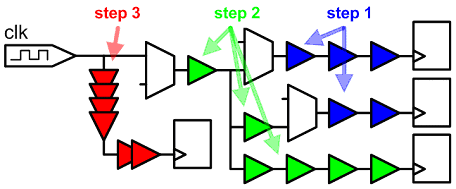

针对通信芯片相对复杂的时钟树结构,BCO在原有机制的基础上提供了一种逐级优化时钟树的方法:如图6所示,首先将整个时钟网络以选通器或分频器为节点分段,按照时钟信号的流向,靠近时钟源的为父时钟树,反之为子时钟树。然后从最末端的子时钟树开始进行优化,并将优化后的延时信息标记在子时钟树的根节点上;优化父时钟树时,根据其所有子时钟树的延迟信息,采用时钟偏差技术(PlannedSkewScheduling),使得其下所有时序器件(包括它的子时钟树)的时钟信号到达时间相同;以此向前递归,直到时钟源;从而实现了整个时钟网络优化。

图6 网状时钟树优化方法

随着工艺技术的进步,芯片制造过程中产生的偏差成为影响芯片性能的重要因素,必须在芯片设计的阶段就考虑这个问题。传统的静态时序分析(StaticTimingAnalysis,STA)方法,建立在以工艺角为基础的器件时序模型上。然而随着工艺技术的进步,反映偏差的参数迅速增加,不仅包括晶片内或晶片间的偏差,还包括各种片上偏差(On-ChipVariation,OCV),例如芯片不同位置上沟道长度、阈值电压、金属层厚度等,这导致工艺角的数目和时序分析的时间呈指数增长。除此之外,STA的另一大缺陷是预测的时序过于悲观,因为器件工作在每个参数的最坏情况下的机率是很低的,这导致设计的时序过于保守,从而增加了设计难度和时间。因此,我们需要建立一个更完备的模型以反映各种工艺偏差对时序的影响,并在有限的时间内,更准确地进行时序分析。

IBM很早就开始对统计静态时序分析方法(StatisticalStaticTimingAnalysis,SSTA)进行研究,并已取代STA应用于65nm、45nm工艺中。SSTA是利用统计的方式去描述制造工艺中的偏差,采用的模型描述的是各个偏差的概率分布曲线。

下面我们举例说明SSTA与STA的不同。如图3所示,寄存器A和寄存器B的时钟端接在同一个门控时钟源,但分别在M5和M6金属层上布线。传统的STA没有考虑不同金属层之间由于CMP工艺造成的偏差,因此假设两条路径工作在相同的工艺角下,导致实际的时钟偏移(Skew)大于估计的结果,电路可能无法正常工作。图4描述了M5和M6金属层阻抗偏差的分布,实际电路可能工作在整个坐标平面内的任意一个点。PrimeTime中通过引入比例因子(DeratingFactor)来解决类似的工艺偏差,两个参数的偏差遵循线性关系,所覆盖的范围为图4中条状区域,比例因子的值决定了所覆盖区域的大小。SSTA是基于各个偏差的概率分布曲线,得到联合概率分布曲线,采用3σ分析方法,覆盖区域所占比例高达98.9%。

图3 金属层制造偏差引起的时钟偏移

图4 不同时序分析方法对工艺偏差的覆盖率

SSTA不以slack作为时序检查的依据,而是预测电路性能对工艺偏差的敏感程度,作为评价设计可靠性的指标。SSTA可以分析出芯片上每个部分能工作在多高的时钟频率下,并为测试方案的设计提供依据。SSTA的基础是建立可靠的模型来反映工艺偏差的概率分布,IBM已经将SSTA应用于自主研发的时序分析工具Einstimer中,并从65nm工艺开始,作为Sign-off的必要条件。同时,IBM还将SSTA的理念应用于布局布线,信号完整性分析等工具中,从统计学的角度对电路进行优化,使设计更符合DFM的要求。

2.3 时钟树优化

通信集成电路通常需要支持各种应用,如HSS、SRAM、DDR、TCAM等;而这些接口电路一般都工作在不同的时钟域下。为了实现各接口电路之间高速的数据传输,往往需要一些计算/控制逻辑电路能够可配置地工作在不同的时钟域。这样就形成了通信领域集成电路芯片独特的时钟树拓扑结构——网状时钟树。如图5所示,多个异步时钟源从PLL、HSS或者IO引入芯片内部,经过几级选通器或分频器,最终到达每个时序器件的时钟端。时钟结构相同的一组逻辑电路,可以在不同的时段采用不同的时钟频率;而时钟结构不同的逻辑电路,经过配置,可以工作在同一时钟域下,进行同步信号传输,满足特殊的通信需求。因此,在建立和优化时钟树时,需要对芯片上各个时钟的到达时间进行一个整体的约束,使可能工作在同一时钟域下的逻辑电路的时钟信号到达时间尽量保持一致,从而保证时序电路正常工作。

图5 网状时钟树结构

IBM常用的时钟树优化机制主要由描述时钟树结构的CDOC(ClockDesignerOptimizationControlFile)文件和时钟树优化工具BCO两部分组成。基本工作原理为:首先通过CDOC文件确定需要优化的时钟树——CDOC文件描述了各条时钟树的起始点和一个停止点,从起始点开始向后追溯,直到所有分支都遇到停止点为止;其间穿过的结构,就是需要优化的时钟树;然后BCO根据CDOC文件所描述的时钟树结构,按前后顺序依次优化——在优化每一条时钟树段落时,BCO会按照由叶至根的顺序,插入一系列缓冲器或者反向器,使得各个叶节点的时钟到达时间偏差和整个时钟树延迟都尽量小,BCO还会对时钟树穿过的组合逻辑结构进行复制,放在各个叶节点附近,从而满足优化前后逻辑功能的一致性。

针对通信芯片相对复杂的时钟树结构,BCO在原有机制的基础上提供了一种逐级优化时钟树的方法:如图6所示,首先将整个时钟网络以选通器或分频器为节点分段,按照时钟信号的流向,靠近时钟源的为父时钟树,反之为子时钟树。然后从最末端的子时钟树开始进行优化,并将优化后的延时信息标记在子时钟树的根节点上;优化父时钟树时,根据其所有子时钟树的延迟信息,采用时钟偏差技术(PlannedSkewScheduling),使得其下所有时序器件(包括它的子时钟树)的时钟信号到达时间相同;以此向前递归,直到时钟源;从而实现了整个时钟网络优化。

图6 网状时钟树优化方法

半导体 集成电路 电压 电路 仿真 Linear PIC PCB 电流 电容 滤波器 相关文章:

- 铁电存储器工作原理和器件结构(05-22)

- 电子熔丝在计算机应用中的优势(06-08)

- 卓联 Marvell?联手展示网络同步Ethernet解决方案(01-07)

- 恩智浦半导体发布USB收发器(02-23)

- 安森美扩充电源计算产品系列 推出新双缘多相控制器(03-13)

- ST推出测试65nm多标准硬盘驱动器物理层IP模块(04-08)