Nios系统基础上的Ultra DMA数据传输模式

时间:09-21

来源:互联网

点击:

随着消费类电子,如MP3、3G手机、视频终端以及宽带无线网络的普及,对大容量存储设备的需求越来越强烈。传统的SRAM、SDRAM以及DDR SDRAM等存储设备的价格与容量比,远远比硬盘高;光存储设备虽然更加廉价,但是在便携性上却远逊于硬盘解决方案。现在硬盘厂商提供了各种适用于不同用途的廉价海量存储设备,如1 in(英寸)的微硬盘可以应用于各种小巧的便携设备中,2.5in硬盘可以应用于笔记本和移动存储中,3.5in硬盘可以应用于个人PC和工业自动化中等等。

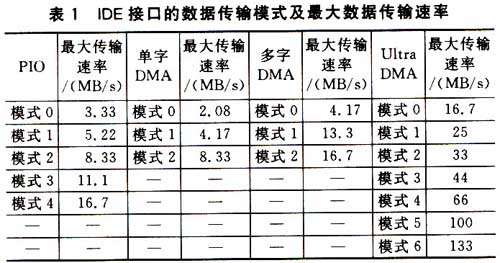

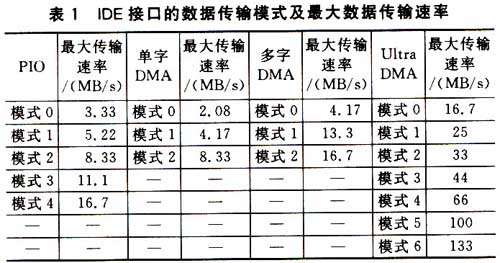

目前,硬盘支持的最为广泛的IDE接口协议中,规定了PIO、DMA以及Ultra DMA三种数据传输模式,其传输速率PIO<多字DMA<Ultra DMA,如表1所列。随着各种多媒体应用的广泛普及,各种设备不但要求拥有海量存储能力,在完成各种实时业务时对数据的传输速率也提出了严格的要求。

现阶段的设计研究主要集中于单边沿锁存数据的PIO和DMA传输模式。大多数设计主要用PIO模式完成控制命令的写入和读取操作,采用DMA数据传输模式进行直接内存读取操作,提高数据传输的速率。如果在相同系统中使用Ultra DMA数据传输模式,则可以在不提高系统时钟频率的基础上,将系统数据传输速率提高l倍,极大地改善了系统性能,而不需要付出更多的硬件资源。因而硬盘的Ultra DMA数据传输方式在工业自动化、Internet网络、消费类电子和各种嵌入式系统中的需求会不断增加,有着很好的商业前景。

1 Nios系统介绍

该设计是在Altera公司推出的Nios嵌入式系统的平台上,设计可以通过Ultra DMA数据传输方式进行高速硬盘读写的接口模块,并开发出相应的IP核。

1.1 Nios系统结构

Nios嵌入式处理器系统通常由N1os处理器、Avalon交换结构总线和各种外围设备(存储、接口及功能模块)的IP核三部分构成。Altera的SOPC Builder系统开发工具可以自动生成这些组件以及连接它们的总线。

Nios处理器是32位结构可配置并包含五级流水线的通用RISC微处理器,采用改进的哈佛存储器结构;处理器带有分离的数据和程序存储器总线控制,具备高速缓存、中断处理功能。与传统处理器相比,Nios指令系统可通过自定义指令和标准处理器选项,利用硬件来明显提高系统性能。

Avalon交换结构总线是Altera开发的用于Nios嵌入式处理器的参数化接口总线,由l组预定义的信号组成,用这些信号可以连接1个或多个IP模块。Altera的S0PC Builder系统开发工具自动地产生Avalon交换结构总线逻辑,其实现只需要极少的FPGA资源,提供完全同步的操作。

Nios嵌入式处理器系统中的各种存储模块、接口模块和功能模块等都在Altera的标准外围设备库中以IP核的方式提供使用,或是由用户自行设计添加到库中,以IP模块的方式在系统中复用。

实现硬盘高速访问功能模块的设计,实际上是在设计一个完整的IP模块,再在Altera提供的SOPC Builder开发环境的设备库中集成该IP核,以达到设计的目的。

1.2采用Nlos软核处理器构建系统的原因

①与其他的实现方式相比有着更好的性能价格比。最常见的硬盘读取控制和数据传输方式是通过单片机或是DSP来实现的,使用单片机或DSP中的PIO接口可以很方便地完成单边沿锁存数据的硬盘PIO和DMA数据传输方式,但在实现双边沿锁存数据的Ultra DMA传输方式时,必须在单片机和DSP芯片外添加额外的FPGA芯片,完成Ultra DMA双边沿锁存数据到单边沿锁存数据的转换,增加了系统设计的成本和复杂性。而采用Nios软核处理器完成与硬盘的Ultra DMA传输方式时,不需要添加任何额外的芯片,仅使用FPGA内的其他资源就可以方便地实现双边沿到单边沿的转换工作。

②与传统的单片机或DSP实现方式相比,Nios嵌入式系统的设计与实现更加简单。从性能上来说,Nios软核处理器与ARM、Intel等的CPU处于同一级别,都能够满足设计的需要,即使是复杂逻辑系统的设计也可以在一片Cyclone或是StratiX芯片上实现全部功能。而且通过使用Altera公司提供的SOPC Builder开发工具,在IP复用的基础上可以快速开发出完整的系统解决方案。

③与传统的单片机或DSP实现方式相比,Nios嵌入式系统的可扩展性更好。单片机或DSP内的资源是硬件厂商固化在芯片内的,用户不可能自行添加或删减,在设计时的灵活性受到器件本身的限制;而Nios软核处理器的所有资源都可以任意地添加或删减,只需最终通过电缆下载到FPGA芯片内就可定制出整个系统的功能。因而在基于Nios的系统设计中,通过对设计文件的修改就可以很方便地进行系统功能的扩展。

目前,硬盘支持的最为广泛的IDE接口协议中,规定了PIO、DMA以及Ultra DMA三种数据传输模式,其传输速率PIO<多字DMA<Ultra DMA,如表1所列。随着各种多媒体应用的广泛普及,各种设备不但要求拥有海量存储能力,在完成各种实时业务时对数据的传输速率也提出了严格的要求。

现阶段的设计研究主要集中于单边沿锁存数据的PIO和DMA传输模式。大多数设计主要用PIO模式完成控制命令的写入和读取操作,采用DMA数据传输模式进行直接内存读取操作,提高数据传输的速率。如果在相同系统中使用Ultra DMA数据传输模式,则可以在不提高系统时钟频率的基础上,将系统数据传输速率提高l倍,极大地改善了系统性能,而不需要付出更多的硬件资源。因而硬盘的Ultra DMA数据传输方式在工业自动化、Internet网络、消费类电子和各种嵌入式系统中的需求会不断增加,有着很好的商业前景。

1 Nios系统介绍

该设计是在Altera公司推出的Nios嵌入式系统的平台上,设计可以通过Ultra DMA数据传输方式进行高速硬盘读写的接口模块,并开发出相应的IP核。

1.1 Nios系统结构

Nios嵌入式处理器系统通常由N1os处理器、Avalon交换结构总线和各种外围设备(存储、接口及功能模块)的IP核三部分构成。Altera的SOPC Builder系统开发工具可以自动生成这些组件以及连接它们的总线。

Nios处理器是32位结构可配置并包含五级流水线的通用RISC微处理器,采用改进的哈佛存储器结构;处理器带有分离的数据和程序存储器总线控制,具备高速缓存、中断处理功能。与传统处理器相比,Nios指令系统可通过自定义指令和标准处理器选项,利用硬件来明显提高系统性能。

Avalon交换结构总线是Altera开发的用于Nios嵌入式处理器的参数化接口总线,由l组预定义的信号组成,用这些信号可以连接1个或多个IP模块。Altera的S0PC Builder系统开发工具自动地产生Avalon交换结构总线逻辑,其实现只需要极少的FPGA资源,提供完全同步的操作。

Nios嵌入式处理器系统中的各种存储模块、接口模块和功能模块等都在Altera的标准外围设备库中以IP核的方式提供使用,或是由用户自行设计添加到库中,以IP模块的方式在系统中复用。

实现硬盘高速访问功能模块的设计,实际上是在设计一个完整的IP模块,再在Altera提供的SOPC Builder开发环境的设备库中集成该IP核,以达到设计的目的。

1.2采用Nlos软核处理器构建系统的原因

①与其他的实现方式相比有着更好的性能价格比。最常见的硬盘读取控制和数据传输方式是通过单片机或是DSP来实现的,使用单片机或DSP中的PIO接口可以很方便地完成单边沿锁存数据的硬盘PIO和DMA数据传输方式,但在实现双边沿锁存数据的Ultra DMA传输方式时,必须在单片机和DSP芯片外添加额外的FPGA芯片,完成Ultra DMA双边沿锁存数据到单边沿锁存数据的转换,增加了系统设计的成本和复杂性。而采用Nios软核处理器完成与硬盘的Ultra DMA传输方式时,不需要添加任何额外的芯片,仅使用FPGA内的其他资源就可以方便地实现双边沿到单边沿的转换工作。

②与传统的单片机或DSP实现方式相比,Nios嵌入式系统的设计与实现更加简单。从性能上来说,Nios软核处理器与ARM、Intel等的CPU处于同一级别,都能够满足设计的需要,即使是复杂逻辑系统的设计也可以在一片Cyclone或是StratiX芯片上实现全部功能。而且通过使用Altera公司提供的SOPC Builder开发工具,在IP复用的基础上可以快速开发出完整的系统解决方案。

③与传统的单片机或DSP实现方式相比,Nios嵌入式系统的可扩展性更好。单片机或DSP内的资源是硬件厂商固化在芯片内的,用户不可能自行添加或删减,在设计时的灵活性受到器件本身的限制;而Nios软核处理器的所有资源都可以任意地添加或删减,只需最终通过电缆下载到FPGA芯片内就可定制出整个系统的功能。因而在基于Nios的系统设计中,通过对设计文件的修改就可以很方便地进行系统功能的扩展。

电子 自动化 嵌入式 Altera 总线 FPGA 单片机 DSP ARM 电路 C语言 Quartus 仿真 相关文章:

- 变革电信网网络安全框架 (01-03)

- 浅谈IPv6技术的若干问题(01-09)

- LG电子低成本CDMA手机的设计原则剖析 (01-12)

- 专家教你做个病毒高手(04-30)

- 数据库归档要考虑的四大问题(05-26)

- 5个步骤成功加密电子邮件(07-18)