基于LEON开源软核的SoC平台构建与测试

时间:09-15

来源:互联网

点击:

伴随着导航系统功能日益多样化、软件算法愈加复杂和集成度要求更高的趋势,在大规模可编程器件上设计、验证和测试导航SoC芯片成为解决方案之一。导航系统SoC芯片设计的要求主要有:

①安全性。芯片的所有功能模块运行正常,运行机制透明,可靠性强。

②可配置性。根据应用要求对硬件进行裁减和配置,达到最佳的功能、功耗和面积比。

③高运算能力。具备在特定时间内完成复杂算法的运算能力。

SoC芯片的核心是实现运算和控制功能的微处理器。LEON是一款基于SPARC V8架构的开源微处理器IP软核,在VHDL源代码基础上,结合具体需求加入定制的运算单元和外设接口建立SoC系统。在配置灵活的LEON核上运行Embedded Linux,提供SoC调试和测试的基本平台。

1 软硬件平台构建

1.1 LEON软核架构简介

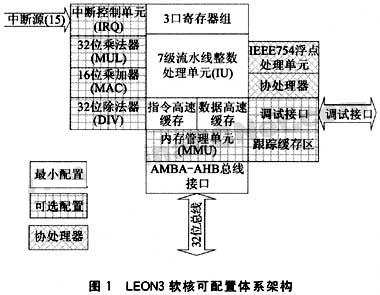

LEON核心是一个与SPARCV8兼容的整数处理单元IU(Integer Unit),LEON2是5级流水线,LEON3是7级流水线。LEON包含整数硬件乘法和除法单元、双协处理器接口(FPU浮点处理单元和Co-processor协处理器),分离的指令和数据总线(Harvard结构)。LEON通过高速的AMBA-AHB总线,指令缓存和数据缓存分别和内存控制器及高速的外部接口相连传输数据。低速的AMBA-APB总线实现片上外设的接口,例如定时器、串口、网络接口等。LEON3软核可配置体系架构如图1所示。

1.2 LEON在SoC芯片开发应用中的优势

LEON软核最突出的优势是其良好的可配置性和可移植性,以及遵循GPL许可证协议的开源性。这些特性保证导航系统SoC芯片的安全性,提供良好的性能和灵活的解决方案,也决定了在LEON上进行嵌入式操作系统移植的特殊性。

1.2.1 开源性

基于GPL许可证协议,LEON非容错版本软核IP提供VHDL源代码,仅是容错版本的LEON软核需要商业授权。源代码公开是实现导航系统SoC芯片设计安全性的前提,同时也使研究者和开发者从根本上研究软核的细节从而定制满足具体应用的软核成为可能。与全部源代码开放的LEON相比,Altera的NIOS软核等其他软核仅提供若干接口,无法在更深的软核层次上进行设计和优化。

1.2.2 优异的可配置性

LEON软核通过集成一套丰富的接口和运算单元IP库,根据具体要求来达到性能、功耗和面积的平衡和优化的目的。

①软核IU可配置参数包括流水线的深度、地址和数据高速缓存(Cache)。另外,常用指令及指令序列可以根据定制的硬件进行优化;在设计或配置新运算单元后能够对指令集进行扩展。在导航系统SoC芯片设计中,通过配置LEON的整数硬件乘除法单元以实现较高的运算性能;而在其他某些使用软件乘除法,即满足要求的应用中无需配置,以降低功耗和优化芯片面积。

②外围设备接口硬件通过挂载AMBA总线来实现。LEON3的AMBA-AHP总线上能够灵活选择集成opencores的以太网控制器和GRETH以太网控制器中的任意一个。针对导航系统中常见的1553总线接口设备,在LEON中通过配置GR1553单元完成1553总线到AMBA-AHB总线的转换,为1553总线设备的集成提供了方便。

③硬件加速单元(如特定加密算法、数字信号处理单元和浮点处理单元)根据需求集成。

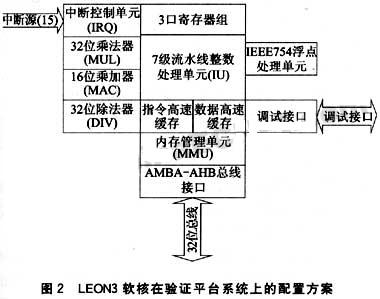

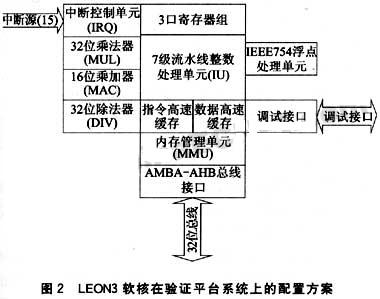

优异的可配置性带来了硬件设计极大的灵活性,也为嵌入式操作系统的移植带来了一定难度(特别是在扩展了指令集的情况下)。考虑到进行性能测试的完整性和灵活性,LEON3软核在本项目中的配置方案如图2所示。(详细配置参数未列出)

1.2.3良好的可移植性

LEON软核通过层次度分明的VHDL模型实现。通过VHDL中特定的配置接口,LEON核的关键参数(例如修改Cache的大小和组织方式,乘法器的生成,速度、芯片面积的调整以及容错方案的选择)都能够灵活设置和移植;而唯一使用专用技术的模型是内存宏模块。这一部分的设计采用了加上中间交互层接口的方式,因此移植的工作仅需重新编写中间交互层接口。导航系统中包括单次滤波在内的大量算法经过硬件实现后需集成在LEON中,根据LEON特定的配置接口即可实现集成和SoC系统移植。在本硬件平台的设计中,针对特定硬件开发板,通过修改顶层module文件设置以及更新引脚配置,即可完成硬件设计的移植工作。

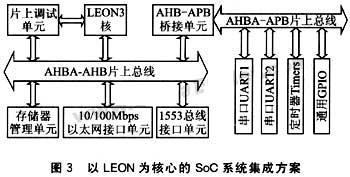

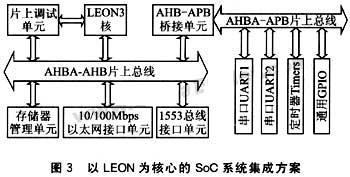

目前,LEON在研究领域被广泛应用,特别是作为软核嵌入在可编程器件中,作为构建SoC芯片的控制和运算中心。LEON软核的容错版本也已经用在了空间站上。在本导航系统SoC芯片项目中,选择了开源且配置灵活的LEON硬件平台和Linux软件平台,并且在初期测试中表现出良好的性能。在本验证平台上,SoC系统需要以太网接口、1553总线接口、串口、通用I/O口以及调试单元,具体配置方案如图3所示。

①安全性。芯片的所有功能模块运行正常,运行机制透明,可靠性强。

②可配置性。根据应用要求对硬件进行裁减和配置,达到最佳的功能、功耗和面积比。

③高运算能力。具备在特定时间内完成复杂算法的运算能力。

SoC芯片的核心是实现运算和控制功能的微处理器。LEON是一款基于SPARC V8架构的开源微处理器IP软核,在VHDL源代码基础上,结合具体需求加入定制的运算单元和外设接口建立SoC系统。在配置灵活的LEON核上运行Embedded Linux,提供SoC调试和测试的基本平台。

1 软硬件平台构建

1.1 LEON软核架构简介

LEON核心是一个与SPARCV8兼容的整数处理单元IU(Integer Unit),LEON2是5级流水线,LEON3是7级流水线。LEON包含整数硬件乘法和除法单元、双协处理器接口(FPU浮点处理单元和Co-processor协处理器),分离的指令和数据总线(Harvard结构)。LEON通过高速的AMBA-AHB总线,指令缓存和数据缓存分别和内存控制器及高速的外部接口相连传输数据。低速的AMBA-APB总线实现片上外设的接口,例如定时器、串口、网络接口等。LEON3软核可配置体系架构如图1所示。

1.2 LEON在SoC芯片开发应用中的优势

LEON软核最突出的优势是其良好的可配置性和可移植性,以及遵循GPL许可证协议的开源性。这些特性保证导航系统SoC芯片的安全性,提供良好的性能和灵活的解决方案,也决定了在LEON上进行嵌入式操作系统移植的特殊性。

1.2.1 开源性

基于GPL许可证协议,LEON非容错版本软核IP提供VHDL源代码,仅是容错版本的LEON软核需要商业授权。源代码公开是实现导航系统SoC芯片设计安全性的前提,同时也使研究者和开发者从根本上研究软核的细节从而定制满足具体应用的软核成为可能。与全部源代码开放的LEON相比,Altera的NIOS软核等其他软核仅提供若干接口,无法在更深的软核层次上进行设计和优化。

1.2.2 优异的可配置性

LEON软核通过集成一套丰富的接口和运算单元IP库,根据具体要求来达到性能、功耗和面积的平衡和优化的目的。

①软核IU可配置参数包括流水线的深度、地址和数据高速缓存(Cache)。另外,常用指令及指令序列可以根据定制的硬件进行优化;在设计或配置新运算单元后能够对指令集进行扩展。在导航系统SoC芯片设计中,通过配置LEON的整数硬件乘除法单元以实现较高的运算性能;而在其他某些使用软件乘除法,即满足要求的应用中无需配置,以降低功耗和优化芯片面积。

②外围设备接口硬件通过挂载AMBA总线来实现。LEON3的AMBA-AHP总线上能够灵活选择集成opencores的以太网控制器和GRETH以太网控制器中的任意一个。针对导航系统中常见的1553总线接口设备,在LEON中通过配置GR1553单元完成1553总线到AMBA-AHB总线的转换,为1553总线设备的集成提供了方便。

③硬件加速单元(如特定加密算法、数字信号处理单元和浮点处理单元)根据需求集成。

优异的可配置性带来了硬件设计极大的灵活性,也为嵌入式操作系统的移植带来了一定难度(特别是在扩展了指令集的情况下)。考虑到进行性能测试的完整性和灵活性,LEON3软核在本项目中的配置方案如图2所示。(详细配置参数未列出)

1.2.3良好的可移植性

LEON软核通过层次度分明的VHDL模型实现。通过VHDL中特定的配置接口,LEON核的关键参数(例如修改Cache的大小和组织方式,乘法器的生成,速度、芯片面积的调整以及容错方案的选择)都能够灵活设置和移植;而唯一使用专用技术的模型是内存宏模块。这一部分的设计采用了加上中间交互层接口的方式,因此移植的工作仅需重新编写中间交互层接口。导航系统中包括单次滤波在内的大量算法经过硬件实现后需集成在LEON中,根据LEON特定的配置接口即可实现集成和SoC系统移植。在本硬件平台的设计中,针对特定硬件开发板,通过修改顶层module文件设置以及更新引脚配置,即可完成硬件设计的移植工作。

目前,LEON在研究领域被广泛应用,特别是作为软核嵌入在可编程器件中,作为构建SoC芯片的控制和运算中心。LEON软核的容错版本也已经用在了空间站上。在本导航系统SoC芯片项目中,选择了开源且配置灵活的LEON硬件平台和Linux软件平台,并且在初期测试中表现出良好的性能。在本验证平台上,SoC系统需要以太网接口、1553总线接口、串口、通用I/O口以及调试单元,具体配置方案如图3所示。

SoC VHDL Linux 总线 嵌入式 Altera VxWorks ARM 仿真 S3C2410 MCU 相关文章:

- SoC面临挑战,智能分割顺势而起(11-07)

- 基于PL3200的CDMA扩频电力线载波通信系统设计(11-19)

- 基于SOCKS地IPv4向IPv6过渡技术(01-08)

- 基于GPRS的SOCKET通信的应用研究(01-15)

- 蓝牙技术硬件实现模式分析(01-11)

- 代理服务器------代理之间的级联(03-17)