基于TMS320VC5410的会议电话的设计与实现

时间:09-03

来源:互联网

点击:

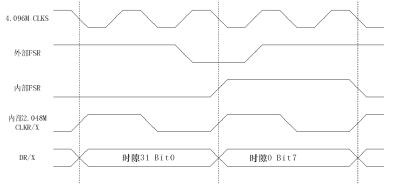

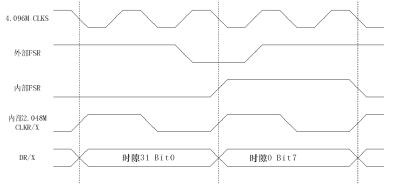

持2M和8M ST-BUS链路,这里我们以4.096M输入时钟的2.048M ST-BUS链路为例,见图4 ST-BUS链路示意图。McBSP的配置主要涉及以下四个寄存器。

图4 ST-BUS链路示意图

1.引脚控制寄存器(PCR)

CLK(R/X)M = 1, 由内部采样率发生器产生内部收发时钟CLK(R/X);FS(R/X)P = 1,帧同步低有效。

2.接收/发送控制寄存器(RCR/XCR)

(RX)PHASE = 0,单相位帧;(R/X)FRLEN1 = 11111,每帧32 字;(R/X)WDLEN1 = 0,字宽度8-bit;(R/X)COMPAND = 11,接收/发送数据使用A律压扩;(R/X)DATDLY = 0,无数据延迟。

3.采样率发生寄存器(SRGR)

CLKGDV = 1,接收/发送时钟CLK(R/X)的频率是CLKS的1/2;

GSYNC = 1,外部接收帧同步FSR同步CLKG;CLKSP = 1,CLKS的

下降沿产生采样率发生器的CLKG,进而产生CLK(R/X);CLKSM = 1,外部时钟CLKS驱动采样率发生器。

4.多通道控制寄存器(MCR1,2)

RMCM = 0,接收全部时隙使能。XMCM=00,发送全部时隙使能。

DMA的配置

DMA0"2依次分配给McBSP0"2的接收,DMA3"5依次分配给McBSP0"2的发送。具体配置如下描述:

1.DMA源地址寄存器(DMSRC)

接收DMA的DMSRC存放其对应的McBSP的DRR的地址;

发送DMA的DMSRC存放其对应的数据缓冲区的首地址。

2.DMA目的地址寄存器(DMDST)

接收DMA的DMDST存放其对应的数据缓冲区的首地址;

发送DMA的DMDST存放其对应的McBSP的DXR的地址。

3.DMA通道单元计数寄存器(DMCTR)

DMCTR的值设置了DMA数据缓冲区的大小,取为0x40,即两数据帧所包含的用户时隙数。

4.DMA 同步事件和帧计数寄存器(DMSFC)

DSYN[3:0]=0001,同步事件为McBSP0的接收事件REVT0;

DBLW = 0,单字模式,每一项是16 bit。

5.DMA传输模式控制寄存器(DMMCR)

AUTOINIT = 0,禁止自动初始化;DMA0的DINM = 1,IMOD = 1,DMA的缓冲区半满和全满时产生中断;

DMA 1"5的DIMM=0,IMOD = X,不产生DMA中断;

CTMOD = 1,DMA工作于ABU模式;

DMA0"2的SIND=000,接收DMA取为源地址不变;

DMA3"5的SIND=001,发送DMA取为源地址递增;

DMS = 01,DMA源地址空间为数据空间;

DMA0"2的DIND=000,接收DMA取为目的地址递增;

DMA3"5的DIND=001,发送DMA取为目的地址不变;

DMD = 01,DMA目的地址空间为数据空间。

性能计算

会议电话要求在每一帧所产生的DMA中断服务程序中必须完成对所有会议的与会用户的话音处理。我们以运算速度100MIPS的TMS320VC5410为例,该DSP一个指令周期的时间为10ns,因此在ST-BUS一帧125ms内可处理的指令数为125ms /10ns=12500条。由于所有用户均参加同一个会议并且话音幅度按照时隙数递增时DSP的运算处理量最大,因此我们按照上述条件来计算处理能力。假设一个会议发起时,可同时参加的用户数为x,则有如下不等式:

26x+254≤12500

其中254为中断服务程序的公共指令周期数,26为每个用户对应的指令周期数。

由上式推算出x≤471,而三条McBSP链路可同时处理3×32=96个用户(2M ST-BUS链路)或者3×128=384个用户(8M ST-BUS链路),所以会议电话的最大用户数最终由McBSP决定,即采用2M ST-BUS链路时支持96个用户,采用8M ST-BUS链路时支持384个用户。

使用汇编语言代码效率高,程序执行速度快。上述算法DMA中断服务程序是采用汇编语言来实现的,实践证明该算法是高效的。

结语

本文介绍的基于TMS320VC5410的会议电话解决方案已成功地应用于CDMA系统MSC中,

网上实际运行充分验证了该方案具有大容量和高性能价格比的特点。

参考文献:

1. TI , TMS320C54x_ DSP Functional Overview.

2. TI ,TMS320VC5410 Fixed-Point Digital Signal Processor Data Manual.

3. TI , TMS320C54x DSP Reference Set Volume 5: Enhanced Peripherals.

4. TI , TMS320C54x DSP Reference Set Volume 1: CPU and Peripherals.

5. MITEL , MT9042C Multitrunk System Synchronizer.

图4 ST-BUS链路示意图

1.引脚控制寄存器(PCR)

CLK(R/X)M = 1, 由内部采样率发生器产生内部收发时钟CLK(R/X);FS(R/X)P = 1,帧同步低有效。

2.接收/发送控制寄存器(RCR/XCR)

(RX)PHASE = 0,单相位帧;(R/X)FRLEN1 = 11111,每帧32 字;(R/X)WDLEN1 = 0,字宽度8-bit;(R/X)COMPAND = 11,接收/发送数据使用A律压扩;(R/X)DATDLY = 0,无数据延迟。

3.采样率发生寄存器(SRGR)

CLKGDV = 1,接收/发送时钟CLK(R/X)的频率是CLKS的1/2;

GSYNC = 1,外部接收帧同步FSR同步CLKG;CLKSP = 1,CLKS的

下降沿产生采样率发生器的CLKG,进而产生CLK(R/X);CLKSM = 1,外部时钟CLKS驱动采样率发生器。

4.多通道控制寄存器(MCR1,2)

RMCM = 0,接收全部时隙使能。XMCM=00,发送全部时隙使能。

DMA的配置

DMA0"2依次分配给McBSP0"2的接收,DMA3"5依次分配给McBSP0"2的发送。具体配置如下描述:

1.DMA源地址寄存器(DMSRC)

接收DMA的DMSRC存放其对应的McBSP的DRR的地址;

发送DMA的DMSRC存放其对应的数据缓冲区的首地址。

2.DMA目的地址寄存器(DMDST)

接收DMA的DMDST存放其对应的数据缓冲区的首地址;

发送DMA的DMDST存放其对应的McBSP的DXR的地址。

3.DMA通道单元计数寄存器(DMCTR)

DMCTR的值设置了DMA数据缓冲区的大小,取为0x40,即两数据帧所包含的用户时隙数。

4.DMA 同步事件和帧计数寄存器(DMSFC)

DSYN[3:0]=0001,同步事件为McBSP0的接收事件REVT0;

DBLW = 0,单字模式,每一项是16 bit。

5.DMA传输模式控制寄存器(DMMCR)

AUTOINIT = 0,禁止自动初始化;DMA0的DINM = 1,IMOD = 1,DMA的缓冲区半满和全满时产生中断;

DMA 1"5的DIMM=0,IMOD = X,不产生DMA中断;

CTMOD = 1,DMA工作于ABU模式;

DMA0"2的SIND=000,接收DMA取为源地址不变;

DMA3"5的SIND=001,发送DMA取为源地址递增;

DMS = 01,DMA源地址空间为数据空间;

DMA0"2的DIND=000,接收DMA取为目的地址递增;

DMA3"5的DIND=001,发送DMA取为目的地址不变;

DMD = 01,DMA目的地址空间为数据空间。

性能计算

会议电话要求在每一帧所产生的DMA中断服务程序中必须完成对所有会议的与会用户的话音处理。我们以运算速度100MIPS的TMS320VC5410为例,该DSP一个指令周期的时间为10ns,因此在ST-BUS一帧125ms内可处理的指令数为125ms /10ns=12500条。由于所有用户均参加同一个会议并且话音幅度按照时隙数递增时DSP的运算处理量最大,因此我们按照上述条件来计算处理能力。假设一个会议发起时,可同时参加的用户数为x,则有如下不等式:

26x+254≤12500

其中254为中断服务程序的公共指令周期数,26为每个用户对应的指令周期数。

由上式推算出x≤471,而三条McBSP链路可同时处理3×32=96个用户(2M ST-BUS链路)或者3×128=384个用户(8M ST-BUS链路),所以会议电话的最大用户数最终由McBSP决定,即采用2M ST-BUS链路时支持96个用户,采用8M ST-BUS链路时支持384个用户。

使用汇编语言代码效率高,程序执行速度快。上述算法DMA中断服务程序是采用汇编语言来实现的,实践证明该算法是高效的。

结语

本文介绍的基于TMS320VC5410的会议电话解决方案已成功地应用于CDMA系统MSC中,

网上实际运行充分验证了该方案具有大容量和高性能价格比的特点。

参考文献:

1. TI , TMS320C54x_ DSP Functional Overview.

2. TI ,TMS320VC5410 Fixed-Point Digital Signal Processor Data Manual.

3. TI , TMS320C54x DSP Reference Set Volume 5: Enhanced Peripherals.

4. TI , TMS320C54x DSP Reference Set Volume 1: CPU and Peripherals.

5. MITEL , MT9042C Multitrunk System Synchronizer.

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)