OMAP5910实时图像系统中的DMA数据传输

时间:09-03

来源:互联网

点击:

4 DMA方式数据传输优化方案

在详细分析各数据传导的数据传输速率性能的基础,本文提出了一种DMA方式的数据传输优化方案,把整帧划分成多个块,OMAP5910待处理的图像数据完全放在OMAP5910的片内数据存储器中进行处理,既减少了与外存的大量交互,又充分利用了片内的高速存储资源,在内外存之间的数据传输使用DMA在后台进行操作,大大提高OMAP5910的工作效率。

4.1 数据流程

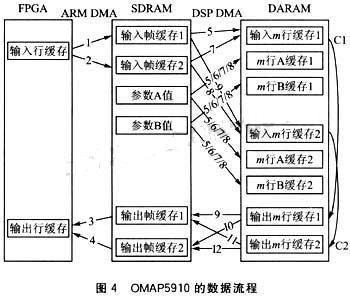

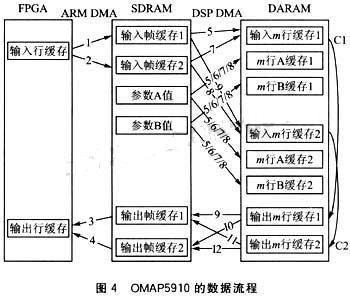

A/D采样的数据首先存放在外部缓冲中,当采集到一定的数据量后,由复杂可编程逻辑器件触发ARM DMA读取数据,依次输入两帧图像保存在SDRAM中,从外挂Flash中取得进行图像处理所需的参数A、B值保存在SDRAM中,与输出帧存以8行为块单位,触发DSP DMA将块数据从OMAP5910的外部缓存区SDRAM搬运到DSP核的双向内部缓存区DARAM,以供DSP核进行计算。有关DMA方式传输的特点,DSP核进行计算的同时,DSP DMA搬运上一块的图像数据(8行)到SDRAM,ARM核接收到输出行数据后,触发ARM DMA把数据搬移到FPGA控制外部存储区,数据流程如图4所示。

由于OMAP5910内部和外部都采用双缓冲机制,因此ARM核和DSP核处理的DMA传输上一帧数据的同时,不影响DMA进行当前帧数据的传输。这样整个系统中A/D数据的采集,DMA数据的传输及CPU数据的计算达到了高度的并行性。

4.2 操作时序

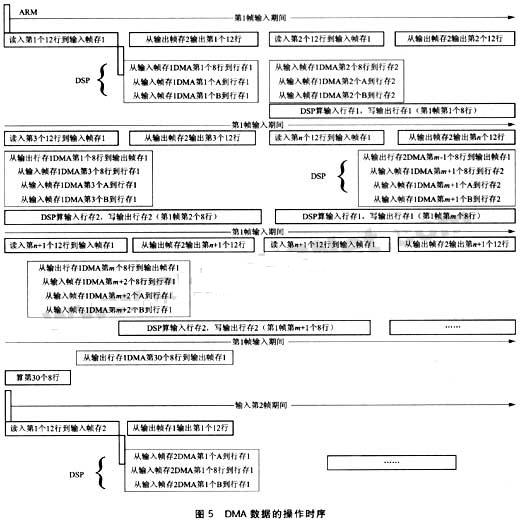

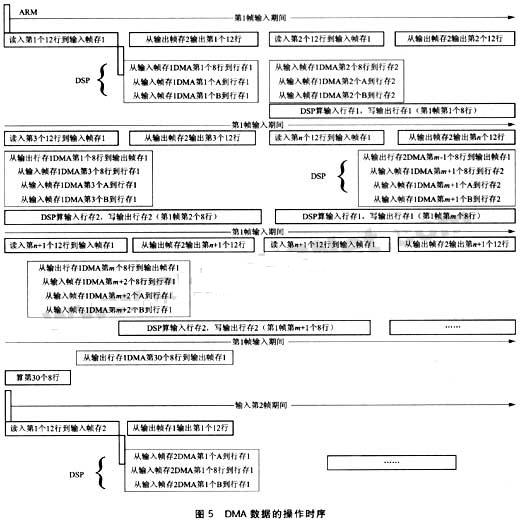

从数据传输的操作时序上,可以看出该优化方案另一个优势,将原来的几个输入过程(每个输入过程指的是输入1行像素)合并为1个输入过程(1次输入几行像素),并且将原来集中完成的输出过程分散到输入过程中间完成,进一步提高的性能。

具体配置操作为:OMAP5910中ARM DMA读过程1次输入12行数据,用20次将1帧图像输入到SDRAM中。ARM DMA的写过程在读过程中间启动。即1帧中的第1次DMA读过程结束的中断中启动行号和帧号的添加以及 DMA的写过程,这一次只写2行,在1帧中的第2次到第20次DMA读过程结束的中断中启动写过程,每次写15行,其操作时序图5所示。

具体的时间计算是:读12行数据为17.07μs×12=204.84μs,写15行数据为27.68μs×15=415.2μs,1次读写及中断的处理所需时间为204.84μS+415.2μs≈700μs,1次读写及中断的处理允许时间为68μS×12=816μs。经计算700μ<816μs,能够保证实时图像处理系统的实时性。

5 优化方案中的代码设计与实现

5.1 ARM端的主程序

ARM核主要实现OMAP5910系统的配置,与FPGA接口的数据输入/输出,与SDRAM的数据保存、帧模式的控制与转换等优化方案的功能。

5.2 DSP端的主程序

DSP核主要实现DSP DMA在I SRAM和DARAM之间

数据的输入/输出,红外图像的两点校正算法和疵点剔除等算法,以及红外图像的亮度和对比度参数的计算等功能。

5.3 调试与配置DMA通道的经验总结

1)测试DMA通道的数据传输是否正确,可编写SDRAM到SDRAM的内部DMA数据搬移测试程序来初步测试DMA通道的初始设置和数据传输是否正确。

2)测试DMA与FPGA接口数据的传输速率,示波器读取读信号或写信号的效率时,应注意查看读信号和写信号的个数是否是传输数据的个数。

3)测试DMA的外部中断,外部中断的引脚是复用引脚,应提前设置此引脚。

4)测试DMA操作的读操作和写操作的相互配合,查看输出的传输是否正确。

5)使用指定内存不同的数据测试视频图像的输出是否正确。

6)DMA中断的触发事件是上升沿有效。

7)为保证DMA传输数据的完整性,要对DMA的优先级进行设置。

结语

实时图像处理系统实现了此数据传输的优化方案,实时显示图像的速度为25帧/s,图像的视觉效果比较理想,通过灵活地控制DMA,不仅能够提高图像数据的传输效率,而且能够充分发挥OMAP5910的高速性能。

在详细分析各数据传导的数据传输速率性能的基础,本文提出了一种DMA方式的数据传输优化方案,把整帧划分成多个块,OMAP5910待处理的图像数据完全放在OMAP5910的片内数据存储器中进行处理,既减少了与外存的大量交互,又充分利用了片内的高速存储资源,在内外存之间的数据传输使用DMA在后台进行操作,大大提高OMAP5910的工作效率。

4.1 数据流程

A/D采样的数据首先存放在外部缓冲中,当采集到一定的数据量后,由复杂可编程逻辑器件触发ARM DMA读取数据,依次输入两帧图像保存在SDRAM中,从外挂Flash中取得进行图像处理所需的参数A、B值保存在SDRAM中,与输出帧存以8行为块单位,触发DSP DMA将块数据从OMAP5910的外部缓存区SDRAM搬运到DSP核的双向内部缓存区DARAM,以供DSP核进行计算。有关DMA方式传输的特点,DSP核进行计算的同时,DSP DMA搬运上一块的图像数据(8行)到SDRAM,ARM核接收到输出行数据后,触发ARM DMA把数据搬移到FPGA控制外部存储区,数据流程如图4所示。

由于OMAP5910内部和外部都采用双缓冲机制,因此ARM核和DSP核处理的DMA传输上一帧数据的同时,不影响DMA进行当前帧数据的传输。这样整个系统中A/D数据的采集,DMA数据的传输及CPU数据的计算达到了高度的并行性。

4.2 操作时序

从数据传输的操作时序上,可以看出该优化方案另一个优势,将原来的几个输入过程(每个输入过程指的是输入1行像素)合并为1个输入过程(1次输入几行像素),并且将原来集中完成的输出过程分散到输入过程中间完成,进一步提高的性能。

具体配置操作为:OMAP5910中ARM DMA读过程1次输入12行数据,用20次将1帧图像输入到SDRAM中。ARM DMA的写过程在读过程中间启动。即1帧中的第1次DMA读过程结束的中断中启动行号和帧号的添加以及 DMA的写过程,这一次只写2行,在1帧中的第2次到第20次DMA读过程结束的中断中启动写过程,每次写15行,其操作时序图5所示。

具体的时间计算是:读12行数据为17.07μs×12=204.84μs,写15行数据为27.68μs×15=415.2μs,1次读写及中断的处理所需时间为204.84μS+415.2μs≈700μs,1次读写及中断的处理允许时间为68μS×12=816μs。经计算700μ<816μs,能够保证实时图像处理系统的实时性。

5 优化方案中的代码设计与实现

5.1 ARM端的主程序

ARM核主要实现OMAP5910系统的配置,与FPGA接口的数据输入/输出,与SDRAM的数据保存、帧模式的控制与转换等优化方案的功能。

5.2 DSP端的主程序

DSP核主要实现DSP DMA在I SRAM和DARAM之间

数据的输入/输出,红外图像的两点校正算法和疵点剔除等算法,以及红外图像的亮度和对比度参数的计算等功能。

5.3 调试与配置DMA通道的经验总结

1)测试DMA通道的数据传输是否正确,可编写SDRAM到SDRAM的内部DMA数据搬移测试程序来初步测试DMA通道的初始设置和数据传输是否正确。

2)测试DMA与FPGA接口数据的传输速率,示波器读取读信号或写信号的效率时,应注意查看读信号和写信号的个数是否是传输数据的个数。

3)测试DMA的外部中断,外部中断的引脚是复用引脚,应提前设置此引脚。

4)测试DMA操作的读操作和写操作的相互配合,查看输出的传输是否正确。

5)使用指定内存不同的数据测试视频图像的输出是否正确。

6)DMA中断的触发事件是上升沿有效。

7)为保证DMA传输数据的完整性,要对DMA的优先级进行设置。

结语

实时图像处理系统实现了此数据传输的优化方案,实时显示图像的速度为25帧/s,图像的视觉效果比较理想,通过灵活地控制DMA,不仅能够提高图像数据的传输效率,而且能够充分发挥OMAP5910的高速性能。

DSP ARM 总线 传感器 FPGA 红外 示波器 相关文章:

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)