基于uPSD3254A单片机的EPP并口通信技术

时间:08-04

来源:互联网

点击:

2uPSD323X及其开发环境介绍

ST公司的uPSD3254A是带8032内核的Flash可编程系统器件,具有在线编程能力和超强的保密功能;256+32Kbytes的Flash存储器;片内8K的SDRAM;带有16位宏单元的3000门可编程逻辑电路(CPLD),可以实现EPP接口等一些不太复杂的接口和控制功能,50个I/O引脚等。

基于Windows平台的一套软件开发环境。只要点击鼠标即可完成对地址锁存器、Flash、可编程逻辑电路等外设的所有配置和写入。使用PSDsoftEXPRESS工具对uPSD3200系列器件的可编程逻辑电路的操作简单、直观。

3.基于uPSD3254A的EPP接口实现

3.1硬件接口

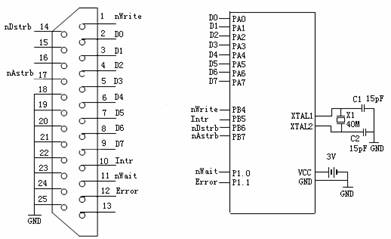

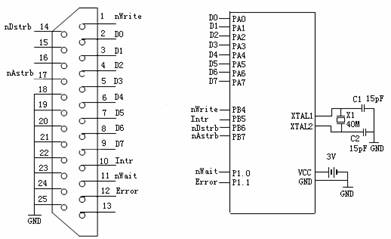

EPP增强并口的速度最高可达到500KB/s~2MB/s,这对外设的接口有很高的要求,如果外设响应太慢,系统的整体性能将大大下降。但如果采用可编程逻辑器件,使接口的响应完全由硬件来完成,系统的整体性能将大大提高。这种实现方案可以达到并口中的速度极限,而且保密性好,EPP接口(EPP1.9)外设硬件接口原理如图3所示。

图3EPP接口外设硬件接口图

在本设计中,uPSD3254A采用主动连续接收PC机并口的数据,当需要数据时,连续接收PC的数据,否则PC一直等待nWait信号有效。而当外设准备好数据上传到PC机时,PC机采用的是中断方式接收外设的数据。

3.2CPLD逻辑编程

在PSDsoftEXPRESS工具中,将PA端口(D0~D7)配置成带有时钟上升沿触发的寄存器类型(PTclockedregister)的输入宏,PB4(nWrite)、PB6(nDstrb)、PB7(nAstrb)配置成CPLD逻辑输入(logicinput)口。nDstrb信号和nAstrb信号各自取反再相与后的值作为输入宏单元的时钟。上述对PA、PB端口的配置用方程式表示如下:

EPP_D0.LD=!nDstrb&!nAstrb;

EEP_D1.LD=!nDstrb&!nAstrb;

EEP_D2.LD=!nDstrb&!nAstrb;

EEP_D3.LD=!nDstrb&!nAstrb;

EEP_D4.LD=!nDstrb&!nAstrb;

EEP_D5.LD=!nDstrb&!nAstrb;

EEP_D6.LD=!nDstrb&!nAstrb;

EEP_D7.LD=!nDstrb&!nAstrb;

nAstrb.LE=1;

nDstrb.LE=1;

数据正向传输过程:即计算机向外设单片机传输数据(即EPP数据写周期)为例,计算机首先把nWrite信号置为低,表明是写周期,同时将数据放到数据总线上,然后检测nWait信号,如果nWait为低则置低nDstrb信号。此时,!nDstrb&!nAstrb信号会出现一个上升沿,此上升沿会将PA端口的数据锁存到输入宏;当单片机检测到nDstrb为低时将nWait信号变高表示外设正忙接收数据并处理,同时读取数据总线上的数据。当计算机检测到nWait信号为高后就会将数据握手信号nDstrb变高,EPP数据写周期结束。上述EPP数据的锁存和nDstrb握手信号的产生都由硬件产生,因此数据传输速度快。整个数据传输过程可以在一个I/O周期内完成。

数据反向传输过程:单片机准备好数据需要上传到计算机时,uPSD3254A将数据放到PA端口,同时置低Intr信号线,向计算机申请一个中断,而计算机则由一个硬件驱动程序来处理并口的硬件中断。计算机首先把nWrite信号置高,表示当前为读周期,当计算机读取EPP数据口时同样会检测nWait信号。如果nWait为低,然后置低nDstrb并读取数据总线上的数据。单片机在检测到nDstrb为低时马上将nWait信号置高,PC机在nWait为高后自动将nDstrb信号置高,完成一个数据周期的读(相对PC机而言)过程。

3.3单片机数据接收程序

sbitnwait=P1^0;

sbitERROR=P1^1;

sbitnDstrb=PB&0x40;

voidparallel_rcv(unsignedlongrcv_count)//并口接收,rcv_count为接收字节数

{

unsignedlongi;

rcv_data=(unsignedchar*)&rcv_buffer;

reread_sign=1;//非错误态

while(reread_sign==1)

{

for(i=0;i<rcv_count;i++)//接收数据

{

nwait=1;//PC端反向后为低,表示外设准备好接收

while(nDstrb)//等待nDstrb为低时完成数据传输并锁存

nwait=0;//完成写周期,

rcv_data[ i]=UPSD_xreg.IMC_A;//从锁存的输入宏中读取数据

}//接收完成

ERROR=error_check(rcv_data);//检测错误,1为正确,0为错误

if(ERROR)

{

reread_sign=0;//无错则退出while循环

}

else

{

ERROR=1;//校验有错则while循环继续

}

}

该程序为单片机数据接收(即PC写数据)子程序,其中rcv_buffer为接收缓存区,error_check为对接收的数据进行校验.如果出错,则将用户自定义引脚12置低,PC机读取状态寄存器时读取到该用户自定义状态为低时,将数据重发,保证了通信的可靠性。

ST公司的uPSD3254A是带8032内核的Flash可编程系统器件,具有在线编程能力和超强的保密功能;256+32Kbytes的Flash存储器;片内8K的SDRAM;带有16位宏单元的3000门可编程逻辑电路(CPLD),可以实现EPP接口等一些不太复杂的接口和控制功能,50个I/O引脚等。

基于Windows平台的一套软件开发环境。只要点击鼠标即可完成对地址锁存器、Flash、可编程逻辑电路等外设的所有配置和写入。使用PSDsoftEXPRESS工具对uPSD3200系列器件的可编程逻辑电路的操作简单、直观。

3.基于uPSD3254A的EPP接口实现

3.1硬件接口

EPP增强并口的速度最高可达到500KB/s~2MB/s,这对外设的接口有很高的要求,如果外设响应太慢,系统的整体性能将大大下降。但如果采用可编程逻辑器件,使接口的响应完全由硬件来完成,系统的整体性能将大大提高。这种实现方案可以达到并口中的速度极限,而且保密性好,EPP接口(EPP1.9)外设硬件接口原理如图3所示。

图3EPP接口外设硬件接口图

在本设计中,uPSD3254A采用主动连续接收PC机并口的数据,当需要数据时,连续接收PC的数据,否则PC一直等待nWait信号有效。而当外设准备好数据上传到PC机时,PC机采用的是中断方式接收外设的数据。

3.2CPLD逻辑编程

在PSDsoftEXPRESS工具中,将PA端口(D0~D7)配置成带有时钟上升沿触发的寄存器类型(PTclockedregister)的输入宏,PB4(nWrite)、PB6(nDstrb)、PB7(nAstrb)配置成CPLD逻辑输入(logicinput)口。nDstrb信号和nAstrb信号各自取反再相与后的值作为输入宏单元的时钟。上述对PA、PB端口的配置用方程式表示如下:

EPP_D0.LD=!nDstrb&!nAstrb;

EEP_D1.LD=!nDstrb&!nAstrb;

EEP_D2.LD=!nDstrb&!nAstrb;

EEP_D3.LD=!nDstrb&!nAstrb;

EEP_D4.LD=!nDstrb&!nAstrb;

EEP_D5.LD=!nDstrb&!nAstrb;

EEP_D6.LD=!nDstrb&!nAstrb;

EEP_D7.LD=!nDstrb&!nAstrb;

nAstrb.LE=1;

nDstrb.LE=1;

数据正向传输过程:即计算机向外设单片机传输数据(即EPP数据写周期)为例,计算机首先把nWrite信号置为低,表明是写周期,同时将数据放到数据总线上,然后检测nWait信号,如果nWait为低则置低nDstrb信号。此时,!nDstrb&!nAstrb信号会出现一个上升沿,此上升沿会将PA端口的数据锁存到输入宏;当单片机检测到nDstrb为低时将nWait信号变高表示外设正忙接收数据并处理,同时读取数据总线上的数据。当计算机检测到nWait信号为高后就会将数据握手信号nDstrb变高,EPP数据写周期结束。上述EPP数据的锁存和nDstrb握手信号的产生都由硬件产生,因此数据传输速度快。整个数据传输过程可以在一个I/O周期内完成。

数据反向传输过程:单片机准备好数据需要上传到计算机时,uPSD3254A将数据放到PA端口,同时置低Intr信号线,向计算机申请一个中断,而计算机则由一个硬件驱动程序来处理并口的硬件中断。计算机首先把nWrite信号置高,表示当前为读周期,当计算机读取EPP数据口时同样会检测nWait信号。如果nWait为低,然后置低nDstrb并读取数据总线上的数据。单片机在检测到nDstrb为低时马上将nWait信号置高,PC机在nWait为高后自动将nDstrb信号置高,完成一个数据周期的读(相对PC机而言)过程。

3.3单片机数据接收程序

sbitnwait=P1^0;

sbitERROR=P1^1;

sbitnDstrb=PB&0x40;

voidparallel_rcv(unsignedlongrcv_count)//并口接收,rcv_count为接收字节数

{

unsignedlongi;

rcv_data=(unsignedchar*)&rcv_buffer;

reread_sign=1;//非错误态

while(reread_sign==1)

{

for(i=0;i<rcv_count;i++)//接收数据

{

nwait=1;//PC端反向后为低,表示外设准备好接收

while(nDstrb)//等待nDstrb为低时完成数据传输并锁存

nwait=0;//完成写周期,

rcv_data[ i]=UPSD_xreg.IMC_A;//从锁存的输入宏中读取数据

}//接收完成

ERROR=error_check(rcv_data);//检测错误,1为正确,0为错误

if(ERROR)

{

reread_sign=0;//无错则退出while循环

}

else

{

ERROR=1;//校验有错则while循环继续

}

}

该程序为单片机数据接收(即PC写数据)子程序,其中rcv_buffer为接收缓存区,error_check为对接收的数据进行校验.如果出错,则将用户自定义引脚12置低,PC机读取状态寄存器时读取到该用户自定义状态为低时,将数据重发,保证了通信的可靠性。

- 基于CPLD的键盘控制器设计(05-20)

- 基于DSP与CPLD的多通道数据采集系统的设计(09-22)

- DSP和CPLD的空间瞬态光辐射信号实时探测研究(01-24)

- 基于CPLD的RS-232串口通信实现(04-23)

- USB数据采集系统中DMA数据传输的实现(06-17)

- 简易USB接口卡的设计和实现(04-21)