USB2.0接口IP核的开发与设计

时间:07-31

来源:互联网

点击:

随着PC机和外围设备的发展,传统的并行接口和串行接口RS-232在易用性(即插即用) 和端口扩展等方面存在着一定的缺陷,这就使之越来越成为通信的瓶颈,因此通用串行总线(universal serial bus,USB)接口也就应运而生。1994年Compaq,IBM,Intel,Microsoft ,NEC 等公司共同提出了USB 协议规范,1996 年制定出了比较成熟的USB 1.1协议标准,最高传输速度为12Mbps。随着通信的发展,其速度明显不能满足需求,因此2000年提出了USB 2.0标准,增加了高速模式,使传输速度提高了40倍,达到了480 Mbps.凭借价格低廉、使用简单、协议灵活,接口标准化和易于端口扩展等优点,USB 接口被越来越多的外围设备所应用。

系统结构设计

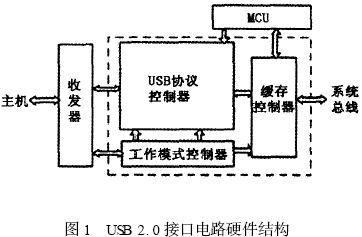

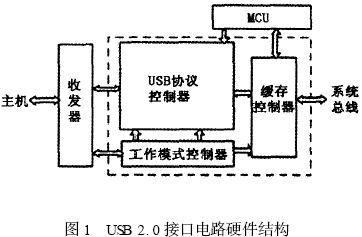

本文所设计的USB 2. 0 接口完全依据于USB 2. 0的协议,可以完成协议的处理和数据的交换。整个系统采用了MCU 固件和硬件电路相结合的设计方法,根据不同的功能以及软硬件实现的难易程度,进行了相应的模块划分。从图1 中可以看出,硬件电路分成4 个模块:收发器,USB 协议控制器,工作模式控制器和缓存控制器。这些模块将在下面具体介绍。

根据协议可知,USB 定义了四种传输类型:控制传输、批量传输、中断传输和同步传输。 其中控制传输是用于支持在设备和主机之间关于设置信息、命令信息和状态信息的传送,是必不可少的,而其他三种传输方式是真正有用的数据传输,是可选的。MCU 作为固件,其功能是协助完成USB 的控制传输,这可使设计简单,因为如果这部分功能使用硬件电路来实现将会变得非常复杂。虽然单片机的速度很慢,远远低于硬件电路,但是对于整个系统来说,控制传输只发生在主机和设备连接的开始阶段和其他传输之前,因此速度稍慢一些对整个系统的在传输速度方面的性能影响不大;但是对于其他传输方式,尤其是同步传输和批量传输来说,这样会降低USB 2. 0 高速传输的性能,是不能容忍的,所以这就决定了其不能参与USB 其他方式的数据传输。

模块设计

收发器( Transceiver)

根据UTMI(USB Transceiver Macrocell Interface) ①可知,USB 2. 0 接口的收发器主要负责时钟和数据的恢复、位填充和位剥离、NRZI(非归零反转) 的编码和解码、串并和并串的转换、同步字段和包结束码的检测和生成等功能,同时支持高速和全速传输,提供30 MHz(16 位并行数据) 时钟和60 MHz(8位并行数据) 时钟。

因为这部分是USB 2. 0 接口的模拟前端,并且是高速(480 MHz) 的串行信号处理,为了降低设计难度和减小开发周期,本文直接采用了CYPRESS 公司的CY7C 68000 芯片。

工作模式控制器( Work Mode Controller)

根据协议可知,从USB 设备连接到主机的USB 接口的过程中,USB 设备有多种可能的状态。不同的状态实现不同的功能。特别注意的是,如果USB 设备在一段特定的时间内探测不到总线活动时,必须进入挂起态,此时USB 设备保持当前的状态、地址及配置,这样可以有效地降低功耗。当检测到总线上任何非空闲信号时,设备必须被唤醒,回到原来的工作状态。

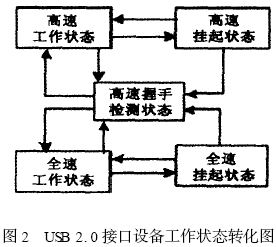

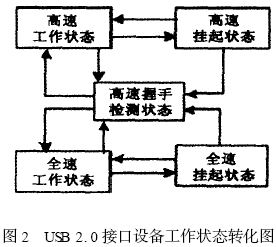

该模块主要负责USB 设备的状态转换,包括设备与主机的高速握手信号检测、主机复位信号检测、挂起和唤醒状态检测等功能。具体的状态转化过程如图2 所示。

当USB 设备刚刚和主机建立连接时,工作在全速状态,主机发送复位信号,在复位过程中,设备发送Chirp K 信号给主机,支持USB 2. 0 的主机接收到此信号后发送3 组交替的Chirp K和Chirp J信号。设备探测到此信号后,在复位信号结束后就工作在高速(480Mbps) 工作状态,否则USB 设备工作在全速(12 Mbps) 状态.当设备工作在高速模式下时,直接使用收发器提供的30MHz 的时钟;当设备工作在全速模式下时,此模块要对收发器提供的时钟进行40分频,然后再供给USB 的其他模块单元。这是因为在全速工作模式时,数据传输的串行速率是12Mbps ,仅为高速传输的1/ 40。检测总线状态,当接收到来自主机的软复位信号时,此模块负责产生复位信号给整个USB 接口电路。处在任何一种状态的设备都必须接收主机的复位信号。

检测总线状态,当USB设备发现总线上的连续空闲(高速时总线状态为SE0 ,全速时总线状态为J ) 时间超过3 ms 时,该模块产生挂起(suspend) 信号给整个USB 2. 0 接口电路,使之进入挂起状态,所有模块都不工作,此时整个电路的功耗会变得很低;处在挂起状态的设备,探测到总线上的非空闲(总线状态一般为K态) 信号时则产生唤醒信号,使整个电路在一定时间内回到全速或高速工作状态。

系统结构设计

本文所设计的USB 2. 0 接口完全依据于USB 2. 0的协议,可以完成协议的处理和数据的交换。整个系统采用了MCU 固件和硬件电路相结合的设计方法,根据不同的功能以及软硬件实现的难易程度,进行了相应的模块划分。从图1 中可以看出,硬件电路分成4 个模块:收发器,USB 协议控制器,工作模式控制器和缓存控制器。这些模块将在下面具体介绍。

根据协议可知,USB 定义了四种传输类型:控制传输、批量传输、中断传输和同步传输。 其中控制传输是用于支持在设备和主机之间关于设置信息、命令信息和状态信息的传送,是必不可少的,而其他三种传输方式是真正有用的数据传输,是可选的。MCU 作为固件,其功能是协助完成USB 的控制传输,这可使设计简单,因为如果这部分功能使用硬件电路来实现将会变得非常复杂。虽然单片机的速度很慢,远远低于硬件电路,但是对于整个系统来说,控制传输只发生在主机和设备连接的开始阶段和其他传输之前,因此速度稍慢一些对整个系统的在传输速度方面的性能影响不大;但是对于其他传输方式,尤其是同步传输和批量传输来说,这样会降低USB 2. 0 高速传输的性能,是不能容忍的,所以这就决定了其不能参与USB 其他方式的数据传输。

模块设计

收发器( Transceiver)

根据UTMI(USB Transceiver Macrocell Interface) ①可知,USB 2. 0 接口的收发器主要负责时钟和数据的恢复、位填充和位剥离、NRZI(非归零反转) 的编码和解码、串并和并串的转换、同步字段和包结束码的检测和生成等功能,同时支持高速和全速传输,提供30 MHz(16 位并行数据) 时钟和60 MHz(8位并行数据) 时钟。

因为这部分是USB 2. 0 接口的模拟前端,并且是高速(480 MHz) 的串行信号处理,为了降低设计难度和减小开发周期,本文直接采用了CYPRESS 公司的CY7C 68000 芯片。

工作模式控制器( Work Mode Controller)

根据协议可知,从USB 设备连接到主机的USB 接口的过程中,USB 设备有多种可能的状态。不同的状态实现不同的功能。特别注意的是,如果USB 设备在一段特定的时间内探测不到总线活动时,必须进入挂起态,此时USB 设备保持当前的状态、地址及配置,这样可以有效地降低功耗。当检测到总线上任何非空闲信号时,设备必须被唤醒,回到原来的工作状态。

该模块主要负责USB 设备的状态转换,包括设备与主机的高速握手信号检测、主机复位信号检测、挂起和唤醒状态检测等功能。具体的状态转化过程如图2 所示。

当USB 设备刚刚和主机建立连接时,工作在全速状态,主机发送复位信号,在复位过程中,设备发送Chirp K 信号给主机,支持USB 2. 0 的主机接收到此信号后发送3 组交替的Chirp K和Chirp J信号。设备探测到此信号后,在复位信号结束后就工作在高速(480Mbps) 工作状态,否则USB 设备工作在全速(12 Mbps) 状态.当设备工作在高速模式下时,直接使用收发器提供的30MHz 的时钟;当设备工作在全速模式下时,此模块要对收发器提供的时钟进行40分频,然后再供给USB 的其他模块单元。这是因为在全速工作模式时,数据传输的串行速率是12Mbps ,仅为高速传输的1/ 40。检测总线状态,当接收到来自主机的软复位信号时,此模块负责产生复位信号给整个USB 接口电路。处在任何一种状态的设备都必须接收主机的复位信号。

检测总线状态,当USB设备发现总线上的连续空闲(高速时总线状态为SE0 ,全速时总线状态为J ) 时间超过3 ms 时,该模块产生挂起(suspend) 信号给整个USB 2. 0 接口电路,使之进入挂起状态,所有模块都不工作,此时整个电路的功耗会变得很低;处在挂起状态的设备,探测到总线上的非空闲(总线状态一般为K态) 信号时则产生唤醒信号,使整个电路在一定时间内回到全速或高速工作状态。

总线 USB MCU 电路 收发器 单片机 模拟前端 FPGA Xilinx 电压 集成电路 相关文章:

- 热插拔和缓冲I2C总线 (04-14)

- PCIe总线何时突破Unix服务器坚冰(02-03)

- TMS320VC5402 HPI接口与PCI总线接口设计(04-12)

- 基于Nios II的I2C总线接口的实现(04-09)

- 双口RAM CY7C026在高速数据采集系统中的应用(04-12)

- 计算机在新型多电机同步系统中的应用(07-08)