USB2.0接口IP核的开发与设计

时间:07-31

来源:互联网

点击:

USB协议控制器( USB Protocol Controller)

这部分是USB 2. 0 接口电路的核心单元,处理大部分USB2. 0 的协议请求,完成数据的通信。USB总线是一种轮讯方式的总线,主机控制端口初始化所有的数据传输。每一次传输可以由多个事务构成,每一个事务最多可以传送3个数据包,分别为标记包(Token Packet) 、数据包(Data Packet) 和握手包(Handshake Packet)。传输开始时,由标志包来标志数据的传输方向,然后发送端开始发送包含有用信息的数据包或者零数据的数据包(根据传输的不同阶段而有所不同) ,接收端则要相应地发送一个握手包表明传送。

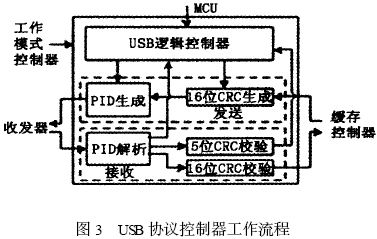

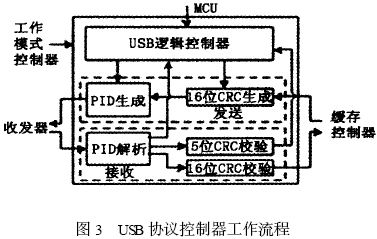

该模块的具体工作流程如图3 所示,在接收数据时,首先对包标识符( PID) 进行解析,如果是标记包(Token Packet) ,则用5 位CRC 进行校验; 如果校验错误,则忽略该信息包,校验正确后将数据送入USB 逻辑控制器,针对不同的PID 进行相应的处理。如果是数据包(Data Packet) ,则用16 位CRC 校验,然后将有效数据送入缓存控制器进行缓存,再根据传输类型,分别送入不同的模块; 在控制传输方式下, 则将数据传送给MCU ,利用MCU 完成主机对设备相应的配置工作以及完成和主机配置方面的数据交换,在其他传输方式下,则直接通过DMA 总线将数据传送到SDRAM 中存储。

如果是握手包(handshake Packet) ,则不需要CRC 校验,因为其已经包含自身反码的校验字段,直接将解析后的PID 送入USB 逻辑控制器。在发送数据时,如果是数据包,首先从缓存控制器模块得到所需数据,然后生成16 位CRC 校验码和相应数据包的PID ,传送到收发器中进行发送;如果是握手包,则直接生成相应握手包(ACK,NAK,STALL) 的PID ,然后送到收发器中发送.同时,USB 协议是通过切换从属于数据发送器和接收器的时序位来实现高速数据传输同步的。仅在接收器接受到带有正确的数据PID的无错数据包时,接收器时序位才切换;而仅在数据发送器收到合法的ACK握手PID 时,发送器时序位才切换。如果同步失败,则根据具体情况重传或丢弃该数据包,这样可以保证数据传输的正确性。

USB 逻辑控制器负责将设备的地址和端点号放入状态寄存器,只有标记包中的地址(先使用缺省地址,然后更改为主机配置的地址) 正确时才接受相应的数据包,然后根据标记包中的端点号来区分不同的传输模式:控制传输是双向端口,只有一个端点号,一般将编号为0 的端点作为控制端点以响应控制事务的输入输出;其他传输模式是单向端口,输入和输出方向都定义为不同的端点号。

缓存控制器( Buffer Controller)

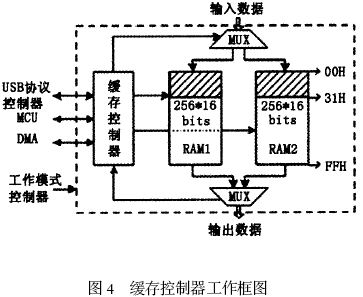

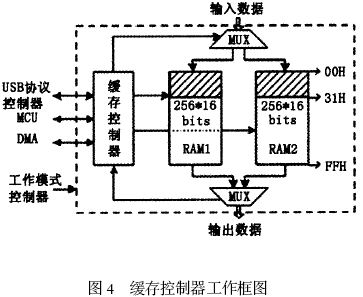

缓存控制器负责暂时存储接收或发送的数据,这些数据来自设备端的外部SDRAM或者主机。考虑到USB 2. 0 高速数据的传输要求,减小存储或读取数据的等待时间,本文采用了双缓冲区的缓存结构,硬件电路可以自动在两个缓冲区间进行转换,这样就可以同时对不同RAM分别读写,减少等待时间,提高了传输效率。不同的传输方式应该有不同的专用缓冲区(主要是区别控制传输和其他传输方式) ,但是为了节省RAM的硬件开销,本文采用了控制传输和其他传输方式缓冲区复用的结构。这种缓存结构也是整个USB 2. 0 接口硬件设计电路的特点之一。如图4 所示,在控制传输时,使用每个RAM地址为00H—31H 的存储空间,因为控制传输的最大数据包容量为32 ×16 位;在其他传输方式时,使用每个RAM地址为00H—FFH的存储空间,数据包的最大容量为256 ×16 位。由此可知,每个RAM的大小为4 种传输方式中最大数据包的容量———512 字节。

本文设计的缓存结构要求缓存控制器对不同的传输方式加以区分,相应增加了一些控制逻辑的复杂度。对于控制传输,数据是在USB 协议控制器和MCU 之间传输;对于其他传输方式,数据则是在USB 协议控制器和DMA(Direct Memory Access) 之间传输。总体来说,这种缓存结构是非常合理且有效的:节省硬件开销,而且保证传输速度。

MCU(Micro Control Unit)

MCU 采用的是51 系列的89C52 ,这部分是固件程序,负责协助完成控制传输,即USB 设备功能与设置配置的工作,利用MCU 可以降低硬件复杂度和硬件开销。在控制传输中,利用MCU 的中断程序来及时处理相应的数据交换,在批量传输时,MCU 几乎不参与工作,这是因为其工作速度较慢,不能满足大量数据传输对速度传输要求,影响传输效率。因为这部分不是硬件电路设计,所以就不再赘述了。

测试方案及测试结果

测试电路

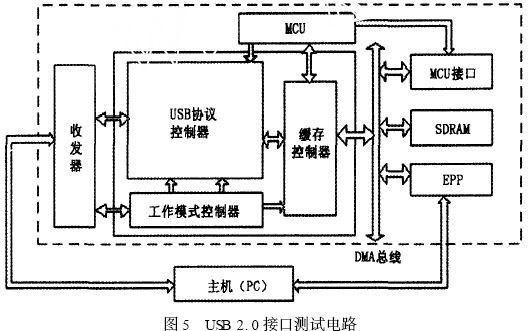

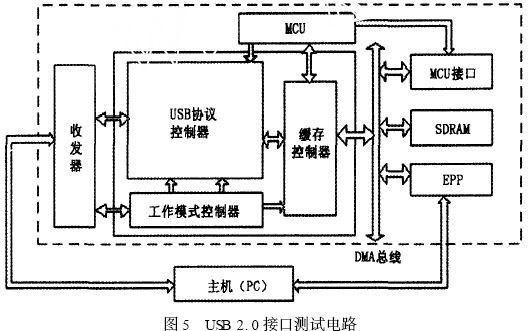

设计了一个测试电路来验证USB 2. 0 接口电路功能的正确性,如图5 所示。在原USB 2. 0 接口电路的基础上,添加了MCU 接口、DMA(Direct Memory Access) 、EPP(Enhanced Parallel Port) 和SDRAM。MCU 负责控制整个电路系统中各个模块的协调工作。这个测试电路实际上基于数码相机电路系统,USB 为该系统与主机的接口电路。

在测试USB 上传数据给主机时,主机先通过EPP 将数据下载到SDRAM中,然后缓存控制器通过DMA总线将数据从SDRAM中读出来,传送给USB 协议控制器,经过USB 协议控制器的打包处理,数据通过收发器传送给主机。通过上传到主机的数据和原数据的对比,就可以验证传送数据的正确性。

下传数据则和上传数据的验证过程类似. 或者直接通过USB 先下传然后再上传来验证数据的正确性。值得一提的是,MCU 接口、DMA ,EPP 和SDRAM这几个模块没有使用收发器芯片提供的30 MHz 时钟,而是使用了另外的系统时钟(13. 5 MHz/ 27 MHz/ 54 MHz) ,这样可以保证在USB 接口电路没有连接到主机或处在挂起状态(收发器此时也处在挂起状态,不提供时钟) 时,主机可以自由地将数据通过EPP 上传或下传到SDRAM中,而不必受USB 接口电路工作与否的限制,便于整个系统的测试工作。这样使得缓存控制器和DMA 之间的数据传输变为异步的工作模式,增加了一些处理的复杂度。图6 为USB 2. 0 接口电路FPGA 验证的验证平台。

这部分是USB 2. 0 接口电路的核心单元,处理大部分USB2. 0 的协议请求,完成数据的通信。USB总线是一种轮讯方式的总线,主机控制端口初始化所有的数据传输。每一次传输可以由多个事务构成,每一个事务最多可以传送3个数据包,分别为标记包(Token Packet) 、数据包(Data Packet) 和握手包(Handshake Packet)。传输开始时,由标志包来标志数据的传输方向,然后发送端开始发送包含有用信息的数据包或者零数据的数据包(根据传输的不同阶段而有所不同) ,接收端则要相应地发送一个握手包表明传送。

该模块的具体工作流程如图3 所示,在接收数据时,首先对包标识符( PID) 进行解析,如果是标记包(Token Packet) ,则用5 位CRC 进行校验; 如果校验错误,则忽略该信息包,校验正确后将数据送入USB 逻辑控制器,针对不同的PID 进行相应的处理。如果是数据包(Data Packet) ,则用16 位CRC 校验,然后将有效数据送入缓存控制器进行缓存,再根据传输类型,分别送入不同的模块; 在控制传输方式下, 则将数据传送给MCU ,利用MCU 完成主机对设备相应的配置工作以及完成和主机配置方面的数据交换,在其他传输方式下,则直接通过DMA 总线将数据传送到SDRAM 中存储。

如果是握手包(handshake Packet) ,则不需要CRC 校验,因为其已经包含自身反码的校验字段,直接将解析后的PID 送入USB 逻辑控制器。在发送数据时,如果是数据包,首先从缓存控制器模块得到所需数据,然后生成16 位CRC 校验码和相应数据包的PID ,传送到收发器中进行发送;如果是握手包,则直接生成相应握手包(ACK,NAK,STALL) 的PID ,然后送到收发器中发送.同时,USB 协议是通过切换从属于数据发送器和接收器的时序位来实现高速数据传输同步的。仅在接收器接受到带有正确的数据PID的无错数据包时,接收器时序位才切换;而仅在数据发送器收到合法的ACK握手PID 时,发送器时序位才切换。如果同步失败,则根据具体情况重传或丢弃该数据包,这样可以保证数据传输的正确性。

USB 逻辑控制器负责将设备的地址和端点号放入状态寄存器,只有标记包中的地址(先使用缺省地址,然后更改为主机配置的地址) 正确时才接受相应的数据包,然后根据标记包中的端点号来区分不同的传输模式:控制传输是双向端口,只有一个端点号,一般将编号为0 的端点作为控制端点以响应控制事务的输入输出;其他传输模式是单向端口,输入和输出方向都定义为不同的端点号。

缓存控制器( Buffer Controller)

缓存控制器负责暂时存储接收或发送的数据,这些数据来自设备端的外部SDRAM或者主机。考虑到USB 2. 0 高速数据的传输要求,减小存储或读取数据的等待时间,本文采用了双缓冲区的缓存结构,硬件电路可以自动在两个缓冲区间进行转换,这样就可以同时对不同RAM分别读写,减少等待时间,提高了传输效率。不同的传输方式应该有不同的专用缓冲区(主要是区别控制传输和其他传输方式) ,但是为了节省RAM的硬件开销,本文采用了控制传输和其他传输方式缓冲区复用的结构。这种缓存结构也是整个USB 2. 0 接口硬件设计电路的特点之一。如图4 所示,在控制传输时,使用每个RAM地址为00H—31H 的存储空间,因为控制传输的最大数据包容量为32 ×16 位;在其他传输方式时,使用每个RAM地址为00H—FFH的存储空间,数据包的最大容量为256 ×16 位。由此可知,每个RAM的大小为4 种传输方式中最大数据包的容量———512 字节。

本文设计的缓存结构要求缓存控制器对不同的传输方式加以区分,相应增加了一些控制逻辑的复杂度。对于控制传输,数据是在USB 协议控制器和MCU 之间传输;对于其他传输方式,数据则是在USB 协议控制器和DMA(Direct Memory Access) 之间传输。总体来说,这种缓存结构是非常合理且有效的:节省硬件开销,而且保证传输速度。

MCU(Micro Control Unit)

MCU 采用的是51 系列的89C52 ,这部分是固件程序,负责协助完成控制传输,即USB 设备功能与设置配置的工作,利用MCU 可以降低硬件复杂度和硬件开销。在控制传输中,利用MCU 的中断程序来及时处理相应的数据交换,在批量传输时,MCU 几乎不参与工作,这是因为其工作速度较慢,不能满足大量数据传输对速度传输要求,影响传输效率。因为这部分不是硬件电路设计,所以就不再赘述了。

测试方案及测试结果

测试电路

设计了一个测试电路来验证USB 2. 0 接口电路功能的正确性,如图5 所示。在原USB 2. 0 接口电路的基础上,添加了MCU 接口、DMA(Direct Memory Access) 、EPP(Enhanced Parallel Port) 和SDRAM。MCU 负责控制整个电路系统中各个模块的协调工作。这个测试电路实际上基于数码相机电路系统,USB 为该系统与主机的接口电路。

在测试USB 上传数据给主机时,主机先通过EPP 将数据下载到SDRAM中,然后缓存控制器通过DMA总线将数据从SDRAM中读出来,传送给USB 协议控制器,经过USB 协议控制器的打包处理,数据通过收发器传送给主机。通过上传到主机的数据和原数据的对比,就可以验证传送数据的正确性。

下传数据则和上传数据的验证过程类似. 或者直接通过USB 先下传然后再上传来验证数据的正确性。值得一提的是,MCU 接口、DMA ,EPP 和SDRAM这几个模块没有使用收发器芯片提供的30 MHz 时钟,而是使用了另外的系统时钟(13. 5 MHz/ 27 MHz/ 54 MHz) ,这样可以保证在USB 接口电路没有连接到主机或处在挂起状态(收发器此时也处在挂起状态,不提供时钟) 时,主机可以自由地将数据通过EPP 上传或下传到SDRAM中,而不必受USB 接口电路工作与否的限制,便于整个系统的测试工作。这样使得缓存控制器和DMA 之间的数据传输变为异步的工作模式,增加了一些处理的复杂度。图6 为USB 2. 0 接口电路FPGA 验证的验证平台。

总线 USB MCU 电路 收发器 单片机 模拟前端 FPGA Xilinx 电压 集成电路 相关文章:

- 热插拔和缓冲I2C总线 (04-14)

- PCIe总线何时突破Unix服务器坚冰(02-03)

- TMS320VC5402 HPI接口与PCI总线接口设计(04-12)

- 基于Nios II的I2C总线接口的实现(04-09)

- 双口RAM CY7C026在高速数据采集系统中的应用(04-12)

- 计算机在新型多电机同步系统中的应用(07-08)