一种基于ISS的软硬件协同验证环境

时间:07-29

来源:互联网

点击:

4 协同验证环境的实现

4.1 基本构架

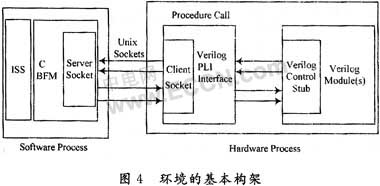

整个环境的基本构架如图4所示,左右两个框分别表示软件仿真进程和硬件仿真进程,他们之间通过UnixSockets交换信息,Verilog PLI是他们交互的接口。下面对环境的各个部分进行介绍。

在软件环境中,指令级模拟器(ISS)是一种仿真CPU行为的程序,他在主机上运行,可以仿真软件程序的可执行镜像。把SOC软件编译成针对SOC硬件嵌入式核的目标代码后,即可在指令级模拟器上仿真。C的总线模型(C BFM)用来实现指令级到周期级的转换,并实现总线接口功能,与硬件环境相连接,同时还包含了Unix Sockets的服务程序。

硬件环境包含2部分。一部分是Verilog PLI Inter-face。他是软件和硬件交互的接口,一方面通过UnixSockets的客户程序与软件环境交互信息;一方面通过一些任务函数,根据Sockets传递过来的信息,向硬件发出请求或者应答信号。另一部分是待验证的硬件模型,用Ver-ilog描述,他的外围是一段控制程序(verilog controlstub),在仿真的每一个时刻调用PLI中的函数,通过端口与Verilog PLI Interface交互信息。

4.2 功能实现

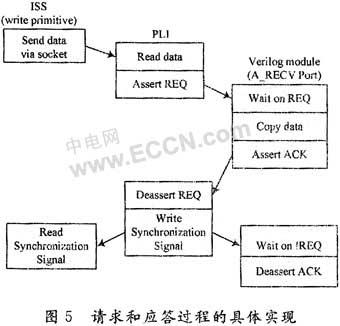

图5给出了软硬件环境通过A_RECV端口实现通信的例子。

当软件需要向硬件写入一个数据时,首先通过Socket将数据发送给PLI;PLI接收数据,同时拉高请求线,向硬件发出请求;硬件模型得到清求后,通过Verilog ControlStub接收数据,传递给内部寄存器,并拉高应答线,向PLI发出应答。PLI得到应答后拉低请求线,同时发出同步信号给Socket,硬件模型得到拉低的请求后,拉低应答线,一次传输结束。当软件需要进行下一次写操作时,首先需要通过Socket读取同步信号,有同步信号时即可开始下一次操作。其他的端口握手过程与此类似。

4.3 协同模拟同步

指令集模拟器以指令为单位进行模拟,时钟每次推进一个指令周期,指令周期长度则随指令的不同而不同。硬件模拟器通常采用事件驱动模拟算法,他以事件为调度对象,硬件模拟器按照事件发生的时间进度推进时钟,时间单位一般由用户的设计指定,例如纳秒,微秒等。因此必须采用一定的机制对二者进行同步,并且他们之间能否同步将直接影响到协同模拟的正确性。指令集模拟器和硬件模拟器之间通常采用Lock-step方式进行同步。采用该同步方式必须首先确定同步点,保证在两个同步点之间的时间间隔内不发生软硬件交互事件。如前文所述,Verilog PLIInterface是软硬件模拟器之间的信息交换界面,所以同步点会因为交互信息的不问而不同。而硬件模拟器是以事件发生的时间顺序推进时钟,要保证其时钟不会越过同步点,就必须引入同步信号,即时间为同步点的信号,硬件模拟器完成一个事件后,需要向Verilog PLI Interface发回一个同步信息,说明硬件模拟器的时钟己推进到同步点。

5 结 语

设计验证是SOC设计的关键技术之一,贯穿整个SOC技术,随着SOC技术的发展,软硬件协同验证技术得到了更多的关注和重视。与过去把整个环境当作单一的一个进程处理的方法不同,本环境将软硬件仿真的过程分离开来,使用Unix Sockets来实现软硬件之间的通信,更接近实际情况。同时,由于两个仿真过程并行执行,仿真速度更快,效率更高。在该环境中,软件用编程语言来编写,硬件用硬件描述语言来建模,符合一般软硬件工程师的习惯,较早的进行软硬件的整合。在此环境中,软硬件之间通信的吞吐量是影响仿真速度的瓶颈,下一步作者将针对协同模拟同步及优化进行研究。

仿真 总线 FPGA 嵌入式 Verilog 硬件工程师 相关文章:

- 一种基于OPNET的小型网络仿真及分析(04-08)

- APOX软件在A+B频段无线网络规划中的应用(06-26)

- 基于GUI的跳频OFDM系统仿真设计(03-03)

- 基于CPLD的RS-232串口通信实现(04-23)

- 2.5 Gbps收发器中1∶2解复用电路的设计(09-17)

- 填补网络 SoC 设计前端与后端验证的差距(09-19)