一种交织器和解交织器的FPGA电路实现

时间:06-28

来源:互联网

点击:

电路特点分析

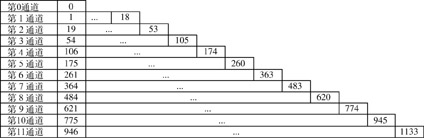

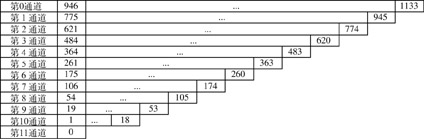

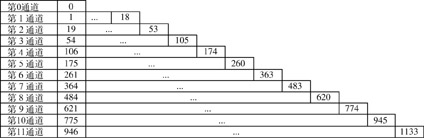

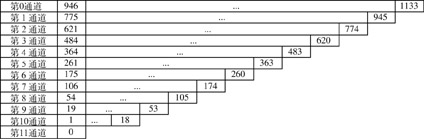

仍然以I=12,M=17的交织器和解交织器为例。

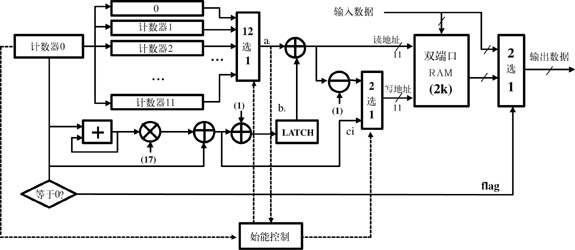

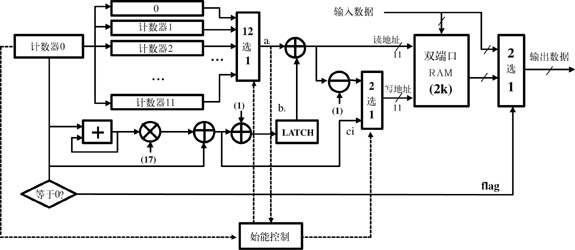

图4:交织器和解交织器

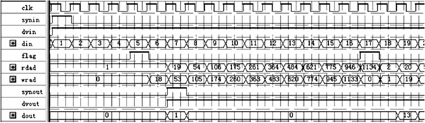

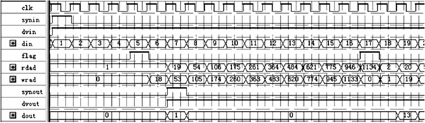

图5:波形仿真图

本设计采用单倍实现所用的存储单元总数Nram=[(I-1)×M/2+1]×I=1134,相应要用到地址总线的位数为Nad=ceil[log2(Nram)]=11。也就是说,要用到2k的双端口RAM,读写地址线各11根。

而采用一般的双倍实现占用的存储单元总数Nram=[(I-1)×M+1]×I=2256,相应要用到地址总线位数Nad=ceil[log2(Nram)]=12。如果采用双倍实现,要用到4k的双端口RAM,读写地址线各12根。

理论上最简存储单元的占用量为Nram=[(I-1)×M×I/2 =1122,地址总线位数为Nad=ceil[log2(Nram)]=11,所以单倍实现的优点是显而易见的,其占用存储单元数为双倍实现的一半,读写地址线各少1根,接近于最简占用量。只要交织深度I不是很深,该设计方法使用的逻辑单元门数并不多,而且可以节约大量的存储单元,效果是显而易见的。

仍然以I=12,M=17的交织器和解交织器为例。

图4:交织器和解交织器

图5:波形仿真图

本设计采用单倍实现所用的存储单元总数Nram=[(I-1)×M/2+1]×I=1134,相应要用到地址总线的位数为Nad=ceil[log2(Nram)]=11。也就是说,要用到2k的双端口RAM,读写地址线各11根。

而采用一般的双倍实现占用的存储单元总数Nram=[(I-1)×M+1]×I=2256,相应要用到地址总线位数Nad=ceil[log2(Nram)]=12。如果采用双倍实现,要用到4k的双端口RAM,读写地址线各12根。

理论上最简存储单元的占用量为Nram=[(I-1)×M×I/2 =1122,地址总线位数为Nad=ceil[log2(Nram)]=11,所以单倍实现的优点是显而易见的,其占用存储单元数为双倍实现的一半,读写地址线各少1根,接近于最简占用量。只要交织深度I不是很深,该设计方法使用的逻辑单元门数并不多,而且可以节约大量的存储单元,效果是显而易见的。

Altera Quartus 仿真 FPGA 电路 总线 相关文章:

- G.723.1在DSP数字对讲机基带系统中的应用(01-14)

- 基于FPGA的无线同播频率校准装置的设计(03-11)

- 利用串行RapidIO交换机设计模块化无线基础系统(03-12)

- 基于CAN核的四冗余通信板设计与仿真(03-18)

- 基于FPGA实现DSP与Rapid IO网络互联(04-13)

- 基于FPGA的嵌入式系统USB接口设计(04-20)