利用串行RapidIO交换机设计模块化无线基础系统

时间:03-12

来源:互联网

点击:

基带架构优势

正如前面提到的,图1中描述的架构具有极高的灵活性和可扩展性,在这种架构中,设计者在分配各种处理端点之间的主要应用任务功能划分方面有广泛的灵活性。由于架构已经不再与运算密切相关,流量和处理能力可在运行时间内从一个器件转移到另外一个器件。该架构也具有可扩展性,有助于满足具体应用在性能和成本方面所需的端点数量增减。例如,可以轻易改变DRP和DSP的数量,以实现相同的设计可以匹配到从微微蜂窝到大型基站的设计要求。

包括IDT公司在内的多家供应商都可提供交换机解决方案执行这种基于结构(fabric- based)的架构。最近推出的IDT PPS为该应用带来了数据分配和DSP加速的组合方案。PPS不仅可作为交换机连接各种串行RapidIO端点,也可为集群(cluster)中DSP重复格式化需求提供数据处理能力,这种格式化需求可占用关键的带宽。

不同的器件和算法以不同的采样和符号长度进行工作。例如,CPRI可把采样长度定义为8至40位。处理器一般以8、16或32位的采样长度工作。不同的算法要求采样具有特定的顺序(I-Q一起或分开、过采样与常规采样一起或分开,以及其它组合),因此,这些数据格式化操作需要在CRP和DSP中执行。根据选择的DSP和CRP的不同,系统设计者应该意识到这些操作可以有多种组合,处理器可能需要花很多周期进行这些操作。PPS可把这些操作集中到交换机中,以减少处理器负担。通过把加法/同步模块与交换机集成到一起,对齐多个CRP中的信息包,累加到下行链路中,以带来更多的价值。普通的串行 RapidIO交换机一般需要累加器(summer)和同步器件(synchronizer)的支持,这增加了设计的元件数量和复杂性。

增强的交换功能使基带架构受益

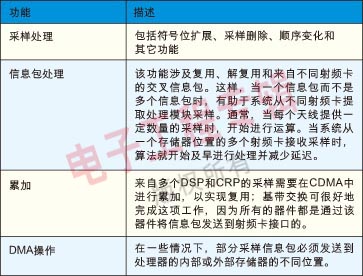

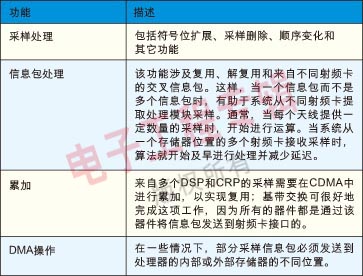

PPS不仅是一个协议交换机,而且是专为支持基带应用中的FPGA或DSP集群而优化的,它为基带卡集成了大量独一无二的其它功能。因此,如果交换机架构允许的话,PPS可更有效地使系统在基带交换机中执行表1中所示的功能。

表1:系统在基带交换机中执行的功能。

为了评估把这些功能集成到交换机操作的好处,首先必须确定通过一个如基带交换机的集中器件,与如DSP的处理器,或者如FPGA或ASIC的端点相比,执行上述操作可节省百分之多少的处理周期。

假设所有的码片率和符号率处理功能都可以在一个或更多1GHz的DSP中实现,那么每个功能都是一个WCDMA功能的实例。每个卸载数据都包括前一个功能,例如27.5%的采样顺序变化就包括采样符号扩展。假设每个采样上的每次功能执行有1~2个周期的延迟,12个天线通道,两倍过采样率的 3.84Mcps(百万样片每秒)WCDMA系统。

一次采样的每个功能延迟1~2个周期是比较乐观的情况,假设每个采样都是在一级存储器或寄存器中进行存取。实际的情况是,采样是存储在更大的二级存储器中,第一次采样的存储器的存取延迟增加到9~10个周期(1GHz DSP),而且每个后来的采样需要两个周期。在最差的情况下,糟糕的软件存储器管理可以迫使每次采样花8~9个周期来读取二级存储器。在极端情况下,由于所有资源都被用于数据格式化了,DSP可能无法用于其它目的。

本文小结

对于设计者来说,构建下一代基带卡和基于连接了多个DSP、FPGA和ASIC的串行RapidIO接口的结构型架构具有许多优势。由于采用现成的元件,这种架构可降低开发和部署成本,同时可确保满足广泛应用和市场条件所需的灵活性和可扩展性。它可以简化设计,并可最大限度地降低增加其它功能和系统升级的成本,还可以大大简化软件开发而不增加延迟。通过在信息包和采样处理等集中的串行RapidIO交换机中采用并行功能,设计者可提高处理效率,并可在降低成本的同时增加性能。

作者:IDT公司高级系统架构师Bertan Tezcan,流量控制管理部高级产品经理Bill Beane

来源:电子工程专辑 2007-3

正如前面提到的,图1中描述的架构具有极高的灵活性和可扩展性,在这种架构中,设计者在分配各种处理端点之间的主要应用任务功能划分方面有广泛的灵活性。由于架构已经不再与运算密切相关,流量和处理能力可在运行时间内从一个器件转移到另外一个器件。该架构也具有可扩展性,有助于满足具体应用在性能和成本方面所需的端点数量增减。例如,可以轻易改变DRP和DSP的数量,以实现相同的设计可以匹配到从微微蜂窝到大型基站的设计要求。

包括IDT公司在内的多家供应商都可提供交换机解决方案执行这种基于结构(fabric- based)的架构。最近推出的IDT PPS为该应用带来了数据分配和DSP加速的组合方案。PPS不仅可作为交换机连接各种串行RapidIO端点,也可为集群(cluster)中DSP重复格式化需求提供数据处理能力,这种格式化需求可占用关键的带宽。

不同的器件和算法以不同的采样和符号长度进行工作。例如,CPRI可把采样长度定义为8至40位。处理器一般以8、16或32位的采样长度工作。不同的算法要求采样具有特定的顺序(I-Q一起或分开、过采样与常规采样一起或分开,以及其它组合),因此,这些数据格式化操作需要在CRP和DSP中执行。根据选择的DSP和CRP的不同,系统设计者应该意识到这些操作可以有多种组合,处理器可能需要花很多周期进行这些操作。PPS可把这些操作集中到交换机中,以减少处理器负担。通过把加法/同步模块与交换机集成到一起,对齐多个CRP中的信息包,累加到下行链路中,以带来更多的价值。普通的串行 RapidIO交换机一般需要累加器(summer)和同步器件(synchronizer)的支持,这增加了设计的元件数量和复杂性。

增强的交换功能使基带架构受益

PPS不仅是一个协议交换机,而且是专为支持基带应用中的FPGA或DSP集群而优化的,它为基带卡集成了大量独一无二的其它功能。因此,如果交换机架构允许的话,PPS可更有效地使系统在基带交换机中执行表1中所示的功能。

表1:系统在基带交换机中执行的功能。

为了评估把这些功能集成到交换机操作的好处,首先必须确定通过一个如基带交换机的集中器件,与如DSP的处理器,或者如FPGA或ASIC的端点相比,执行上述操作可节省百分之多少的处理周期。

假设所有的码片率和符号率处理功能都可以在一个或更多1GHz的DSP中实现,那么每个功能都是一个WCDMA功能的实例。每个卸载数据都包括前一个功能,例如27.5%的采样顺序变化就包括采样符号扩展。假设每个采样上的每次功能执行有1~2个周期的延迟,12个天线通道,两倍过采样率的 3.84Mcps(百万样片每秒)WCDMA系统。

一次采样的每个功能延迟1~2个周期是比较乐观的情况,假设每个采样都是在一级存储器或寄存器中进行存取。实际的情况是,采样是存储在更大的二级存储器中,第一次采样的存储器的存取延迟增加到9~10个周期(1GHz DSP),而且每个后来的采样需要两个周期。在最差的情况下,糟糕的软件存储器管理可以迫使每次采样花8~9个周期来读取二级存储器。在极端情况下,由于所有资源都被用于数据格式化了,DSP可能无法用于其它目的。

本文小结

对于设计者来说,构建下一代基带卡和基于连接了多个DSP、FPGA和ASIC的串行RapidIO接口的结构型架构具有许多优势。由于采用现成的元件,这种架构可降低开发和部署成本,同时可确保满足广泛应用和市场条件所需的灵活性和可扩展性。它可以简化设计,并可最大限度地降低增加其它功能和系统升级的成本,还可以大大简化软件开发而不增加延迟。通过在信息包和采样处理等集中的串行RapidIO交换机中采用并行功能,设计者可提高处理效率,并可在降低成本的同时增加性能。

作者:IDT公司高级系统架构师Bertan Tezcan,流量控制管理部高级产品经理Bill Beane

来源:电子工程专辑 2007-3

IDT DSP FPGA 嵌入式 Altera 飞思卡尔 赛灵思 集成电路 无线电 射频 电子 相关文章:

- 华硕电脑高端母板采用 IDT PCI Express 交换解决方案(10-17)

- IDT推出业界每秒10亿次最高搜索性能的20M比特密度搜索加速器(02-26)

- IDT推出每秒10亿次搜索性能的20Mb密度搜索加速器(03-13)

- IDT 推出业界首款可扩展3G 基站优化预处理解决方案(05-21)

- IDT 推出为超级PC音频体验优化的、低功耗、高清音频编解码器(06-12)

- IDT与RMI 强强联手 推出下一代网络解决方案(08-18)