通讯系统中超高效率降压型变换器的设计考虑

时间:12-22

来源:互联网

点击:

适用于上管的SGT新型功率MOSFET

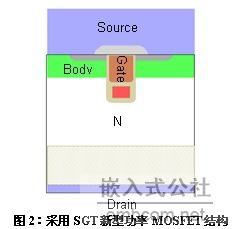

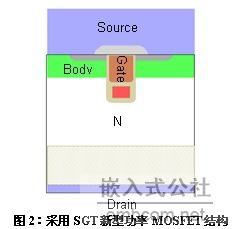

通常,对于MOSFET,导通电阻Rds(on)和漏极栅极的米勒电容是一个相互矛盾的参数,必须采用新技术才能解决这个问题。对于同样面积的晶圆,如果要减小米勒电容,则必须减小漏极和栅极相对接触面积。最为直观的方法是对栅极采用一定的屏蔽技术,减小漏极和栅极的相对电容。图2就是采用AOS的专利技术SGT所制作的具有极低漏极栅极米勒电容的新型功率MOSFET。

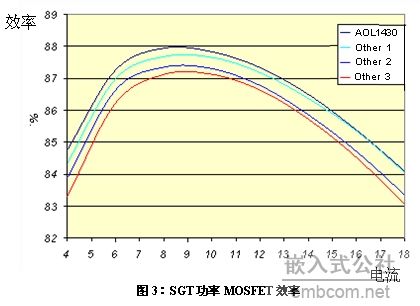

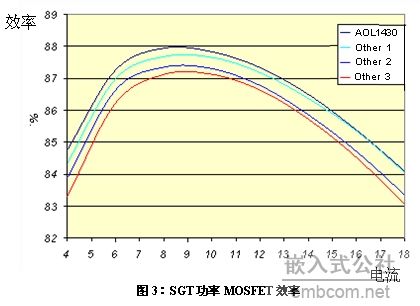

在图2中,除了栅极结构,其它部分是标准的采用Trench工艺的MOSFET。栅极被分割成上下两个部分,下部分用一些特殊的材料屏蔽起来。下部分在内部和上部分的栅极相连,而下部分栅极的屏蔽层被连接到源极,以减小漏极栅极米勒电容。采用这种技术设计的MOSFET,例如AOL1464,其Vds为 30V,在Vgs等于10V条件下,Rds(on)为6.2mΩ,而其Crss只有20pF。这样大大减小了开关过程中米勒平台的持续时间,降低了开关损耗。AOL1430的Vds为30V,在Vgs等于10V条件下,Rds(on)为2.5mΩ,而其Crss为50pF。图3给出了下管采用AOS的 AOL1428、上管采用AOL1430的设计,和采用其他厂家目前Crss最低器件的设计的效率曲线。由此可见,上管采用AOL1430的设计具有非常高的效率。请注意,这里的输入电压为12V,输出电压为1.7V,开关频率为300kHz。

适用于下管的超低Rds(on)功率MOSFET

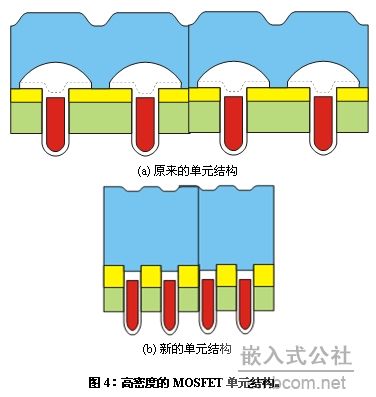

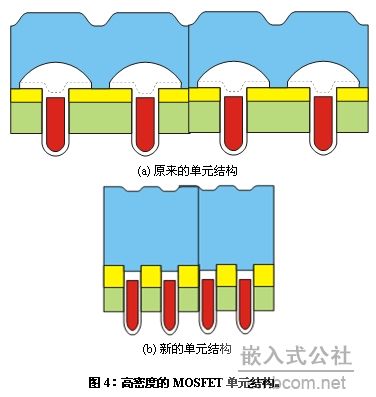

下管主要是导通损耗,因此要尽量使用导通电阻Rds(on)低的功率MOSFET。目前主要通过改进工艺和使用新的材料,在同样面积的晶圆上降低每个单元的电阻,同时尽可能设计出更多的单元,提高单元的密度,以形成低的导通电阻Rds(on)。

(a) 原来的单元结构

(b) 新的单元结构

在图4中,每个MOSFET单元在相同额定的Vds电压条件下,导通电阻都相同,具有更高的单元密度,在水平和垂直两个方向都尽可能缩小了尺寸。AOS的 AON 6702采用DFN的封装,Vds为30V,在Vgs等于10V条件下,Rds(on)为1.9mΩ,同时内部集成了具有优异开头特性的肖特基二极管。

本文小结

同步降压型变换器的上管同时具有开关损耗和导通损耗,在输入输出压差大的应用中,以开关损耗为主。导通损耗与MOSFET的导通电阻Rds(on)成正比,开关损耗与漏极栅极米勒电容相关。

采用SGT技术功率MOSFET具有超低的漏极栅极米勒电容,减小了开关过程中米勒平台的持续的时间,降低了开关损耗。

同步降压型变换器的下管只有导通损耗,开关损耗几乎为0。建议选取Rds(on)尽量小的MOSFET。采用新工艺和新材料可以提高晶圆上单元的晶胞密度,降低单元的电阻密度。

作者:刘松,丁宇

万代半导体元件(上海)有限公司

作者介绍:刘松,男,硕士,36岁,万代半导体元件有限公司应用中心经理,曾任凌特有限公司上海办事处应用工程师,ST意法半导体上海有限公司高级电源系统工程师,现主要从事开关电源系统及模拟电路的应用研究和开发工作。发表论文30多篇,获发明专利一项及广东省科技进步二等奖一项。

地址:上海市松江区松蒸公路888号松江出口加工区B区茸康路109弄91号8/9栋 邮编201614

通常,对于MOSFET,导通电阻Rds(on)和漏极栅极的米勒电容是一个相互矛盾的参数,必须采用新技术才能解决这个问题。对于同样面积的晶圆,如果要减小米勒电容,则必须减小漏极和栅极相对接触面积。最为直观的方法是对栅极采用一定的屏蔽技术,减小漏极和栅极的相对电容。图2就是采用AOS的专利技术SGT所制作的具有极低漏极栅极米勒电容的新型功率MOSFET。

在图2中,除了栅极结构,其它部分是标准的采用Trench工艺的MOSFET。栅极被分割成上下两个部分,下部分用一些特殊的材料屏蔽起来。下部分在内部和上部分的栅极相连,而下部分栅极的屏蔽层被连接到源极,以减小漏极栅极米勒电容。采用这种技术设计的MOSFET,例如AOL1464,其Vds为 30V,在Vgs等于10V条件下,Rds(on)为6.2mΩ,而其Crss只有20pF。这样大大减小了开关过程中米勒平台的持续时间,降低了开关损耗。AOL1430的Vds为30V,在Vgs等于10V条件下,Rds(on)为2.5mΩ,而其Crss为50pF。图3给出了下管采用AOS的 AOL1428、上管采用AOL1430的设计,和采用其他厂家目前Crss最低器件的设计的效率曲线。由此可见,上管采用AOL1430的设计具有非常高的效率。请注意,这里的输入电压为12V,输出电压为1.7V,开关频率为300kHz。

适用于下管的超低Rds(on)功率MOSFET

下管主要是导通损耗,因此要尽量使用导通电阻Rds(on)低的功率MOSFET。目前主要通过改进工艺和使用新的材料,在同样面积的晶圆上降低每个单元的电阻,同时尽可能设计出更多的单元,提高单元的密度,以形成低的导通电阻Rds(on)。

(a) 原来的单元结构

(b) 新的单元结构

在图4中,每个MOSFET单元在相同额定的Vds电压条件下,导通电阻都相同,具有更高的单元密度,在水平和垂直两个方向都尽可能缩小了尺寸。AOS的 AON 6702采用DFN的封装,Vds为30V,在Vgs等于10V条件下,Rds(on)为1.9mΩ,同时内部集成了具有优异开头特性的肖特基二极管。

本文小结

同步降压型变换器的上管同时具有开关损耗和导通损耗,在输入输出压差大的应用中,以开关损耗为主。导通损耗与MOSFET的导通电阻Rds(on)成正比,开关损耗与漏极栅极米勒电容相关。

采用SGT技术功率MOSFET具有超低的漏极栅极米勒电容,减小了开关过程中米勒平台的持续的时间,降低了开关损耗。

同步降压型变换器的下管只有导通损耗,开关损耗几乎为0。建议选取Rds(on)尽量小的MOSFET。采用新工艺和新材料可以提高晶圆上单元的晶胞密度,降低单元的电阻密度。

作者:刘松,丁宇

万代半导体元件(上海)有限公司

作者介绍:刘松,男,硕士,36岁,万代半导体元件有限公司应用中心经理,曾任凌特有限公司上海办事处应用工程师,ST意法半导体上海有限公司高级电源系统工程师,现主要从事开关电源系统及模拟电路的应用研究和开发工作。发表论文30多篇,获发明专利一项及广东省科技进步二等奖一项。

地址:上海市松江区松蒸公路888号松江出口加工区B区茸康路109弄91号8/9栋 邮编201614

电路 电流 电源模块 电压 MOSFET 电阻 电容 电感 二极管 半导体 意法半导体 开关电源 模拟电路 相关文章:

- 浅谈E1线路维护技术与应用(01-12)

- R4网络接口和电路域容灾技术(01-05)

- 移动通信网引入IMS的相关探讨(02-21)

- 未来接入网的结构与演进(01-26)

- 电子熔丝在计算机应用中的优势(06-08)

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)